采用硅通孔(TSV)的多芯片堆叠结构高速互连SI分析

本节建立了GSG结构TSV 3D模型的传输线等效电路,通过修改等效电路中相应元件的参数,可反映TSV模型参数的变化。下面将对堆叠芯片结构的互连进行了仿真,还通过得到的S参数进行了时域仿真,并建立了TSV的传输线等效电路,以验证通孔几何尺寸变化的影响。图8c展示了TSV间距=30μm、氧化层厚度=0.2μm时,不同TSV直径对应的S21。上面对包含多条TSV-RDL-凸点路径的3D堆叠芯片互连进行了

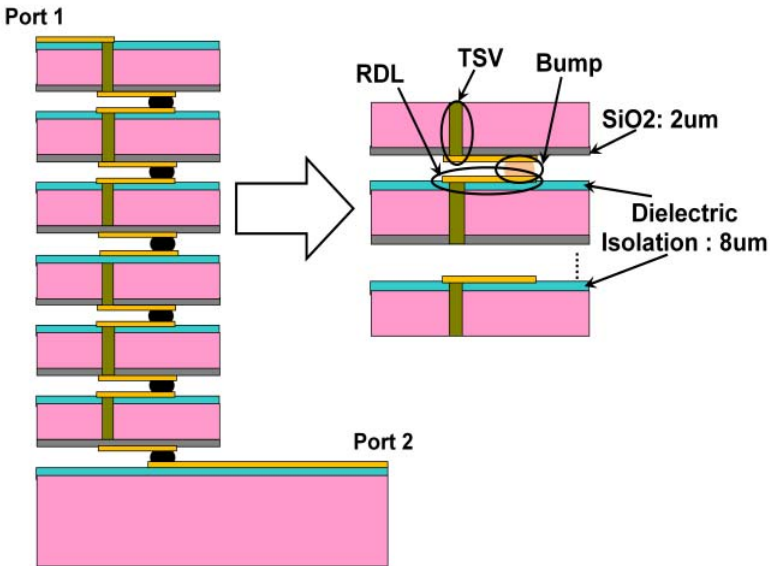

3D硅集成电路堆叠或采用硅/有机中介层的技术,仍是实现更小、更快、更廉价电子系统的主要趋势。三维系统级封装(3D SiP)是芯片堆叠的典型方案,它利用第三维度进行芯片布局,大幅减少了对封装衬底面积的需求。顶部到底部的垂直互连通过引入TSV以及额外的RDL和凸点实现。与传统2D封装或仅引线键合封装相比,这大幅缩短了互连路径长度并减少了所需面积。

尽管3D封装技术的发展旨在缩短系统总互连长度,但随着器件频率不断提高,互连的建模与仿真对于预测寄生参数的影响至关重要。下面将对堆叠芯片结构的互连进行了仿真,还通过得到的S参数进行了时域仿真,并建立了TSV的传输线等效电路,以验证通孔几何尺寸变化的影响。

堆叠芯片建模

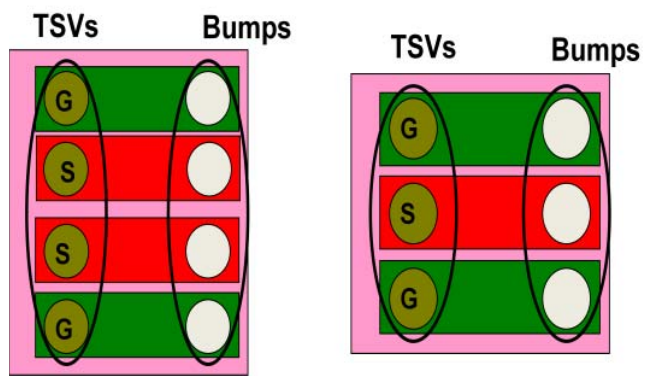

通常,整个堆叠结构由相同的存储芯片组成,底部放置一片控制器芯片,构成完整的工作系统。图1展示了最多包含6片芯片的堆叠结构模型。每片芯片上的多个TSV-RDL-凸点连接实现了顶部到底部的导通。TSV与凸点之间通常需要设置偏移量,因为TSV直接位于凸点上方会引发可靠性问题。该模型完整的互连路径采用GSSG和GSG两种配置,以分别仿真插入损耗和串扰。

图1a 带TSV和凸点偏移的6片芯片堆叠侧视图

图1b TSV与凸点的GSSG和GSG配置俯视图

表1 六芯片堆叠的建模尺寸

插入损耗与串扰

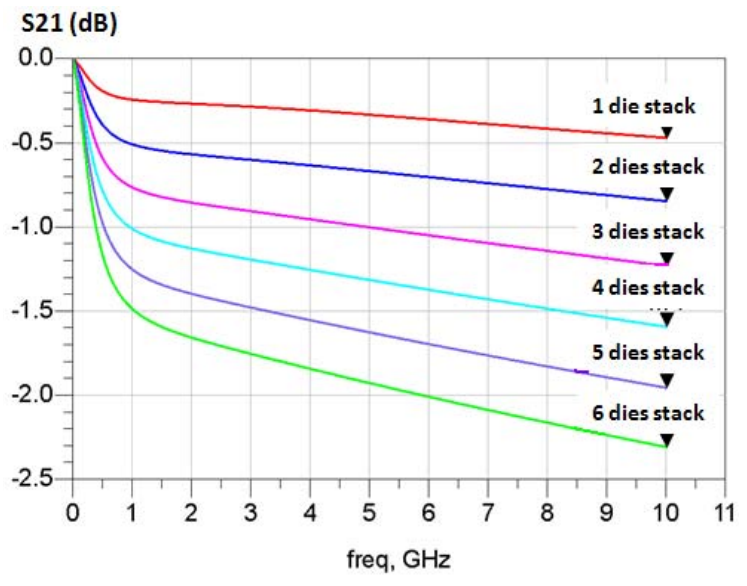

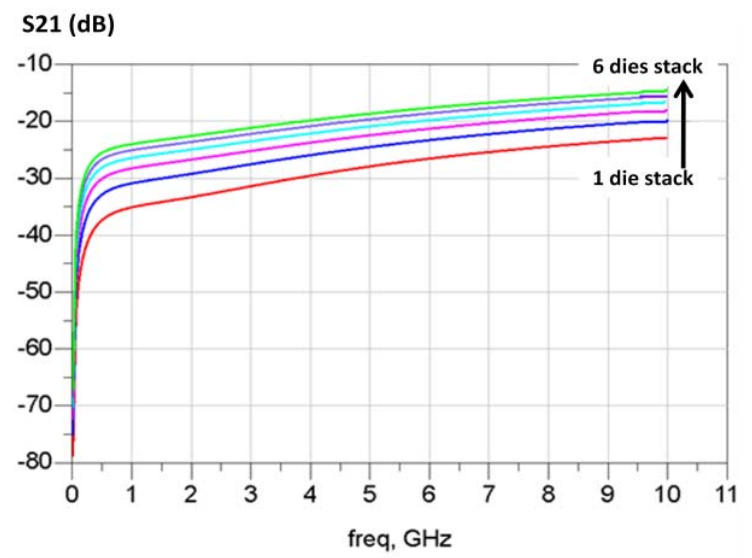

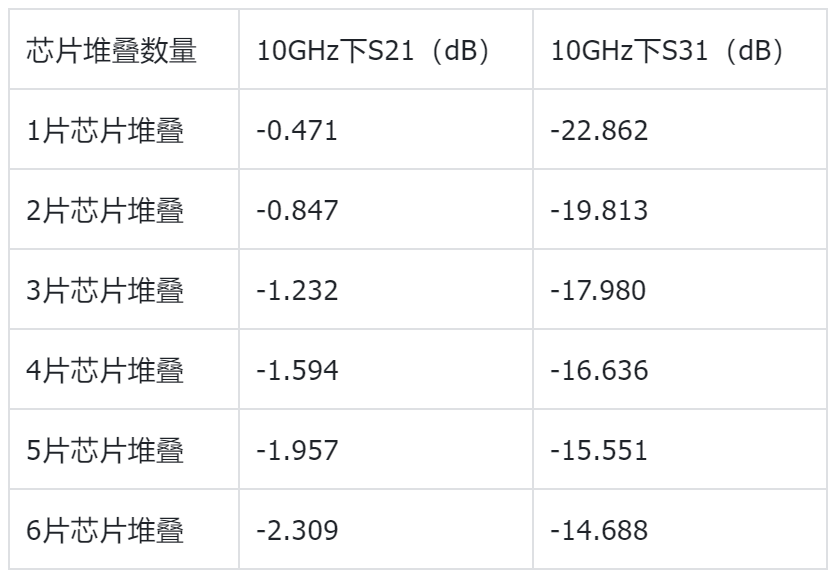

图2展示了多芯片堆叠的插入损耗(S21)和近端串扰。随着芯片数量增加,S21性能逐渐恶化,因为更长的路径会产生更多损耗。从表2的统计结果可知,每增加一片芯片,平均损耗增加约0.3~0.4dB。额外损耗主要源于有耗的周围硅,导致信号向地泄漏能量。

图2a 不同芯片堆叠数量的S21(插入损耗)

图2b 不同芯片堆叠数量的S31(近端串扰)

表2 不同芯片堆叠的S21和S31

与S21类似,近端串扰(S31)随芯片数量增加而增大,因为更长的路径导致两条信号路径的耦合长度更长。

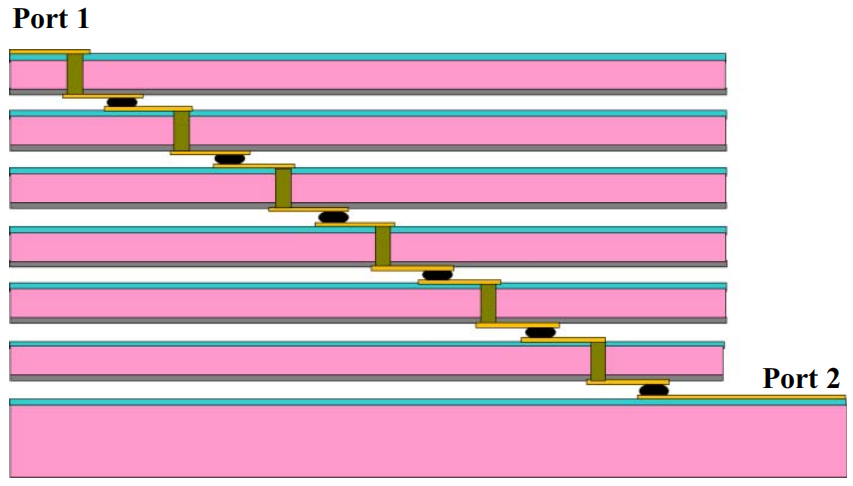

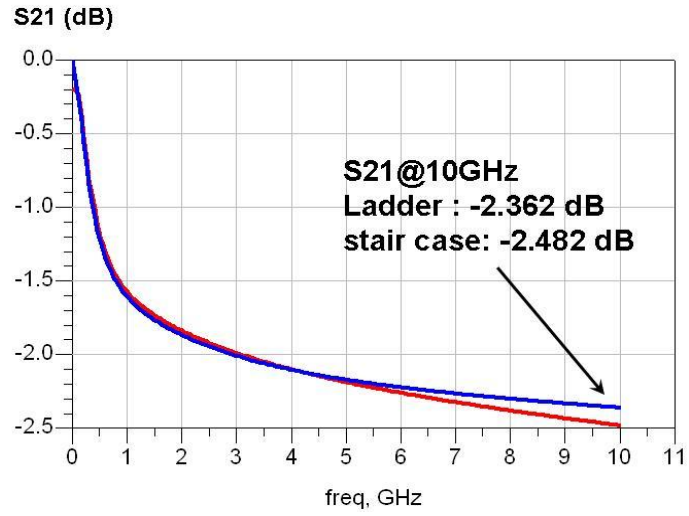

TSV与凸点的另一种布局拓扑为“阶梯状”结构,不同于图1a中的“梯状”结构。图3展示了“阶梯状”模型的横截面,以及两种模型下GSG配置互连的插入损耗对比。

图3a TSV与凸点的阶梯状布局

图3b TSV与凸点阶梯状和梯状布局的S21

梯状和阶梯状堆叠结构的S21性能相近,但阶梯状芯片堆叠在整个路径上占用更大的硅衬底面积,因此更易受串扰和电磁干扰(EMI)问题影响。

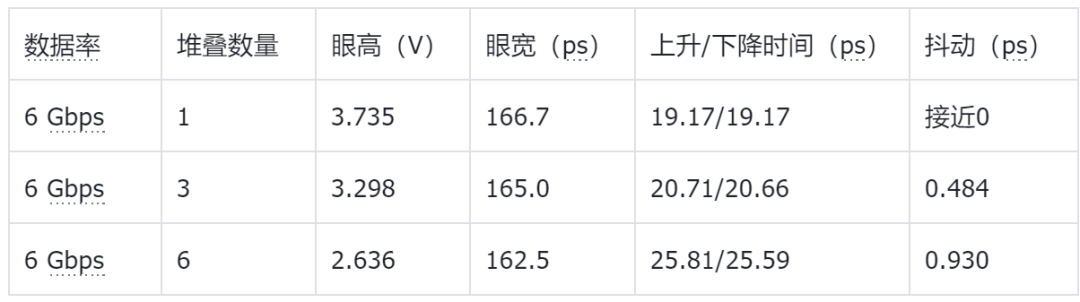

眼图

为更深入了解传输系统性能,基于互连路径的S参数仿真得到了眼图。输入设置/条件如下:

-

数据比特率:6 Gbps

-

伪随机二进制序列(PRBS)寄存器长度:32位

-

幅度:200 mVpp

-

负载:50Ω电阻

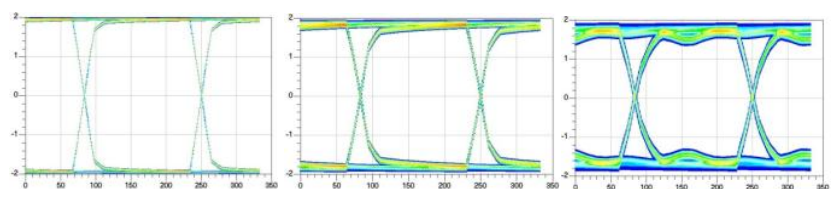

图4展示了1片、3片和6片芯片堆叠在6 Gbps下的眼图。表3为不同芯片堆叠数量在6 Gbps数据率下的眼图仿真结果。随着堆叠芯片数量增加,眼图张开度变小,抖动和上升/下降时间变长。结果表明,在6 Gbps下眼图张开度保持良好,说明数据质量优异。

图4 1片、3片和6片芯片堆叠在6 Gbps下的眼图

表3 芯片堆叠的眼图测量结果

TSV等效电路

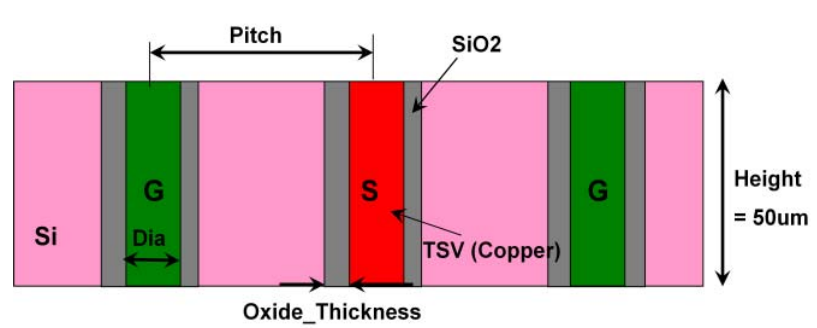

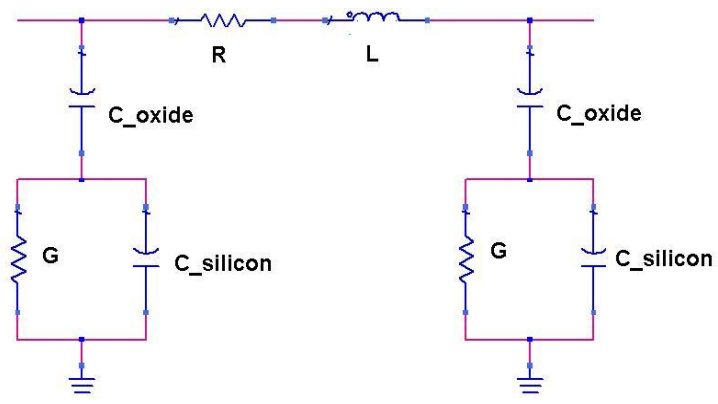

RDL的响应可通过宽度、间距、长度等几何尺寸预测,而凸点由于电长度较短(微凸点高度最终可低至10μm),其损耗可忽略不计。TSV因位于有耗硅内部,成为整个互连路径中的关键部分。本节建立了GSG结构TSV 3D模型的传输线等效电路,通过修改等效电路中相应元件的参数,可反映TSV模型参数的变化。图5展示了GSG结构TSV模型的横截面和传输线等效电路。

图5a GSG结构TSV模型的横截面

图5b GSG结构TSV的传输线电路

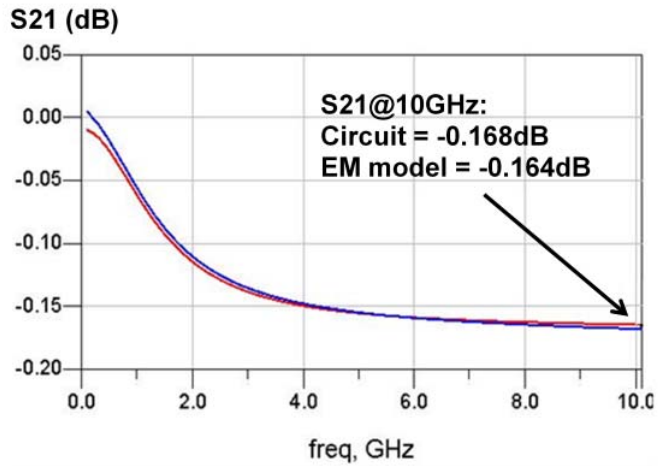

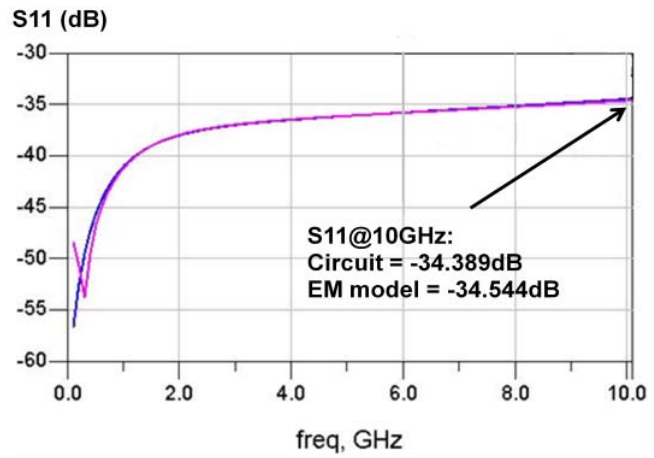

其中,R和L分别表示信号TSV的电阻和电感;C_oxide是信号TSV与硅之间的薄氧化层形成的电容;C_silicon和G分别是有耗硅从信号到地的电容和电导。对RLCG值进行仿真和调试,使电路的S参数与电磁提取得到的S参数匹配。图6展示了TSV直径=5μm、间距=30μm、氧化层厚度=0.2μm时,S11和S21的匹配结果。

图7a 电磁建模与等效电路的S21匹配结果

图7b 电磁建模与等效电路的S11匹配结果

氧化层厚度变化

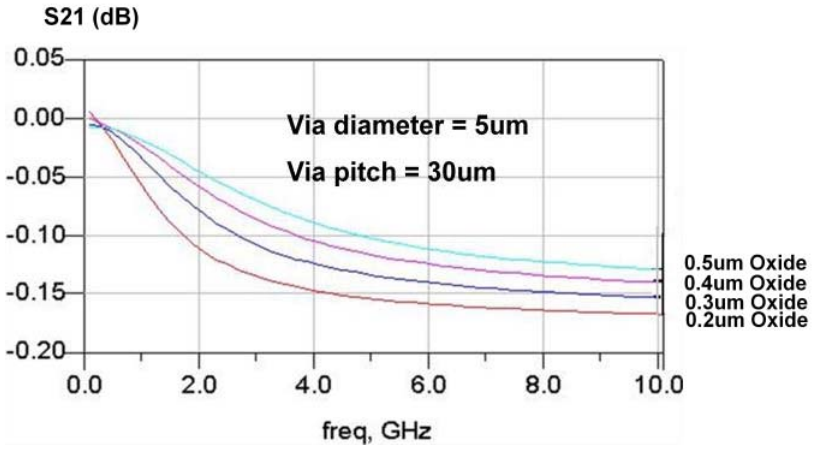

图8a展示了TSV直径/间距固定为5μm/30μm时,不同氧化层厚度对应的S21。

图8a 不同氧化层厚度的S21

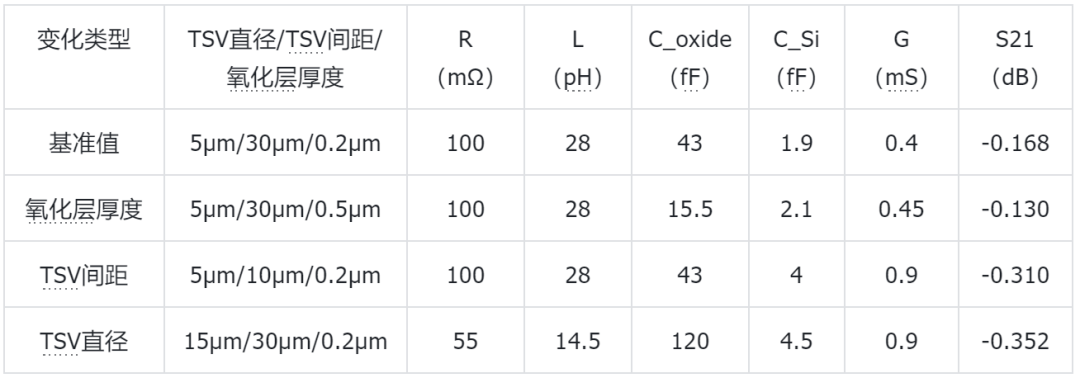

氧化层厚度增加可改善TSV与导电硅衬底之间的隔离度,因此氧化层越厚,S21性能越好。在电路中,氧化层厚度的变化可通过改变C_oxide的值来体现,如表4所示。当氧化层厚度从0.2μm增至0.5μm时,由于TSV与导电硅之间的距离增大,C_oxide减小。

TSV间距变化

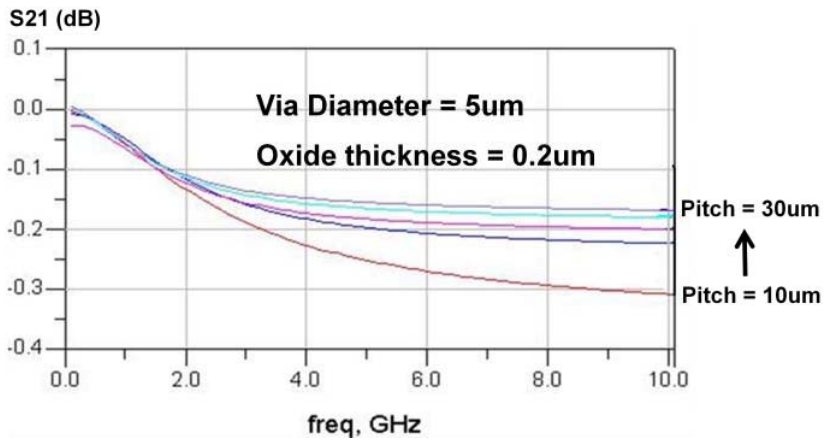

图8b展示了TSV直径=5μm、氧化层厚度=0.2μm时,不同TSV间距对应的S21。

图8b 不同TSV间距的S21

随着TSV间距增大,信号与地之间的C_silicon和G减小,导致从信号到地的泄漏电流减少,S21性能更佳。C_Si和G对应的电路元件参数如表4所示,由于信号TSV与接地TSV之间的间距增大,电容和电导均减小。

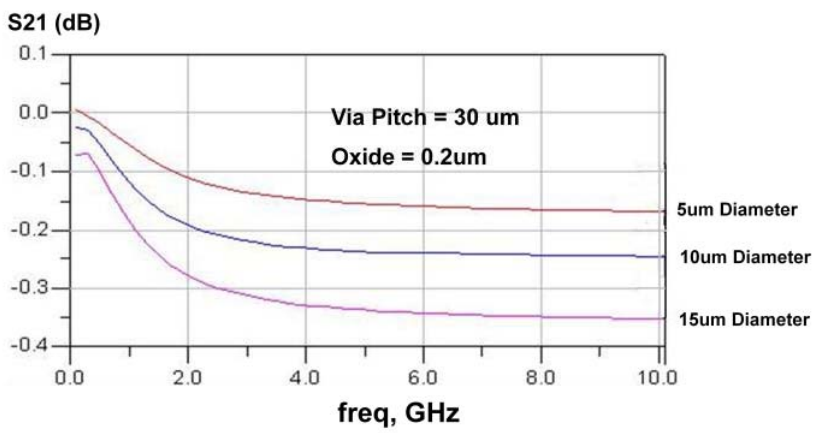

TSV直径变化

图8c展示了TSV间距=30μm、氧化层厚度=0.2μm时,不同TSV直径对应的S21。TSV直径变化会导致TSV之间的距离和氧化层电容发生变化,即使间距和氧化层厚度保持不变,所有电路元件的参数也会与初始值不同。

图8c 不同TSV直径的S21

增大TSV直径等效于减小TSV间距,会导致更多能量泄漏,使S21性能下降。此时,如表格4所示,由于TSV直径和间距均发生变化,所有电路元件的参数均会改变。

表4 不同几何尺寸变化下的等效电路元件值

结论

上面对包含多条TSV-RDL-凸点路径的3D堆叠芯片互连进行了全波电磁仿真研究和眼图分析,并建立了GSG配置TSV的等效电路,实现了建模参数变化与电路RLC值变化的对应。为TSV高速互连设计提供设计指导方向。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献16条内容

已为社区贡献16条内容

所有评论(0)