基于官方EVAL-AD7779FMCZ板的AD7779芯片开发教程

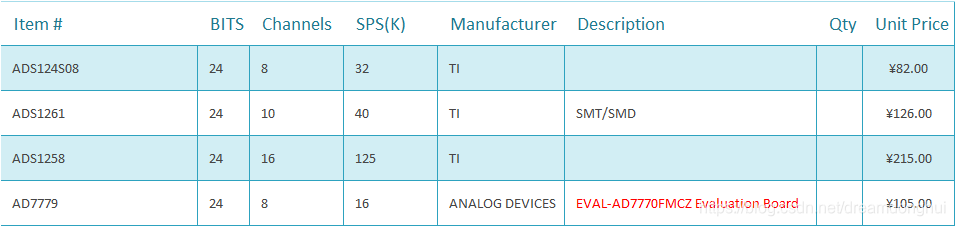

文章说明声明如若转载,请附转载地址并声明原作者。此项目在GitHub托管,托管地址。若链接失效请向作者索要。邮箱:dreamdonghui@163.com说明本项目分AD采集模块和软件模块。本文为硬件模块,AD采集的软件模块请参考该文章。项目需求一秒一千次采样以上,30通道以上,24bit以上分辨率。器件选型...

文章结构

文章说明

声明

如若转载,请附转载地址并声明原作者。此项目在GitHub托管,所有的资料包括datasheet都在GitHub托管,托管地址。若链接失效请向作者索要。邮箱:dreamdonghui@163.com

作者还拥有个人公众号,会写一些感悟文章,知圈,二维码如下,欢迎扫描关注:

说明

本项目分AD采集模块和软件模块。本文为硬件模块,AD采集的软件模块请参考作者的该文章。

项目需求

一秒一千次采样以上,30通道以上,24bit以上分辨率。

器件选型

最终选择:AD7779

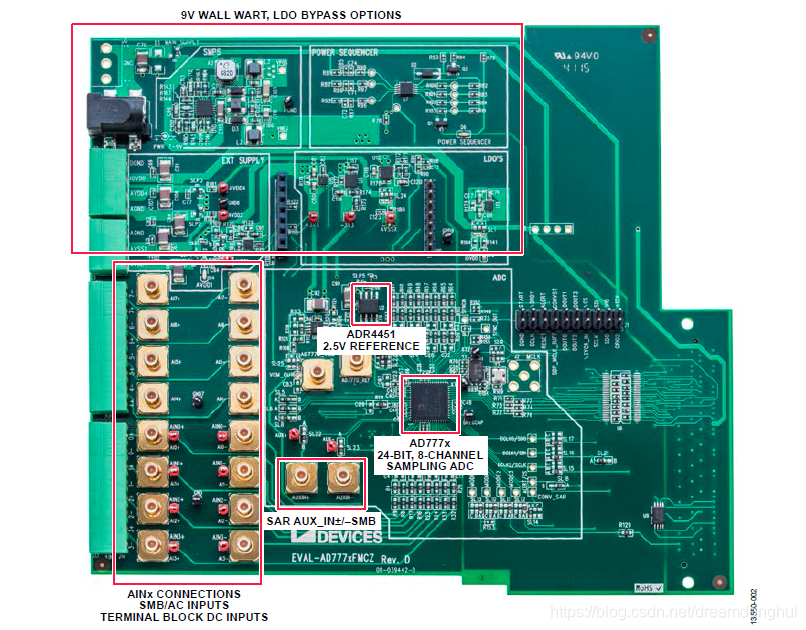

并选购了官方demo板:EVAL-AD7770FMCZ Evaluation Board

开发板快识

SPI通信

该例用到的SPI知识集

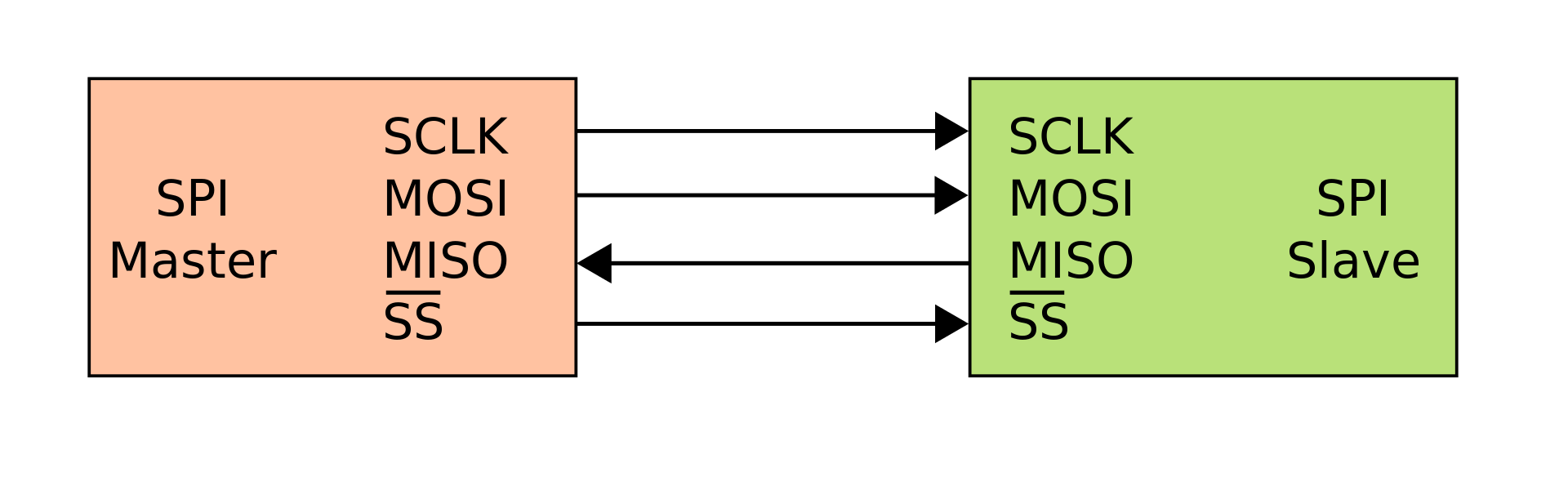

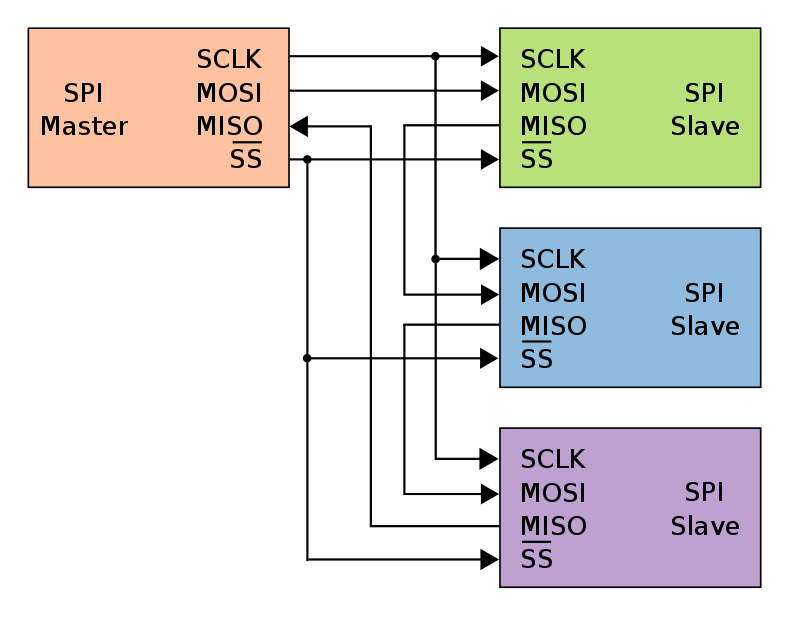

单主从基本SPI原理示意:

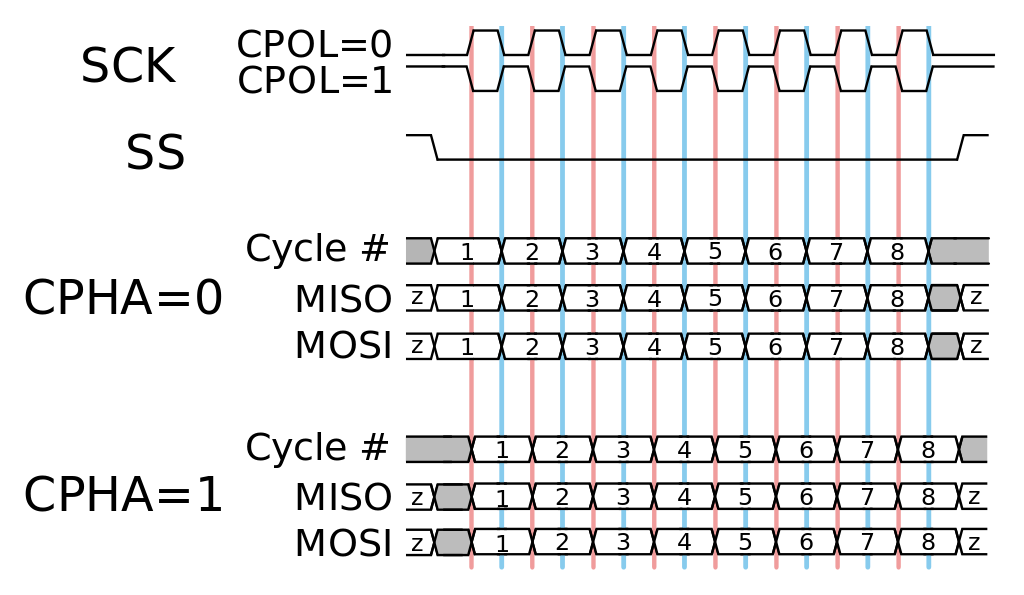

SPI 四种模式/Mode numbers

缩写解释:

CPOL:clock polarity 时钟极性

CPHA:clock phase 时钟相位

一般"Microchip PIC"和"ARM-based" 微处理器遵循以下规则(NCPHA为CPHA取反):

| SPI mode | Clock polarity (CPOL/CKP) | Clock phase (CPHA) | Clock edge (CKE/NCPHA) |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 2 | 1 | 0 | 1 |

| 3 | 1 | 1 | 0 |

其它处理器遵循以下规则:

| Mode | CPOL | CPHA |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

时序如下:

- CPOL决定时钟的极性。

- CPOL=0,低电平为空闲态,每一个周期包含一个高电平脉冲。用上升沿表示开始,下降沿表示结束。

- CPOL=1,高电平为空闲态,每一个周期包含一个低电平脉冲。用下降沿表示开始,用上升沿表示结束。

- CPHA决定时钟脉冲和数据位的对应关系。

- CPHA=0,在脉冲结束时改变数据,在脉冲开始时(或脉冲开始后很短的时间内)读取数据。数据从上一个脉冲结束开始一直保持到当前始终周期结束。对于第一个时钟周期,master(主机)第一位数据必须在时钟沿到来之前保持在MOSI线上。该模式也被理解为:前半周期空闲态,后半周期赋值。

- CPHA=1,在脉冲开始时改变数据,在脉冲结束时(或脉冲结束后很短的时间内)读取数据。数据一直保持到下一个脉冲开始。对于最后一个周期,slaver(从机)必须将数据保持在MISO线上一直到slave select(SS)使能关闭。该模式也被理解为:前半周期赋值,后半周期空闲态。

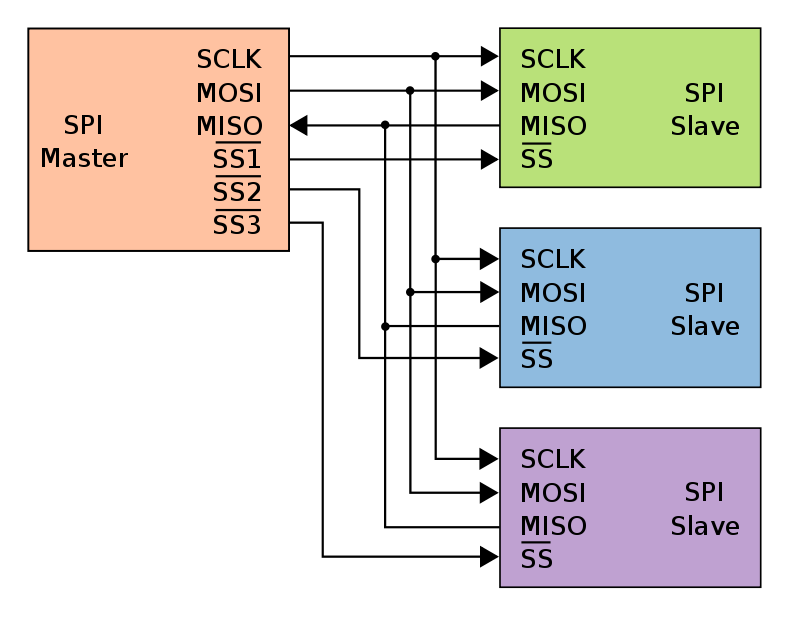

SPI的两种多负载方式

Independent slave configuration/独立控制模式

独立控制模式比较好理解,利用片选信号进行从机控制。

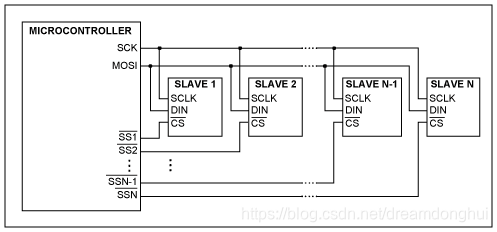

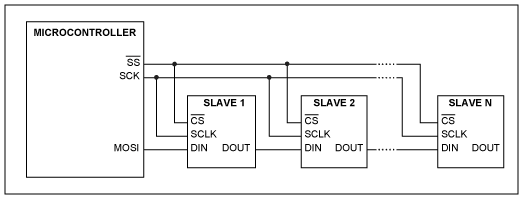

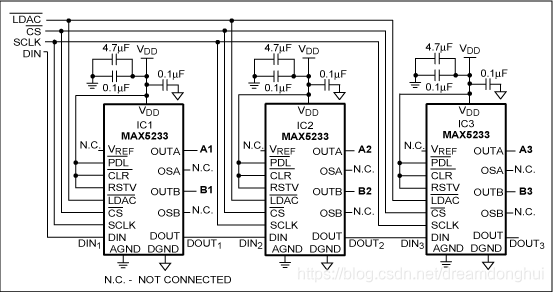

Daisy chain configuration/菊链法

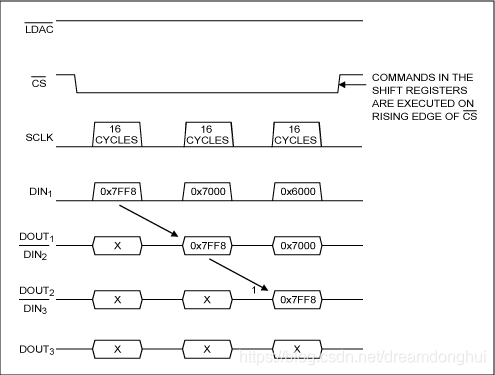

如上图所示,菊链法利用的类似锁存器的原理,将主机发送的信号进行传递。实例解释如下:

以最清晰的如上最后一张图来解释,每一个使能(C̅S̅)周期包含三段数据(与挂载从机数量相同)。第一个数据周期将数据存在了从机一的上;第二个数据周期时,从机一在接收第二段数据的同时,将上一个周期收到的数据传给从机二,这样,当第二个数据段周期结束时,从机一的数据被覆盖成了第二个数据周期的数据,而从机二则收到了由从机一发来的第一段数据;第三个数据段周期时,从机一的数据被第三段数据覆盖,从机二的数据被第二段数据覆盖,而从机三终于收到了由从机二发来的第一段数据。三个周期完成后,从机一、从机二、从机三分别存储的是第三段、第二段、第一段数据。此时,该阶段的所有数据传输完成,等待芯片处理动作(比如此时进行指令执行),动作完成后可以再以同样的原理进行下一个菊链数据的填充。

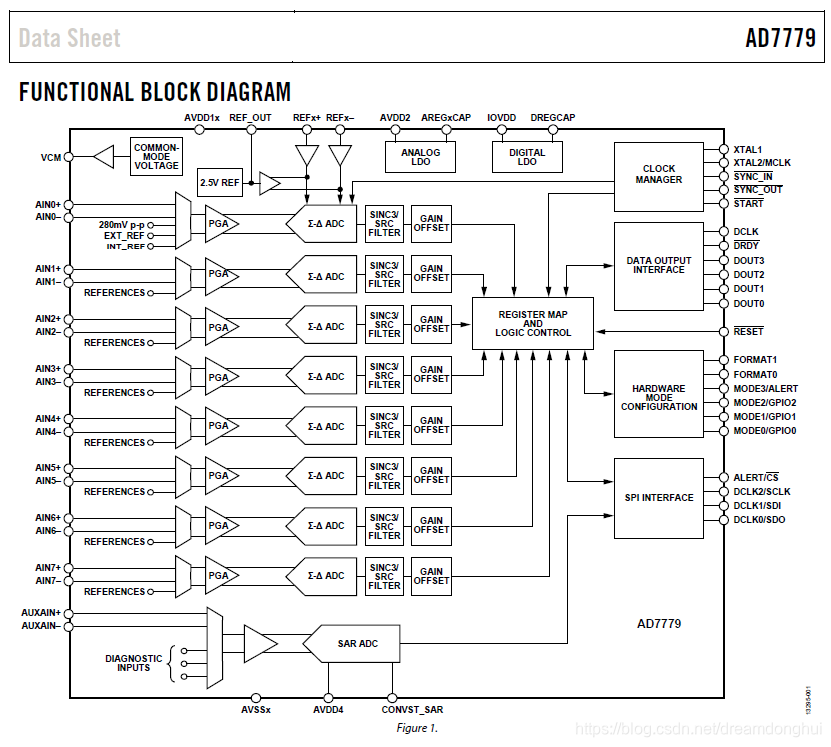

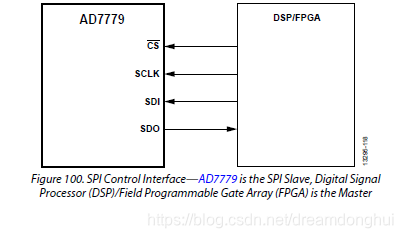

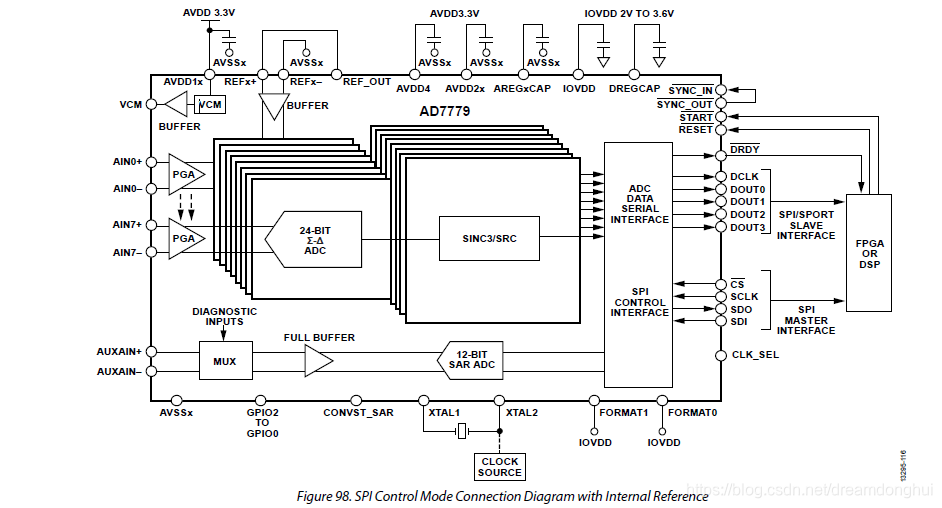

AD7779的SPI

评估板的Demo连接

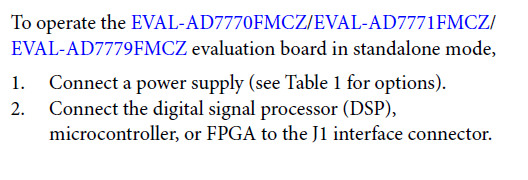

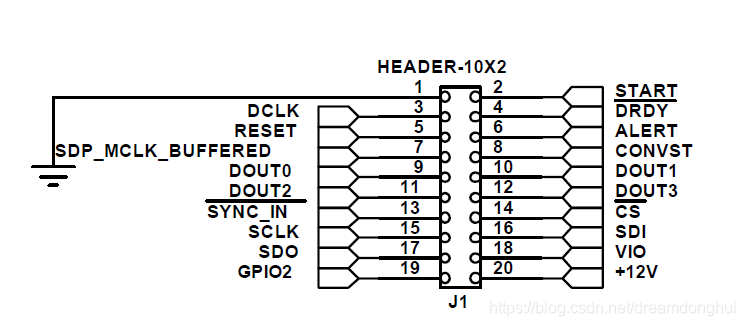

在手册中,提到了评估版的基本接口:

如上图,手册中提到,独立使用时:

-

- 连接电源。

-

- MCU连接J1。

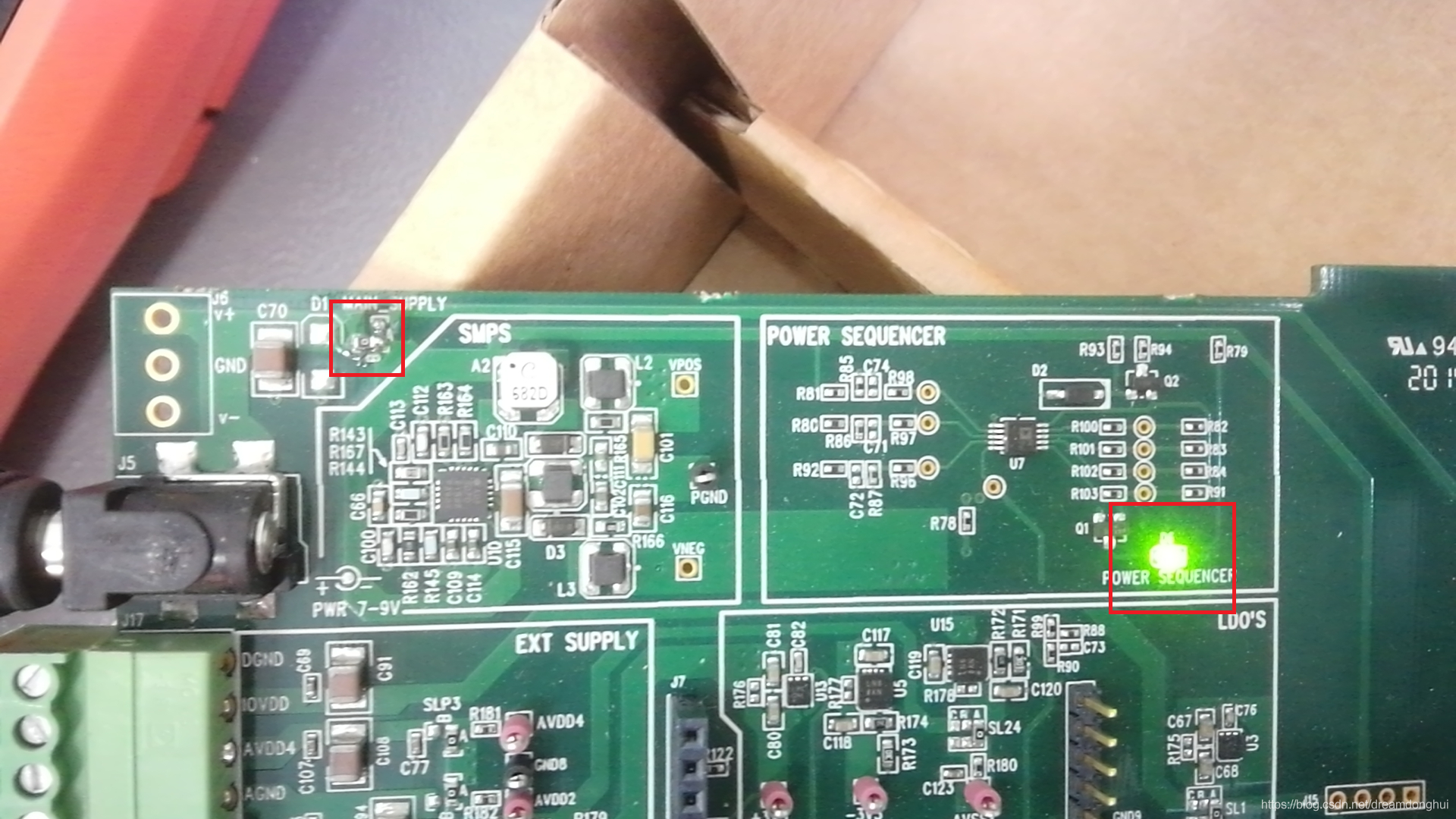

考虑方便插接,选的J5通过wall wart接口通9V电压供电。插上后发现没反应,查看手册,默认不是此供电接口,通过下图的0Ω开关来控制的,把0Ω电阻从A位置(position)拆下来,重新焊道B position,插上电源,灯亮。(请勿将A、B位置同时短路,这两个是直连的,如果同时接入两个不同电压的电源会烧回电路/电源设备)。

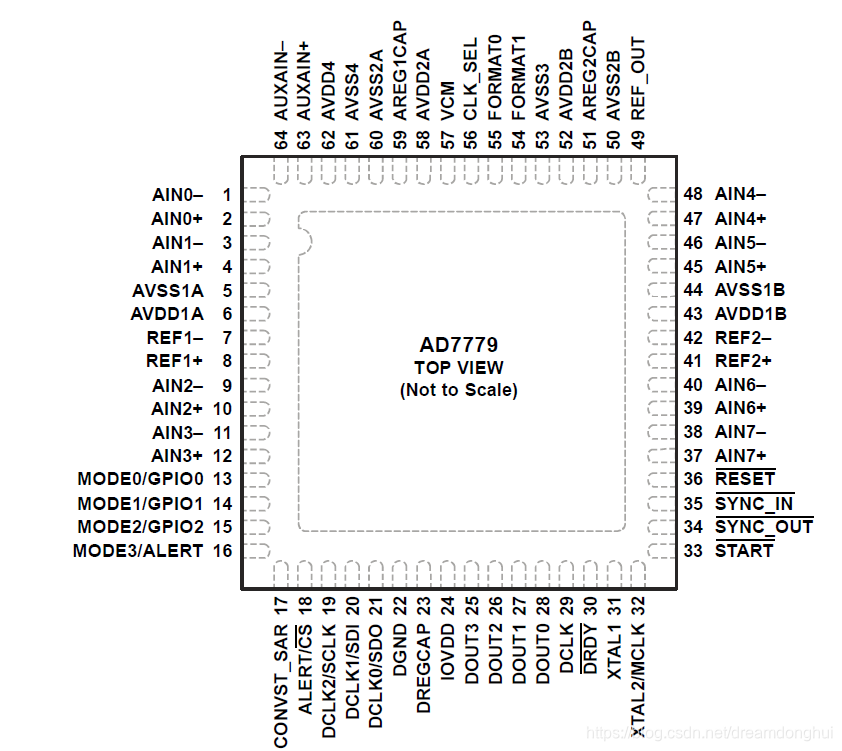

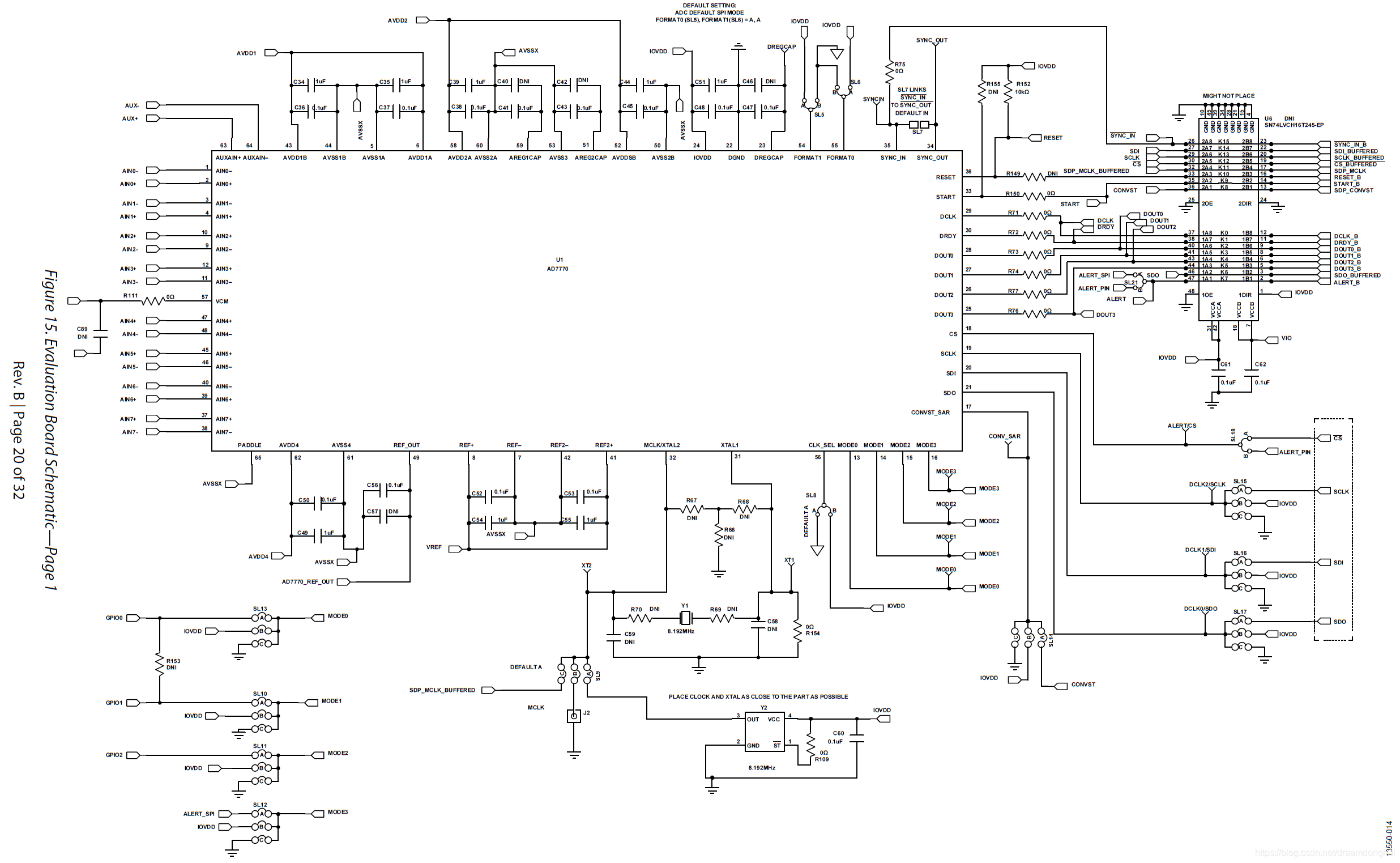

因为手册中说MCU通过J1控制,所以找出J1的描述及其J1所连接到的AD7779(Manuel中为AD7770):

通电用示波器测试了一下,J1接口所有信号线都没有信号输出,包括时钟线。说明要demo版的默认设置不是J1输出,需要更改。

搜索Manuel并找出J1输出相关的如下板载开关(Solder Link Options)位置:

| Link No. | Default Option | Description | 更改为 |

|---|---|---|---|

| Main_SUPPLY | A | Unregulated input voltage source selection.

|

前面改了由J5输入9V供电,所以此处应改为B位置。 |

| SL1 | A | IOVDD supply selection.

|

由于我们并没有接SDP-H1板,而我们的MCU板选择3.3V输出,所以我们在此将此开关改为B位置。 |

| SL5, SL6 | A | Data interface format selection. The evaluation software only supports SPI control mode. The default condition is SPI configuration. See the AD7770, AD7771, and AD7779 data sheets for more information. | SL5应为A,SL6应为B,以使输出为DOUT0输出ch0–Ch7 |

| SL10, SL11, SL13 | A |

GPIO/mode pins.

|

经查看,改为C位置,以使MODE0–MODE3为0,Decimation Rate 1024,SPS为1000,PGA Gain都设为1 |

| SL14 | A |

CONVST_SAR selection.

|

改为C |

| SL15, SL16, SL17 | A |

SPI data interface lines.

|

SL15改为B位置,SL16改为C,SL17改为C |

| SL18 | A |

SPI data interface line.

|

可能需要更改 |

| SL21 | A |

Alert connection.

|

可能需要更改 |

将SL1改为B位置后,通过示波器测试J1引脚,有输出,其中,

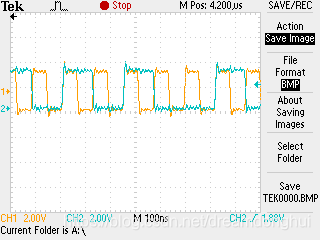

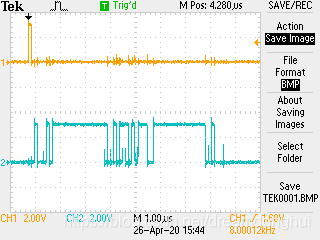

Dclock 和 DOUT2 输出如下:

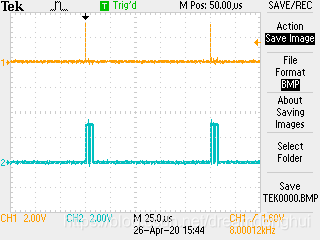

\ready和DOUT2输出如下:

DOUT2(黄色)和DOUT3(蓝色)如下:

从信号可以看出,此时的配置:

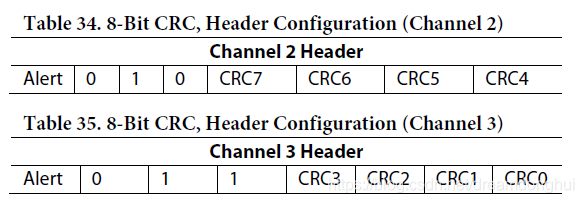

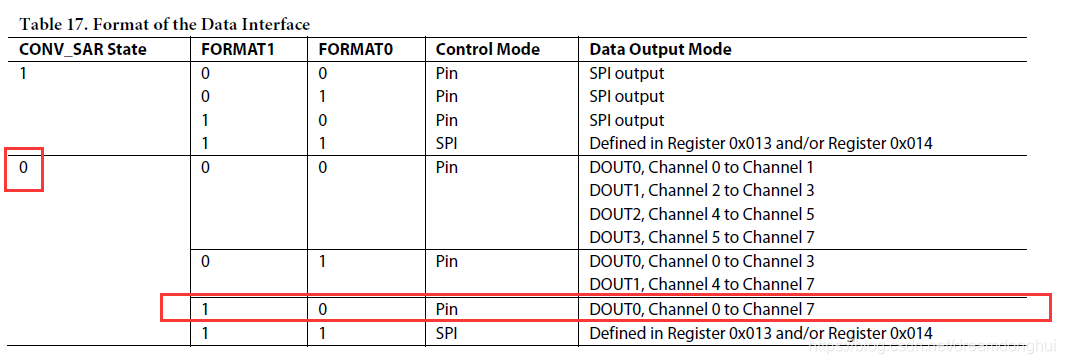

经查看电路连接,现在的FORMAT0和FORMAT1都接到了IOVDD,即高电平。

手册中关于该配置的描述:

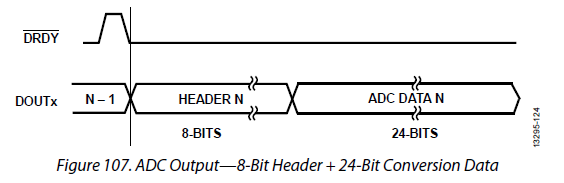

根据描述,我们应当按照如下图设置,即SL14接到C位置以使CONV_SAR State设置为0,将SL5放在A位置以使FORMAT1设置为1,将SL6接到B位置以使FORMAT2设置为0,这样一来我们需要三根线(DREADY/DCLOCK/DOUT0)就可以将七路信号读回。

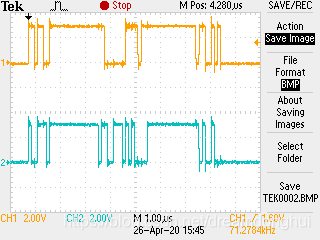

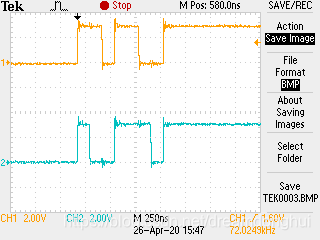

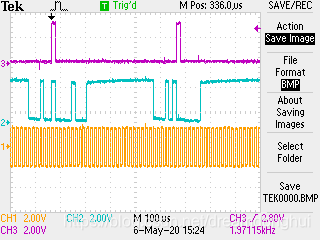

上图的MODE3/MODE2/MODE1/MODE0设置为0/0/0/0以将Decimation配置为1024。然而示波器发现并没有输出八通道数据,只有一通道数据。如下:

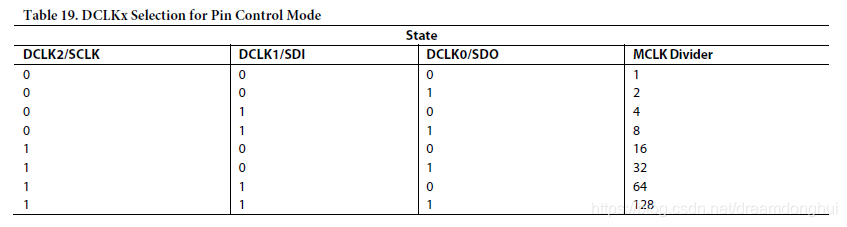

查看手册,发现下面的DCLK没有设置,如果未设置,由于传输太慢,后面的数会被新的数据覆盖,其余通道一直没有机会输出。燃着如下更改。

根据如上公式计算,由于之前选择的Decimation为1024,输入为DOUT输出8通道:

D C L K M I N < 1024 8 × 8 = 16 DCLK _{MIN} < \dfrac {1024}{ 8 × 8} = 16 DCLKMIN<8×81024=16

DCLK2/DCLK1/DCLK0至少应配置为1/0/0以使其为配置为16分频以防止数据被覆盖。

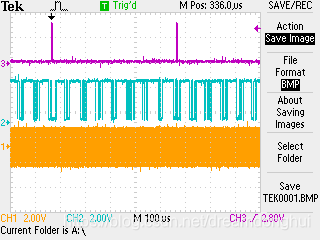

更改后八通道数据全部出来了,示波器显示如下:

至此,硬件配置完成。如需查看后续的与MCU主机通讯,请查阅作者的此篇文章。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)