改进100BASE-TX以太网芯片-- 保证工业以太网闭环控制的确定性V1

本文针对工业以太网闭环控制中100BASE-TX/T1协议因干扰导致链路重建时间过长(330ms/100ms)的问题,提出两项物理层改进方案:1)每帧重启扰码器-解码器同步机制,利用正常帧间隙实现零额外时间开销;2)单组双绞线半双工方案,通过类似CAN的即时NACK机制实现错误快速重传。分析表明,100BASE-T1在汽车电子场景中抗干扰优势有限,而改进后的100BASE-TX在保持125M带宽优

**

改进100BASE-TX以太网芯片-- 保证工业以太网闭环控制的确定性V1

**

杨福宇 yfy812@163.com 2026-1-26

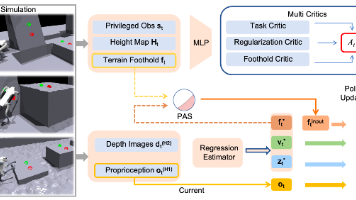

摘要:从比较和论述100BASE-TX与100BASE-T1出错开始,说明出错是不可避免的,但是出了错会造成这二种协议LINK错,重建link需要的时间太长,100BASE-TX需要330ms,100BASE-T1需要100ms。这对文字处理不是问题,但是对于工业控制可能是灾难的开始,因为工业应用上闭环控制变开环就是失控了。因此提出了基于100BASE-TX的每帧都重启扰码器-解码器的同步的方案,这个方案只用正常IFG的位流,因此不需要额外的时间,从而解决了大的失控时长问题。另外,提出了基于100BASE-TX的单组双绞线半双工方案,其特点是可传送类似CAN的接收节点立即NACK信号,阻断出错后发送节点的发送,提示立即出错重发,保证以太帧的传送时序。同时也节省了出错后无效带宽。这些物理层的改进与现有标准不全相同,不影响数据链路层,可以大大拓展它在闭环控制上功能安全的性能指标。IEEE也没有以太网名称的专利权,所以改进也可叫某种以太网,也可叫其它什么名字。

关键字:100BASE-TX,100BASE-T1,Link down,ISO7637-3 ,帧内报错

1.探索无约束

需要就是市场。这个市场就是网联车、机器人、风电等,40年前的标准及其后裔没有完全满足工控的需要,现在的以太网100ms的link重建时间对文字处理可以忽略,但对闭环控制可能是灾难的开始。现在100km/h-0实测刹车距离的第1名是智己LS6 33.35m ,第8名是非凡F7 33.92m,如果有100ms的停止工作,那么要多加2.77m,不光是排名落后可能100名了,而且已经撞车撞人了。

Interoperability是技术推进的利器但也是束缚,但是要改缺点就不可避免与原有协议的不可互操作,你还可以建立新的互操作性群。想想“以太网冰淇淋”可以,你也可以创造自己的以太网协议(例如100BASE-TX1,最后的1代表1对双绞线),只要卖得出去。

2.100BASE-T1的不利点

比较100BASE-TX与100BASE-T1的优缺点:

1)100BASE-T1是为汽车用的。以15m为限。而100BASE-TX以100m为限,从应用场景来看有重叠(100BASE-TX已用于OBD),但是100BASE-T1要的带宽是66.6M,而100BASE-TX的带宽是125M,所以100BASE-T1抗线缆来的干扰要强,但抗干扰不止是线缆上的带宽;

2)在汽车内像摄像头,域控制器之间的传送SerDes对100BASE-T1的竞争很强(可达6.8Gb/S甚至更高,未来12Gb/S@HMST),100BASE-T1的非屏闭双绞线也是很容易出错的。例如TJA1100收发器输入阻抗的差就会将共模变为差模有输入阻抗容差±5%,它会导致出错,下面加以分析。

TJA1100 P39/52

在这里插入图片描述

在这里插入图片描述

在ISO7637-3,3a,3b干扰的主要频率16M下,隔直电容100nf的阻抗Z=0.1Ω,可以忽略不计,同极性的共模干扰经过200μ共模电感时在铁芯中的磁通是同向的,只要没饱和就可以分别计算回路动特性。

200μH共模电感在16M时的感抗接近20KΩ。耦合阻抗为 R~14K@16M(见后),P,N二个线圈並联,于是分到电压25V@源60V。

在忽略共模电感本身的不对称性,只计算2个串连51Ω及输入阻抗的不对称性的LR特性:

例如R1=47.5+ 102x0.99=148.48Ω ,R2=52.5+ 102x1.01 =155.27Ω。LR的时间常数T1=200/ 148.48μS =1.346μS ;T2=200/155.27μS =1.288μS。ISO7637-3干扰峰的时长为td=150nS,从上升时间tr=5ns开始之后的耦合到共模电感前的电压初值20V,80ns后为>10V,都按10V计算串模干扰:

Vd2c=10x【47.5/148.48(1-e-80/1346) -52.5/155.27(1-e-80/1288】=10x【0.184-0.0602】=1.2V。

这个差模电压足以使PAM3出错。在这种情况下100BASE-T1的非屏蔽双绞线也要改为屏蔽线,与SerDes比就没任何优势了。

3.0版本的启动时间为100ms,不是原来的200ms

出错之后便会有自同步解码器的失去同步,重建同步的100ms的通信停止服务!与100BASE-TX的重建同步的330ms是50步笑100步。

3)市场上100BASE-TX与100BASE-T1芯片的价格相近(~¥8-9@100片),来自电源的干扰都会引起二者link down,100BASE-TX重建link需要330ms,100BASE-T1重建link需要200-100ms,这个时间在实时控制中是不能接受的。

例如ISO7637-2,ISO7637-3 3a,3b的干扰群间隔t3=90ms,尚未重建好又link down了,即使采用环网做冗余也会失效,无法满足功能安全的要求,例如网联车的域控、人形机器人。

在改进重建link方面100BASE-TX容易(见后),可达到无需额外的link重建时间。而且100BASE-TX可工作到100m,应用面更宽,例如风电。100BASE-TX也用于EtherCat,EtherCat也是机器人内部通信的常用选项。100BASE-TX只用一对双绞线作半双工应用也可满足大部份应用,将来学习作单电缆全双工也有可能。所以本文以100BASE-TX为主讨论。

3.为什么会link down?

Link down有二个来源。一是传输线上干扰引起出错,这个错使自动步解码器失去同步,本章讨论此种情况,第二个原因是电源干扰使时钟相关操作出错使解码器失去同步,将在下一章讨论。

100BASE-TX PMD.PDF P4/36

1)干扰引起出错

总线上的信号是经过变压器耦合的,100BASE-TX有变压器性能的规定。

在TI DP83826中介绍的通用100BASE-TX的建议。例如differential to commen mode rejection ratio 项。

100BASE-TX变压器的输入是来自发送方symbol信号的3态模拟电压,1v,0v,-1v,经变压器的insertion loss 之后到总线上约0.88v,如果干扰感应到总线上的差压达到一半(0.44V),那么就可能造成symbol读取的差错(MLT-3译码错)。接收方变压器也有insertion loss,接收节点收到的电平约0.8v,0v,-0,8v。

100BASE-TX采用4B/5B编码和MLT-3线路编码,数据在双绞线上以125兆波特率进行传输,即每个symbol要8ns,MLT-3编码规则(在+1, 0, -1三个电平间变化,4B/5B编码保证不会出现超过4个连续的“0”,这些边沿就是PLL进行相位对齐的“参考点”。

接收电压经过6位AD采样,然后经MTL-3译码变为symbol数字输出。接收方对这个输入模拟量要做很多工作才能判断是否会产生link down。

车内的电磁干扰比较典型的是ISO7637-3,3a,3b波形,为了求出干扰的大小,参考了:Niels Lambrecht , H. Pues et al. A Circuit Modeling Technique for the ISO 7637-3 Capacitive Coupling Clamp Test. IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY, VOL. 60, NO. 4, AUGUST 2018

对电容耦合钳法(CCC)作仿真与实测的比较,该文提到其内容以ISO 7637-3 的60V干扰波型3B(REF 6.p3/9)为例。而这个的实测数据我将用于本文中( “In this paper, we will test with the pulse 3b shown in Fig. 3 at level II. This test level corresponds to the following parameter values: US = 60 V, tr = 5 ns, td = 0.15 μs, t1 = 100 μs, t4 = 10 ms, and t5 = 90 ms.”)。

从上图可见VA,VB是被测的输入,即DUT=10K ohm时耦合到25V,因为ISO 7637-3 的 td = 0.15 μs. 相当于16M。由分压关系25V/60V=10K/(R+10k)。这相当于耦合阻抗为 R~14K@16M。

用变压器耦合的100BASE-TX收发线路中的变压器型号为XH1198FNL,内带共模电感,媒体侧350μH,变压器的阻抗近似35.2K@16M,以此估计变压器前的共模电压为35.2/(35.32+16)×60=41.2V,由上述TI DP83826表10-2要求共模抑止比为-30db,变压器后串模电压41.2V×10-1.5=1.3V,而(p12/116)VOD Differential output voltage 范围为min950 max1050 mV,所以100BASE-TX是一定会出错的。

2)出错到判link down

为了link重建的需要,接收节点的解码器是一种自动步解码器,解码结果将送到解码器移位寄存器的最低位。当接收过程出错时看,扰码器与解扰器同步就丢失,造成后续位流更多的错,出错数是link down的判断依据之一。

LAN9253是MICROCHIP生产的2/3-Port EtherCAT® Slave Controller with Integrated Ethernet PHYs。这个数据页是2020年的版本,也是当前用的器件之一。其物理层是基于100BASE-TX的以太网协议,其中有输入差压的最小值,变压器后串模电压1.3V远大于它:P385/402

100BASE-TX判出现link down的依据:

P183/402

DP83826E p65/116

DP83826E p46/116 有判link down的5个条件

第2条是严重干扰引起MLT-3频出+1V、-1V直接跳变,可以计数。

第3条是信噪比记录不好。未查到定义,理解为小于0.1V的能被AD感到的过0信号(+1V对应ADC=64,-1V对应ADC=0,0V对应ADC=32),可以计数。

第4条是电源没了。

第5条是上述4条的合并处理。这些会导至RX错,间接使自同步解码器失去同步。

自同步解码器失去同步后,扰码器11位,假设发生自同步解码器不同步时每11位有1个RX错,只要352ns第1条就满足就能满足。可是不知道正确的RX是什么,1)所以这一条仅当5b为非法码时才能计数:2)如错的5b碰巧成为控制码时就成为另一种错误演进场景。3)如无上述情况直到CRC检验才可发现错,那么只有1个错。4)假设帧长处发生错,在自同步解码器link down,同时CRC的位置将错,只有1个错:在接收帧长比发送帧长长时,最坏情况下,CRC将落在空闲区之后的下一帧的场景。这些情况表明发现link down的时间不确定,会有后续演变的后果,例如;自同步解码器已link down,link down的信号报不上去,不能立即启动重建,继续连续link down丢帧。

根据自动步解码器只要1个错就会link down的原理,上述条件可简化为1条:有错就报link down。但是这会导至大量link重建。这是自动步解码器的至致命缺陷,非自动步解码器只有一部份错(第4章)会引起link down。100BASE-TX的link重建需要330ms。

P196/402

To allow the line to stabilize, the link integrity logic will wait a minimum of 330 ms from the time DATA_VALID is asserted until the Link-Ready state is entered. Should the DATA_VALID input be negated at any time, this logic will immediately negate the Link signal and enter the Link-Down state.

3)重建link为什么要花这么久?

我没查到原始文献,我自己的分析如下:。初始状态由扰码器的12位多项式和解扰器的12位多项式决定,共224个状态。在同步过程中它们都在变,最终同步后的状态有212种状态,同步之后只要输入无错,它们就会一直同步下去。按理想情况,可用马尔可夫理论分析,收敛的时间是67.11ms,远小于330ms。但是收发状态同时因移位寄存器规则的约束,使222个状态的变化途径大为减少,造成与马尔可夫理论差异巨大。这330ms可能是大量仿真后的折中选择。

P44/91

TI的DP83848C/I/100BASE-TX收发器在IFG中自动恢复解码器状态,但是并未保证在722us中一定能重同步。它没有給出可能的重建link时间的上限。所以可能DP83826E用了相同的自同步解码器才会这样。

4.电源来的干扰使解码器失步

3.3V的TJA1100 数据手册P37/42耗电量最大可达200mA:

在考虑ISO7637-2波型3a时,LDO的电源受到负电压的干扰脉冲而停止电流供给,但是输出电流由储能电容提供。无干扰时,LDO调整自己等效内阻保证输出电流与电压在稳定值,所以电容充放电电流=0。有干扰时LDO停止供电,负载电流由电容立即提供,而此电流的增长速度由电容本身电感Ls的限制,所以输出电压将有跌落,其跌落量DV=-Lsxd(Iout)/dt。其中dt=tr是波型3a脉冲的上升时间=5ns。Iout是正常稳态负载电流。更精确的计算可以用LRLORD模型计算,其中RLORD=3,3V/200mA=16.5Ω。

d:/miscelanious/AEappGUIDE电解电容:”Aluminum Electrolytic Capacitor Application Guide”介绍:Inductance Ls is the equivalent series inductance, and it is relatively independent of both frequency and temperature.Typical values range from 10 nH to 30 nH for radial-leaded types, 20 to 50 nH for screw-terminal types, and up to 200 nH for axialleaded types. It increases with terminal spacing.

在取Ls=20nH,Iout=200mA(如果要与相连的MCU同享电源,数值将更大),tr=5ns时有DV=-20nHx200mA/5ns=-0.8V。这会使3.3V电源跌到2.5 V<3V,100BASE-T1收发器TJA1100不能正常工作,例如使解码器时钟跳变(晶振与PLL提供的相位合成)本身丢失,或解码器电路移位出错,失去同步。这一分析也同样适用于100BASE-TX收发器解码器失去同步。

这个干扰只要是负的,停止了LDO的供电,就会引起DV=-0.8V。所以很小的干扰(不是-60V,而是-6V)也会失去同步。

5.一种重建Link的改进方法:

既然link down难免,重点就是如何快速重建Link!

1)不采用自同步解码器,x0=x9+x11更新(与输入错无关,开始同步就一直同步,扰解码作用还在);【前面已分析过自同步解码器了(扰码:symout=din+x9+x11,x0=symout; 解码dout=symin+x9+x11,x0=dout), 扰码器解码器初始状态一致,总线无错时symin=symout,便有dout=din,否则,扰解便失去同步,可自同步,但时间太长】.

2)发送节点在ESD(由T/R二个5B的帧结束控制码构成)之后停止扰码,SSD(由J/K二个5B帧开始控制码构成)后恢复以种子初态並开始运行;停止扰码其间发送节点以原来的5B方式输出IIJK流, I为媒体空闲控制码(11111)。(100BASE-TX规定此区间扰码器一直工作,5B方式是在为保证接收节点可以简化硬件创造条件,而且11111是跳变最多的信号)。

3)接收节点在见到ESD前有任何检测错时(这些错可能包括因电源干扰引起的丢步而造成的错,以及MLT-3跳变错、非法5B错),向PMA报错并准备解码器重同步;在ESD时没有出错也要准备重同步。(本设计的要点是无论是否出错每帧都做一次重同步**,对原来link down的判断硬件都省去了**)。

4)解码器重同步内容包括停止解码,把解码器重置为种子状态,用5B输入流观察是否有IIJK流出现,如观察到就认为同步时刻已到,锁定解码器种子並开始运行;(这就保证了收发而端扰码器与解码器状态的同步,由于同步发生在100BASE-TX规定的帧间隔IFG内开始的,这个方法重同步不需要额外的时间)。

5)接收节点对输入位流的判断用20位移位寄存器的比较硬件快速实现。(在1symbol之内完成判断)。

6)帧有错就重发。对于帧长有错时CRC可能落在发送节点ESD(帧结束控制码)后情况,此时错的发现推迟了,可以用另一个检测机制代替:在见到ESD之前见到II帧表明帧长错,这在原来的802.3 clause 24就有,按上述3)处理。这就不影响立即重同步扰码器解码器。

6.更多的改进:带报错反馈的半双工100BASE-TX

重建link是在接收节点一方,但是发送节点不知道发送帧已经出错。在以太网中一般以接收节点发反馈帧通知发送方实现。这种方法增加带宽不说,还有时间的不确定性,而时间的不确定性可能造成时序的倒置。例如第1帧命令机器人举手,第2帧命令机器人伸手,如果第1帧出错,还未确认就发第2帧就会出事故。时序的错误可能对分散系统取得共识有害。

这里可以参考CAN设计报错信号,或将100BASE-T1的全双工结构作简化(不需要多余的接收功能模块如解码器、5B/4B等等)。

接收节点的发送驱动正常时为高阻,发送节点wire-in的ADC=发送DAC,半双工时少干扰。接收节点发送的NACK是三组00111流(120ns)。发送节点对NACK的判断是wire-in的ADC-发送DAC<>0,由于接收节点-发送节点距离(100m=500ns)形成的延迟,NACK与发送位之间有相位差,因此采用三组ADC和DAC的和之差作为判定COL=1(电缆上信号冲突)的依据。总线上的电磁干扰也可能启动这一机制。但是能达到这一程度表明干扰(ISO7637-3,3a\3b 干扰长td=100ns)也可能引起接收出错,已经需要NACK了。发送节点在收到COL后丢弃本帧,在等待延时后重发。这种立即停发减少了发送节点的出错后部分的无效发送带宽。立即报错增加了时序的确定性,减少了上层协议保证时序确定性的开销。这个方案降低了成本提高了性能,是以往以太网未达到的高度(在物理层实现)。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)