74LS48芯片功能实现设计VHDL代码Quartus仿真

74LS48芯片功能实现74LS48芯片是一种常用的七段数码管译码器驱动器,常用在各种数字电路系统的显示中设计代码实现74LS48芯片功能,并进行仿真

·

名称:74LS48芯片功能实现设计VHDL代码Quartus仿真

软件:Quartus

语言:VHDL

代码功能:

74LS48芯片功能实现

74LS48芯片是一种常用的七段数码管译码器驱动器,常用在各种数字电路系统的显示中

设计代码实现74LS48芯片功能,并进行仿真

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

1、工程文件

2、程序文件

3、程序编译

4、RTL图

5、管脚分配

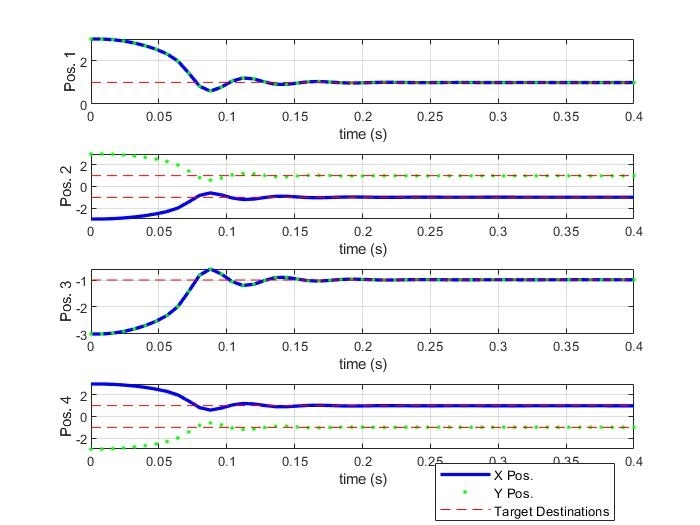

6、仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY chip_74ls48 IS PORT ( A0 : IN STD_LOGIC; A1 : IN STD_LOGIC; A2 : IN STD_LOGIC; A3 : IN STD_LOGIC; LT : IN STD_LOGIC; RBI : IN STD_LOGIC; RBO : OUT STD_LOGIC; a : OUT STD_LOGIC; b : OUT STD_LOGIC; c : OUT STD_LOGIC; d : OUT STD_LOGIC; e : OUT STD_LOGIC; f : OUT STD_LOGIC; g : OUT STD_LOGIC ); END chip_74ls48; ARCHITECTURE trans OF chip_74ls48 IS SIGNAL segment : STD_LOGIC_VECTOR(6 DOWNTO 0); SIGNAL A3210 : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN A3210 <= (A3 & A2 & A1 & A0); PROCESS (A3210, LT, RBI) BEGIN IF (LT = '0') THEN RBO <= '1'; segment <= "1111111"; ELSIF (RBI = '0' AND A3210 = "0000") THEN RBO <= '0'; segment <= "1111111"; ELSIF (RBI = '1' AND A3210 = "0000") THEN RBO <= '1'; segment <= "1111110";

源代码

点击下方的公众号卡片获取

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献11条内容

已为社区贡献11条内容

所有评论(0)