TMS320F280039系列文章之第三章 芯片资源(外设)、存储器映射及加密(代码安全模块CSM)

本文章采用CCS进行DSP(TMS320F280039)系列学习。从零开始,重新学习并记录知识点,同时也是为了方便自身回顾

·

TMS320F280039系列文章目录

第一章 新建工程

第二章 最小系统组成及Boot启动模式

第三章 芯片资源(外设)、存储器映射及加密(代码安全模块CSM)

文章目录

前言

本文章采用CCS12.1.0(CCS软件版本)及C2000Ware_4_01(SDK-设计资源)进行TMS320F280039(DSP芯片)系列学习

- 萌新入坑,如有不对的地方请大佬多多指教,谢谢!->欢迎评论区留言

- 对于萌新来说,学习无非就是多看博文,但是…0.0大佬们的思维大多都有些跳跃,真的很难理解(当然大佬们估计都是为了记录或者提醒自己的工作及学习例程),所以想通过慢慢学习,把每一步都解释出来(保姆版)

第三章 芯片资源(外设)、存储器映射及加密

1.外设资源(外设)

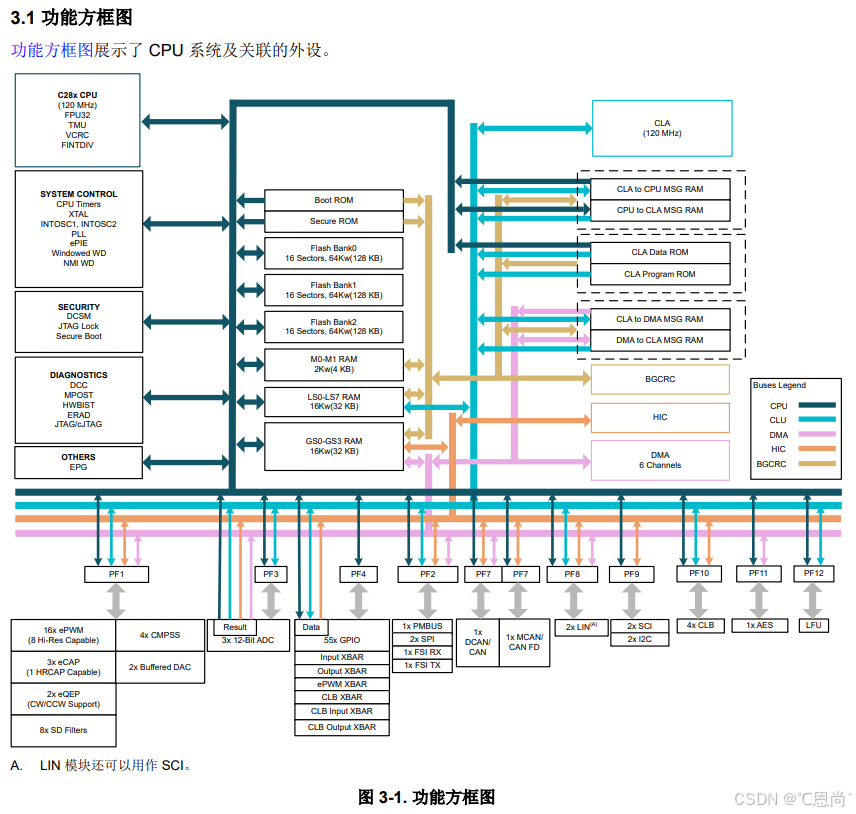

1.1 芯片资源(外设)功能方框图(采用哈佛架构:独立的程序和数据总线)

- 芯片上各资源(外设)通过5大总线与各资源(外设)相连

- CPU总线(中央处理器):程序运行过程中主要使用的程序和数据总线

- CLU总线:主要连接可编程控制律加速器(CLA),实现将并发控制环执行引入C28x系列

- DMA总线(直接内存访问):6通道直接存储器存取(DMA)控制器

- HIC总线:主要连接主机接口控制器(HIC),支持从外部主机访问内部存储器

- BGCRC总线:主要连接背景CRC(BGCRC),实现32 位数据的一个周期CRC运算

1.2 芯片资源(外设)简介(结合功能方框图及Datasheet首页内容)

- TMS320C28x 32位DSP内核(在120MHz下)

- FPU32(IEEE 754 浮点单元):支持快速整数除法(FINTDIV)

- TMU(三角法数学单元):支持非线性比例积分微分(NLPID)控制

- VCRC(CRC 引擎和指令)

- SYSTEM CONTROL(系统控制模块)

- CPU Timers

- XTAL(晶体振荡器或外部时钟输入)

- INTOSC1,INTOSC2(两个内部10MHz振荡器)

- PLL

- ePIE(增强型外设中断扩展)

- Windowed WD(窗口化看门狗计时器模块)

- NMI WD

- SECURITY(安全模块)

- DCSM(用户可配置的双区域安全模块)

- JTAG Lock(锁定)

- Secure Boot

- DIAGNOSTICS(诊断模块)

- DCC(双路时钟比较器)

- MPOST(内存开机自检)

- HWBIST(硬件内置自检)

- 十个硬件断点(包括ERAD:嵌入式实时分析和诊断)

- JTAG/cJTAG

- OTHERS

- EPG(嵌入式图形发生器)

- CLA(可编程控制律加速器)

- 120MHz + IEEE 754 单精度浮点指令 + 独立于主CPU执行代码(独立的、完全可编程的32位浮点数学处理器,能够将并发控制环执行引入C28x系列)

- 通过使用CLA来处理时间关键的控制环,主CPU便可自由执行其他系统任务,如通信和诊断等(CLA的低中断延迟使其能够“及时”读取ADC样本,从而显著减少ADC样本到输出的延迟,以实现更快的系统响应和更高速率的MHz控制环)

- DMA(6通道直接存储器存取控制器)

- HIC(主机接口控制器)

- 支持从外部主机访问内部存储器

- BGCRC(背景CRC)

- 实现32 位数据的一个周期CRC运算

- 存储器(内存)

- 在三个独立存储体上提供 384KB (192KW) 的闪存(ECC保护)

- 69KB (34.5KW) RAM(ECC保护)

- 其他外设(PFx:外设帧x)

- PF1

- 16x ePWM(8 Hi-Res Capable)(16个ePWM通道,包含具有高分辨率功能(150ps 分辨率)的8个通道)

- 集成式死区支持

- 集成式硬件跳匣区域(TZ)

- 3x eCAP(1 HRCAP Capable)

- 在3个eCAP模块中,有一个提供高分辨率捕捉(HRCAP)

- 2x eQEP(CW/CCW Support)

- 两个支持CW/CCW运行模式的增强型正交编码器脉冲模块

- 8x SD Filters(8个Σ-Δ滤波器模块(SDFM)输入通道(每个通道两个并联滤波器))

- 标准SDFM数据滤波

- 用于高估或低估情况下快速操作的比较器滤波器

- 4x CMPSS(4个带12位参考数模转换器(DAC)的窗口比较器)

- 数字干扰滤波器

- 2x Buffered DAC(两个12位缓冲DAC输出)

- 16x ePWM(8 Hi-Res Capable)(16个ePWM通道,包含具有高分辨率功能(150ps 分辨率)的8个通道)

- PF2

- 1x PMBUS(一个电源管理总线接口)

- 2x SPI(2个串行外设接口端口)

- 1x FSI RX(带一个发送器和一个接收器的快速串行接口(最高200Mbps))

- 1x FSI TX(同上)

- PF3

- 3x 12-Bit ADC(三个4MSPS 12 位模数转换器)

- 最多23个外部通道(包括两个gpdac输出)

- 每个ADC具有四个集成后处理块(PPB)

- 3x 12-Bit ADC(三个4MSPS 12 位模数转换器)

- PF4

- 55x GPIO(55个独立可编程多路复用通用输入/输出引脚)

- Input XBAR

- Output XBAR

- ePWM XBAR

- CLB XBAR

- CLB Input XBAR

- CLB Output XBAR

- PF5

- PF6

- PF7

- 1x DCAN/CAN(一个控制器局域网总线端口)

- 1x MCAN/CAN FD(一个具有灵活数据速率的控制器局域网总线端口)

- PF8

- 2x LIN(两个UART兼容的本地互连网络接口)

- LIN模块还可以用作SCI

- 2x LIN(两个UART兼容的本地互连网络接口)

- PF9

- 2x SCI(两个UART兼容的串行通信接口)

- 2x I2C(两个内部集成电路端口)

- PF10

- 4x CLB(可配置逻辑块)

- 4个逻辑块

- 增强现有外设功能

- 支持位置管理器解决方案

- 4x CLB(可配置逻辑块)

- PF11

- 1x AES(高级加密标准加速器)

- PF12

- LFU(实时固件更新)

- 从旧固件到新固件的快速上下文切换

- 缩短了闪存组擦除时间

- LFU(实时固件更新)

2.存储器映射

2.1 存储器的类型

- DSP的CPU本身不含存储器,但它可以访问DSP片内其他地方的存储器或者片外的存储器

2.1.1 程序/数据存储器

- 具有片内单口随机存储器SRAM、只读存储器ROM和Flash存储器

- 1Kx16位的OPT存储器统一映射到程序和数据存储器空间,这样OPT存储器可以用来存放数据或代码,与Flash存储器不同的是它只能被用户写一次,不能再次被擦除

- 它们被映像到程序空间或者数据空间,用以存放执行代码或存储数据变量

2.1.2 保留区

- 数据区的某些地址被保留作为CPU的寄存器使用

2.1.3 CPU中断向量

- 在程序地址中保留了64个地址作为CPU的32个中断向量

2.1.4 Boot ROM

- Boot ROM是出厂时的引导程序

- 在上电时,引导模式信号提供给bootloader软件,用以决定使用何种引导模式。用户可以选择通常的引导模式或者从外部连接下载新程序,亦或选择内部的Flash/ROM引导程序

- Boot ROM还包含有标准的表,比如Sin/Cos波形表,具体的引导模式需要查询数据手册相关表格

2.1.5 代码安全模块CSM(Code Security Module)

- 在开发完程序,将代码烧写进芯片的存储器后,常常会担心别人通过JTAG口从存储器中将代码读出来,为了保护代码安全,DSP设计有代码安全模块CSM

- 受到CSM保护的模块有Flash、OTP、RAM。密码保护的概念应该很好理解,Flash、OTP、RAM这些模块就像是一个保险箱,把代码装载入存储单元之后,就给保险箱设一个密码,当需要再取这些存储单元中的内容时,需要凭密码来打开,只有当输入的密码和之前设置的密码相同时,才能打开保险箱;否则无法打开保险箱,即无法读取存储单元中的内容

2.1.6 外设帧PF

- DSP片内具有3个外设帧PF0,PF1和PF2,专门用于外设寄存器的映像空间

- 除CPU寄存器之外其他寄存器均放在了PF0、PF1、PF2和PF3内,其只限于数据存储,用户程序无法在程序空间访问这些存储空间

2.2 存储器(内存)映射

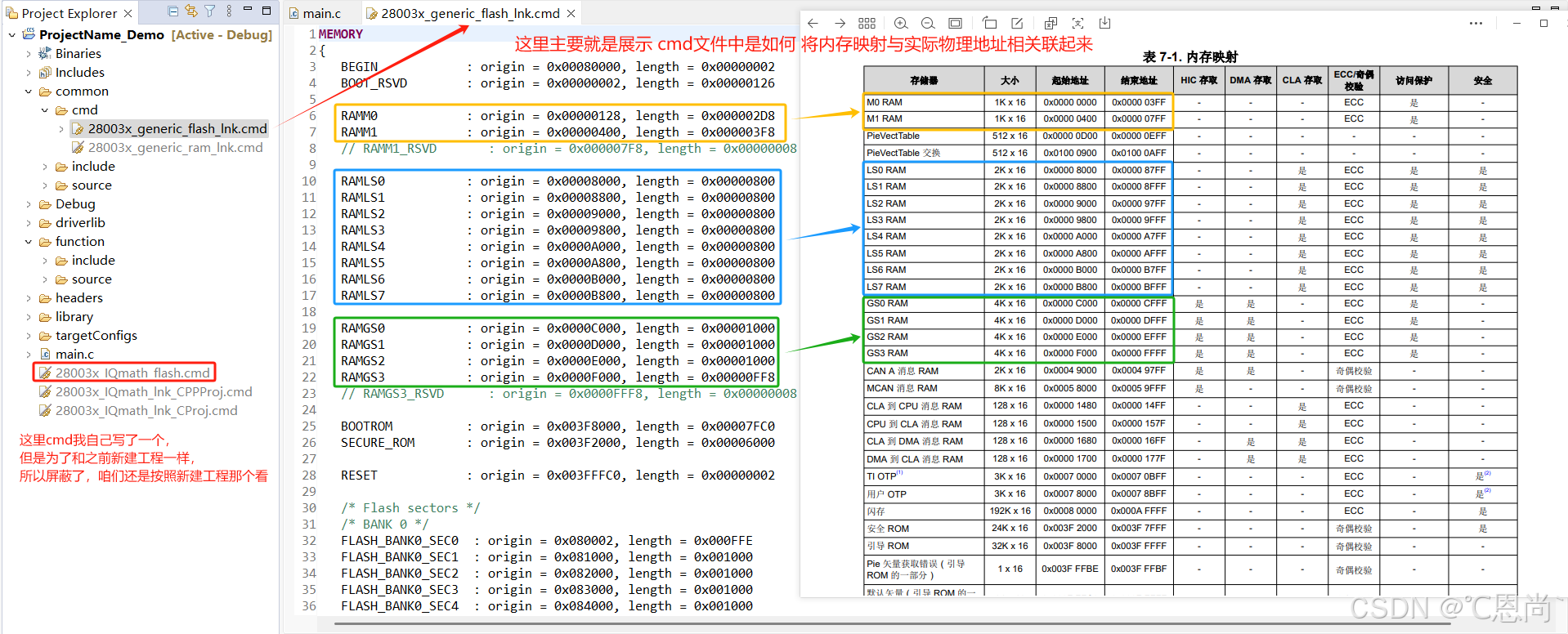

2.2.1 如何理解存储器(内存)映射?(与cmd文件息息相关)

- 概念:存储器映像(Memory Mapping)可以从“统一地址访问”的核心思想入手 —— 它是一种将计算机中所有可被CPU访问的资源(如内存、外设寄存器、ROM、显存等)都映射到同一个连续地址空间的设计方式

- 理解:给每个资源分配一个唯一的“地址编号”,让CPU可以像访问普通内存一样,通过这个编号直接操作所有资源,无需区分“这是内存”还是“这是外设”

- 去快递站取快递(图书馆找书):通过一个取件码(书籍检索号)“即地址映射”,你就知道在哪一个快递(书)架的哪一排找你的快递(书)“即真实的内存地址”

2.2.2 存储器(内存)映射总图

在文档中没有找到类似STM32F407和TMS320F28335 Datasheet的框图,只有表格描述

2.2.2.1 内存控制器模块

- 类型

- 专用RAM专用于CPU:M0、M1内存

- 在CPU和CLA之间共享:LSxRAMS

- 在CPU、DMA和HIC之间共享:GSx内存

- 用于处理器之间的消息发送和接收:MSG内存块

- 特性

- 都具有高度的可配置性,可实现对写入访问和从不同主节点读取访问的控制

- 都启用了ECC功能(包括数据和地址),其中一些存储器还属于安全存储器

- 每个RAM都配备了一个控制器,该控制器负责处理与该RAM相关的访问保护/安全检查和ECC功能

// 配置后的防误写常用操作:

EALLOW; // Enable write protection

// DSP外设相关寄存器配置编码

EDIS; // Disable write protection

2.2.2.2 RAM详解

- 专用RAM(Mx RAM)

- CPU子系统有两个支持ECC功能的专用RAM模块:M0和M1

- 这些存储器是与CPU紧密耦合的小型存储器块(即只有CPU可以访问这些存储器,其他主设备(CLA、DMA或HIC)均无法访问这些存储器)

- 所有专用RAM都具备ECC和访问保护(CPU写入保护/CPU取指保护)功能:通过配置分配给每个子系统的访问保护寄存器中的特定位,可以启用/禁用每个RAM块的各种访问保护功能(DxACCPROT)

- 本地共享RAM(LSx RAM)

- 从CPU、CLA和BGCRC可访问的RAM(LSx RAM),但默认情况下仅专用于CPU,可以通过在LSxMSEL寄存器中配置MSEL_LSx位域来启用CLA访问。此外,当这些存储器在CPU和CLA之间共享时,用户可以通过在LSxCLAPGM寄存器中配置CLAPGM_LSx位域,选择将这些存储器用作CLA程序存储,这样,CPU对被配置为CLA程序存储的所有内存块的访问将被阻止

- 所有本地共享RAM(LSxRAM)都是安全的存储器,并具有ECC功能

- 这些RAM都具有CPU访问保护(CPU写入/CPU获取)功能:通过配置本地共享RAM访问保护寄存器中的特定位,可以启用或禁用每个RAM块的每种访问保护类型

- 本地共享RAM(LSx RAM)功能表

| MSEL_LSx | CLAPGM_LSx | CPUx 允许访问 | CPUx.CLA1 允许访问 | 备注 |

|---|---|---|---|---|

| 00 | X | All | - | LSx内存配置为CPU专用RAM |

| 01 | 0 | All | 数据读取/写入 | LSx内存在CPU和CLA1之间共享 |

| 01 | 1 | 仿真读取/写入 | 仅获取/仿真读取/写入 | LSx内存是CLA1程序内存 |

- 全局共享RAM(GSx RAM)

- 从CPU、HIC、BGCRC和DMA可访问的RAM(GSx RAM)

- 全局共享RAM(GSx RAM)功能表(CPU、HIC和DMA都具有对这些存储器的完全读写访问权限)

| CPU(Fetch) | CPU(读) | CPU(写) | CPU.DMA(读) | CPU.DMA(写) | HIC(读) | HIC(写) |

|---|---|---|---|---|---|---|

| Yes | Yes | Yes | Yes | Yes | Yes | Yes |

- 所有全局共享RAM(GSx RAM)块都具有ECC功能

- 全局共享RAM(GSx RAM)具有不同的访问保护级别(CPU写入/CPU获取/DMA写入/HIC写入):通过配置GSACCPROT寄存器中的特定位来启用或禁用这些保护级别

- GSx RAM块的访问保护配置可以被用户锁定,以防止对该位字段进行进一步更新,用户还可以通过设置GSxCOMMIT寄存器中的特定位字段来永久锁定配置到各个位字段(一旦为特定的GSxRAM块执行了配置,在发出CPU.SYSRS指令之前,该配置将不能再被更改)

- 消息RAM

- 此器件上有两种类型的消息RAM可用于在CPU、CLA和DMA之间共享

- CLA-CPU消息:RAM在CLA和CPU之间共享数据

- 这些RAM块可用于在CPU和CLA之间共享数据(CLA具有对“CLA至CPU MSGRAM”的读写访问权限,且CPU具有对“CPU至CLA MSGRAM”的读写访问权限,CPU和CLA均可对两个MSGRAM进行读取访问)

- CLA-DMA消息:RAM在CLA和DMA之间共享数据

- 这些RAM块可用于在CLA和DMA之间共享数据(CLA具有对“CLA至DMA MSGRAM”的读写访问权限,且DMA具有对“DMA至CLA MSGRAM”的读写访问权限,CLA和DMA均可对两个MSGRAM进行读取访问)

2.2.2.3 cmd文件与存储器(内存)映射的关系

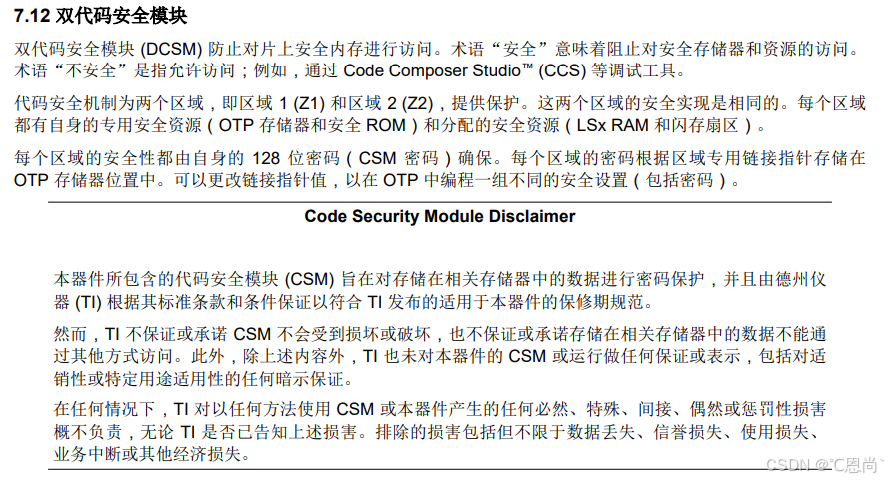

3.存储器加密(代码安全模块-CSM-Code Security Module)

3.1 简介

- 双代码安全模块(DCSM)防止对片上安全内存进行访问

- 术语“安全”意味着阻止对安全存储器和资源的访问

- 术语“不安全”是指允许访问。比如通过 Code Composer Studio"(CCS)等调试工具

- 代码安全机制为两个区域:区域1(Z1)和区域2(Z2)

- 这两个区域的安全实现是相同的

- 每个区域都有自身的专用安全资源(OTP存储器和安全ROM)和分配的安全资源(LSxRAM和闪存扇区)

- 每个区域的安全性都由自身的128位密码(CSM密码)确保

- 每个区域的密码根据区域专用链接指针存储在OTP存储器位置中

- 可以更改链接指针值,以在OTP中编程一组不同的安全设置(包括密码)

- Datasheet截图(TI也不能保证安全性,没事别用)

3.2 应用(看看就行!不要用!会不幸!)

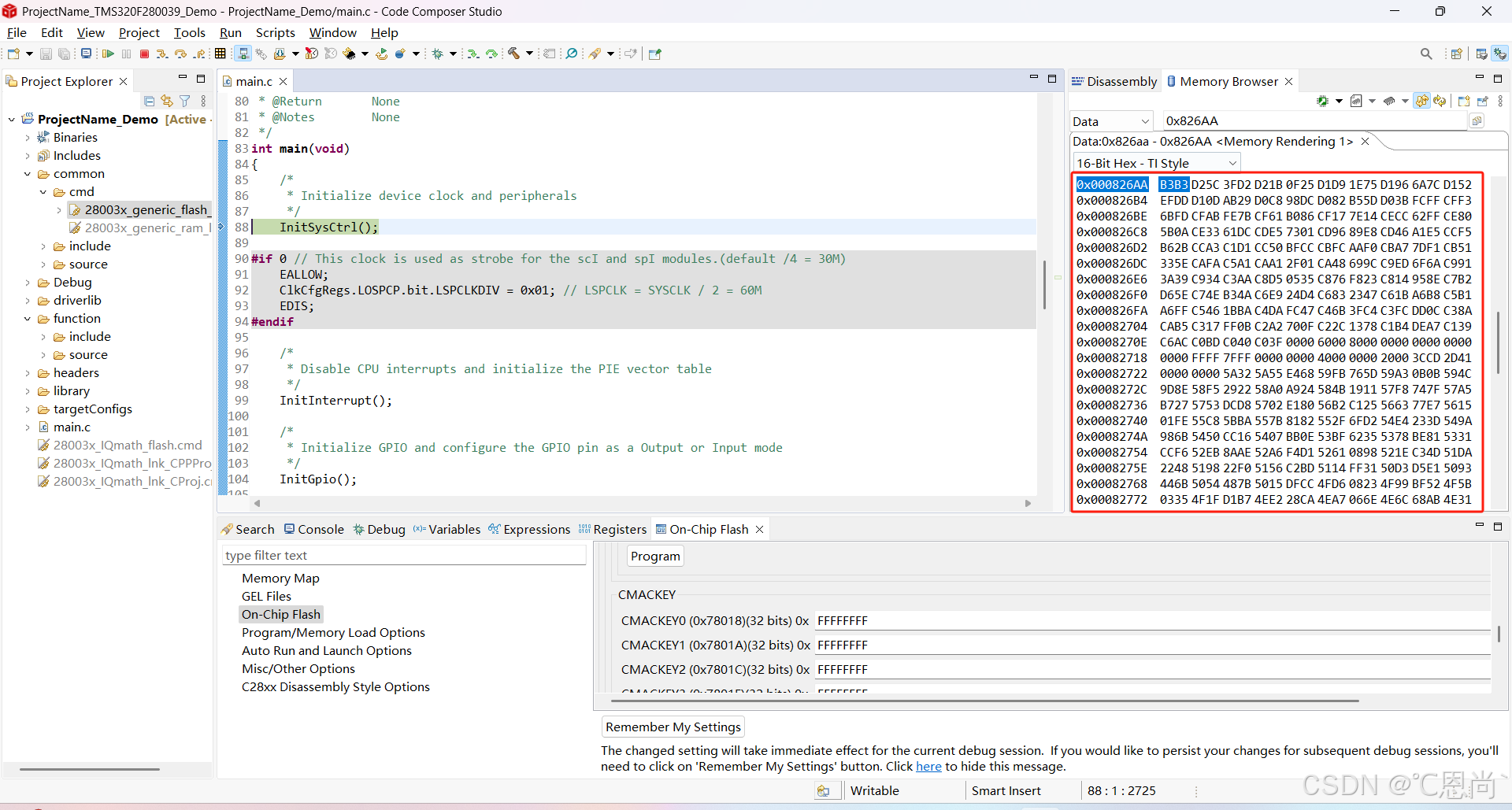

3.2.1 未加密状态(程序可读,即通过某些方法可以破译)

3.2.2 如何加密

- 如3.1简介中所说,它有两个安全区域,两个都可操作,咱们以Z1为例

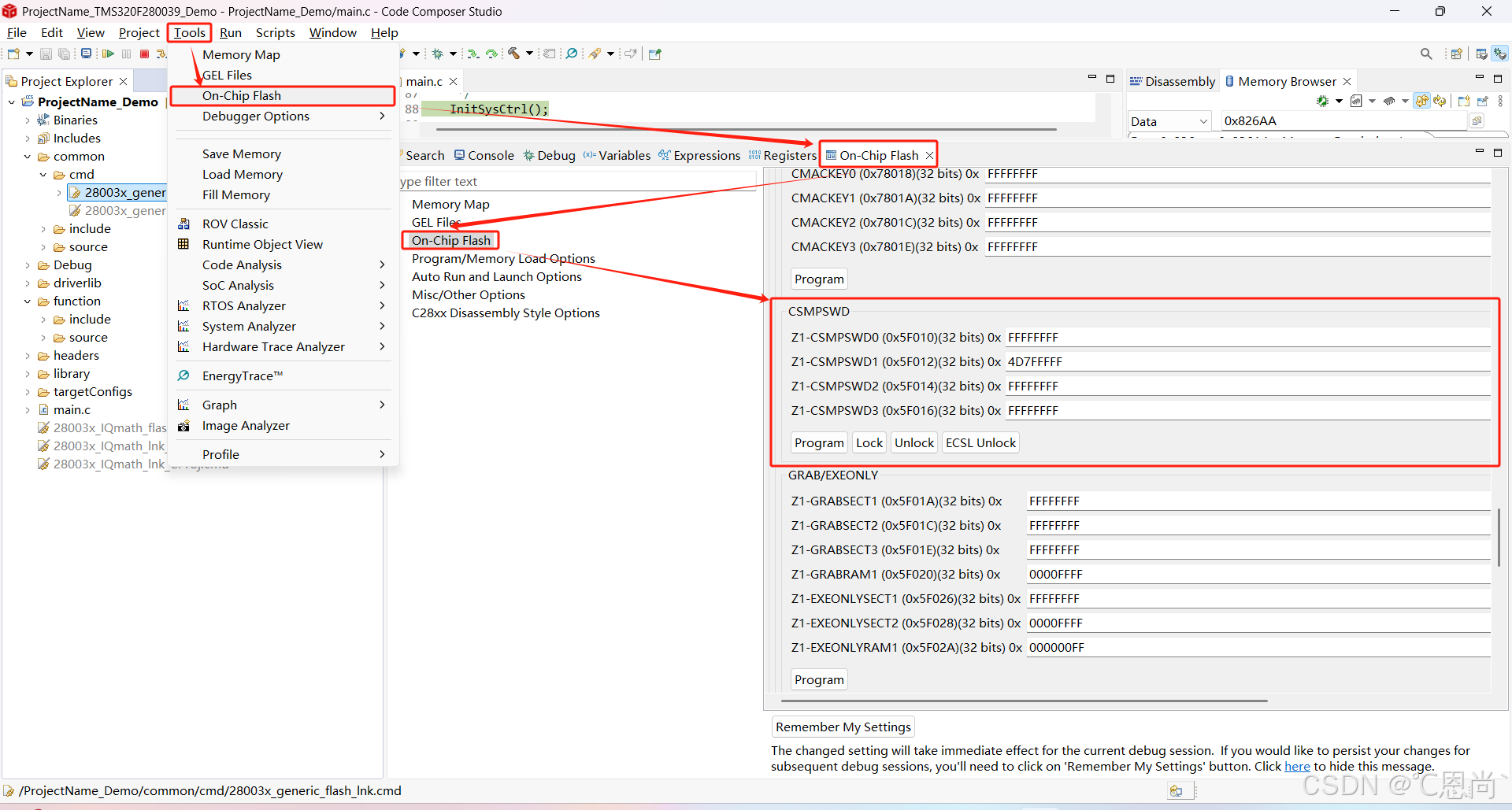

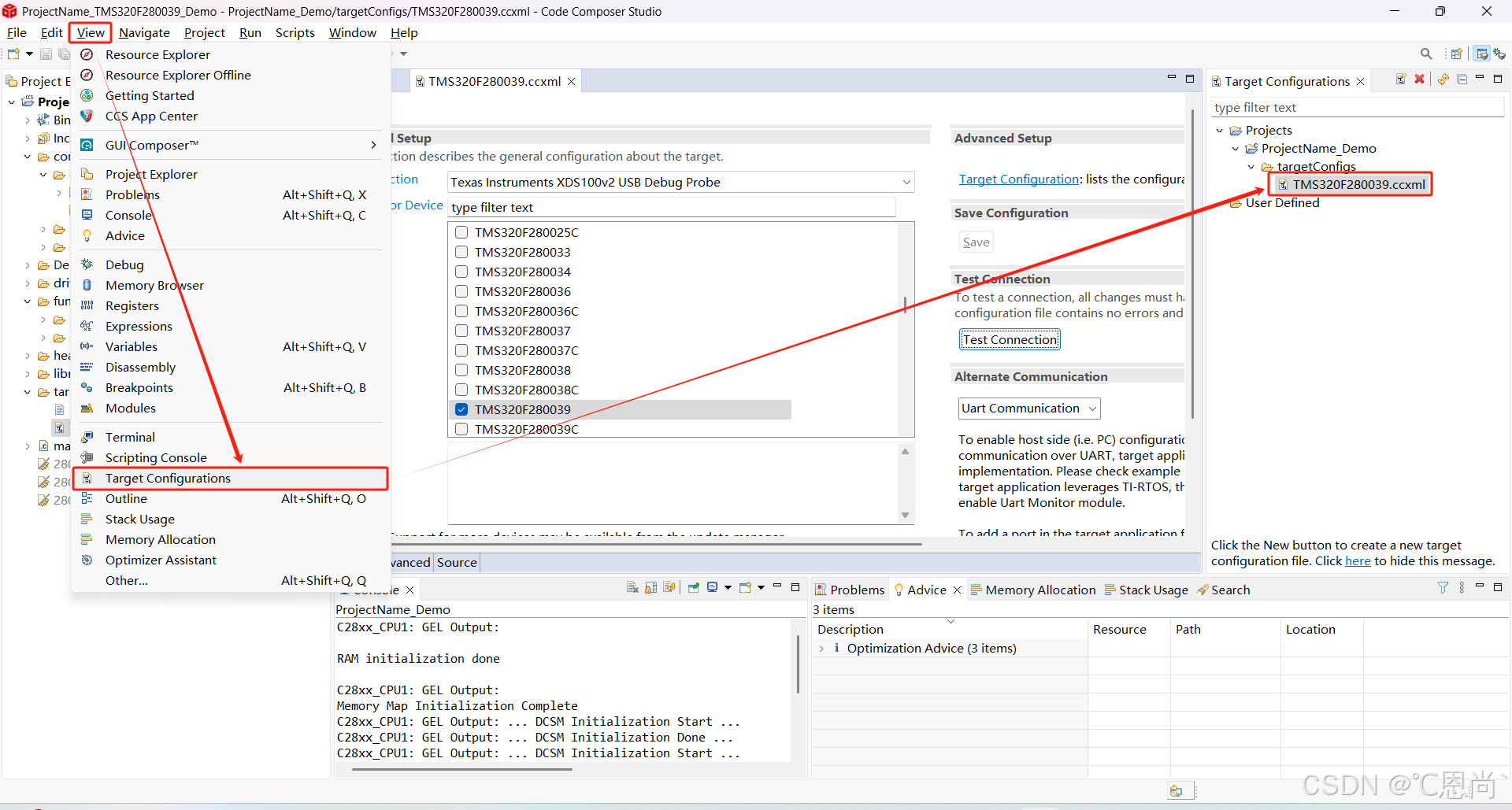

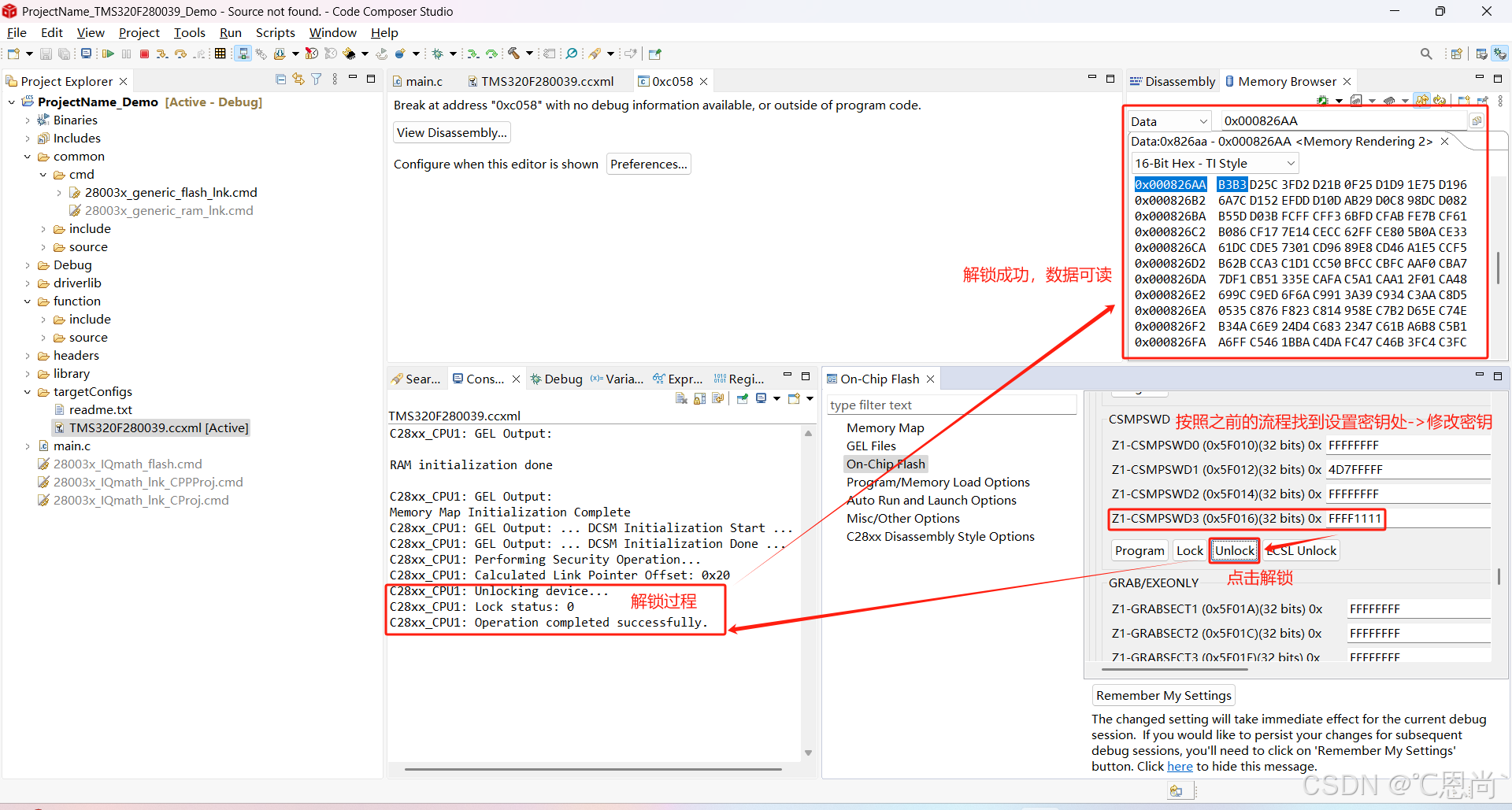

3.2.2.1 进入仿真状态,如图所示找到CSMDSWD

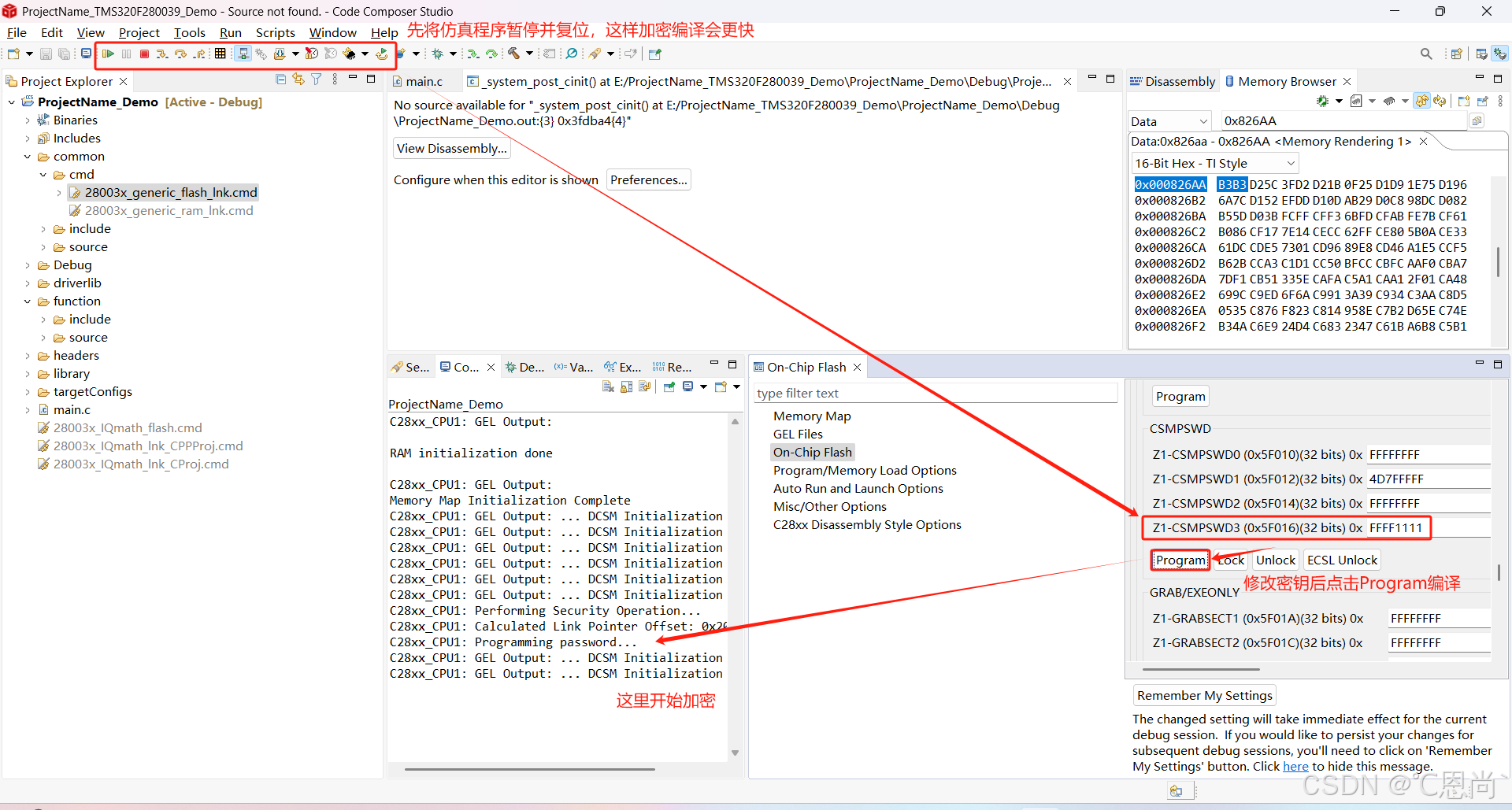

3.2.2.2 修改密钥(原有的不要动!按需修改其他,但不要全设置成0x0000,否则芯片会直接锁死)

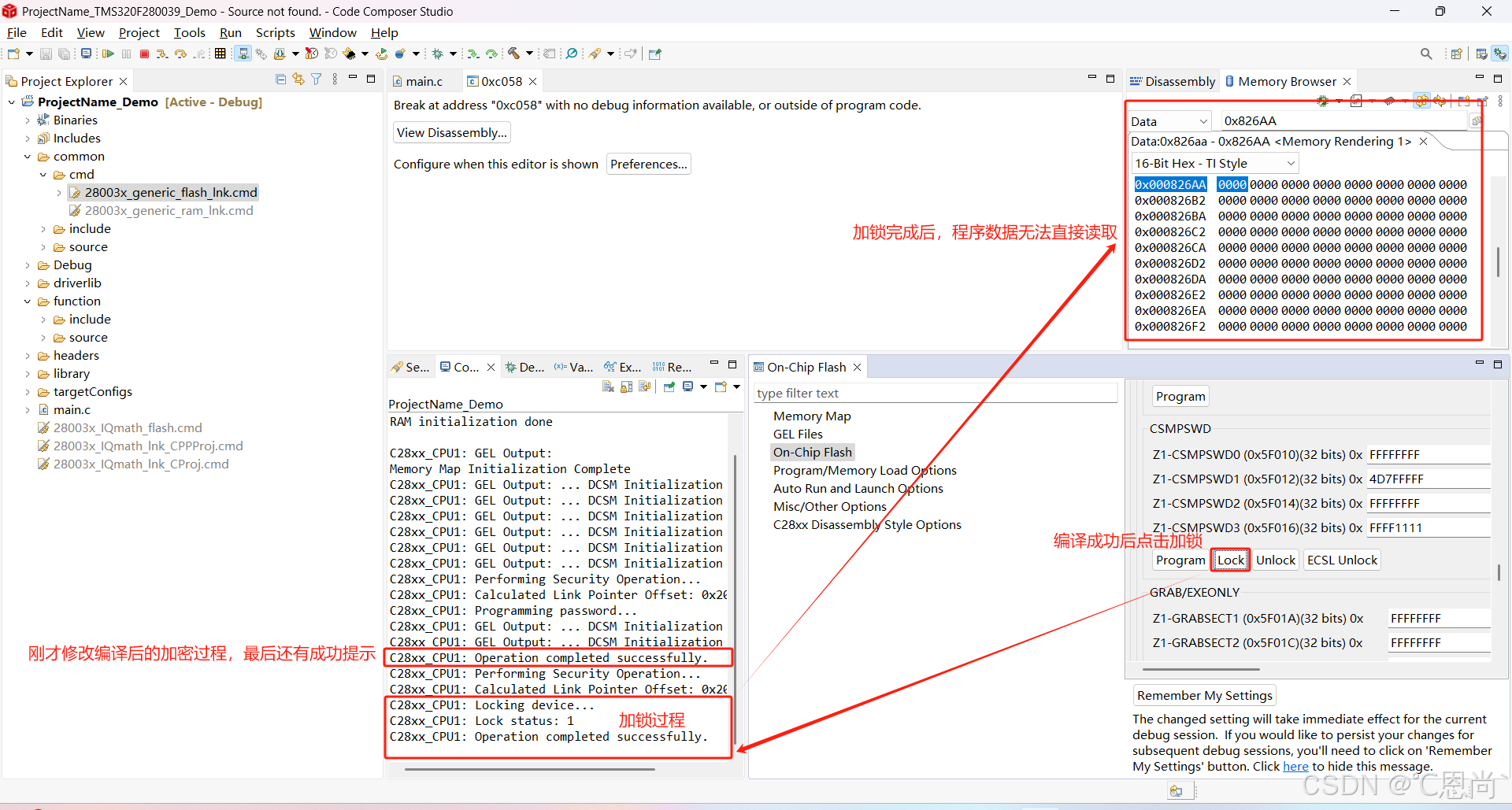

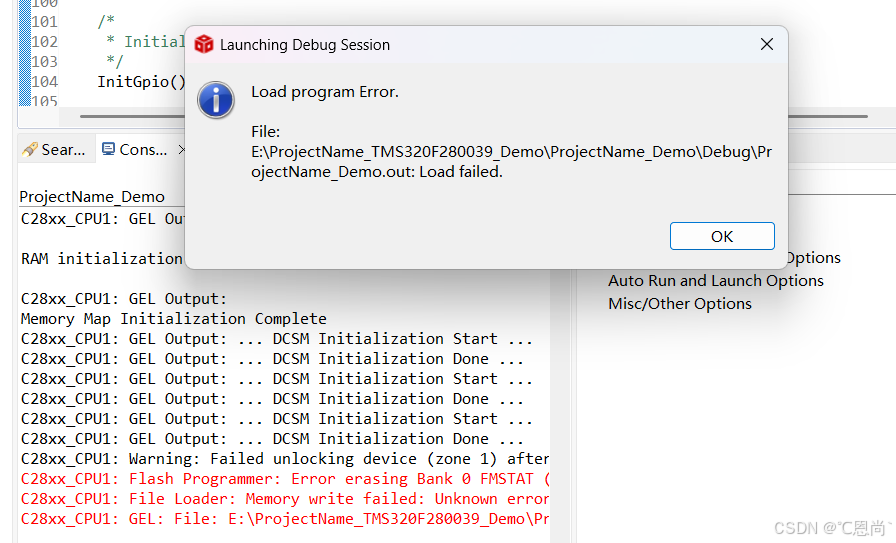

3.2.3 加密状态(程序不可读且无法重新烧录)

- 程序不可读

- 无法重新烧录

3.2.4 如何解密

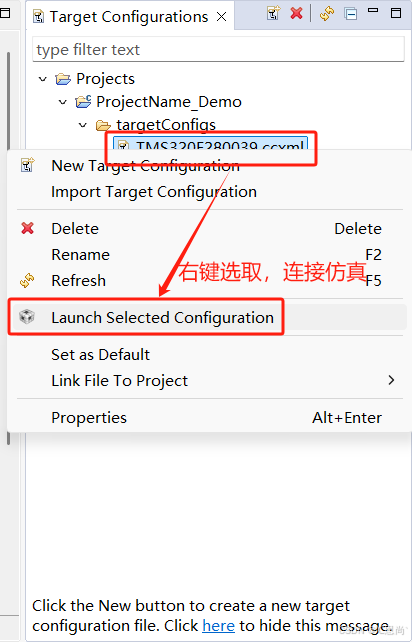

3.2.4.1 连接仿真

- 打开连接仿真按钮

- 右键选取连接仿真器

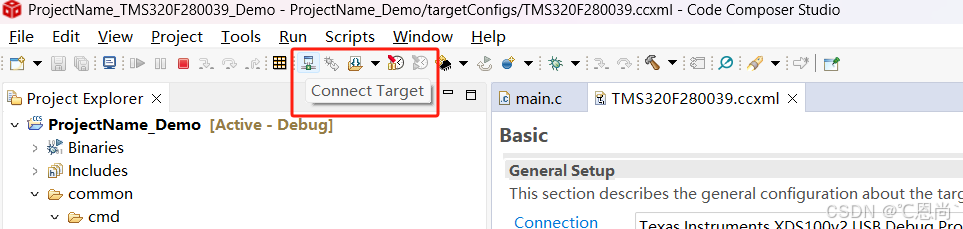

3.2.4.2 连接开发板

3.2.4.3 解锁密钥

3.2.5 解密验证(重新烧写软件查看Memory Browser,可读证明解锁成功)

- hi,真不巧,验证过程走丢了…

总结

本章为TMS320F280039学习系列文章 第三章:芯片资源(外设)、存储器映射及加密(代码安全模块CSM)

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)