使用DDR4控制器实现多通道数据读写(十一)

只有一个主设备,四个从设备,多个主机读写一个从机是通过主机的ID号不同来实现的,每个主机具有不同的ID号,连接到AXI Interconnect RTL IP的从机接口,AXI Interconnect RTL IP的主机接口连接到DDR4。在这里将主机id位宽设置为4,那么作为从机的DDR4的id位宽为8。在interfaces界面中,数据位宽为512位,不进行转换,使用异步时钟,仲裁模式选择轮

Ddr4接口协议为axi4协议,想要实现多通道读写功能,最合适的方式就是使用AXI Interconnect RTL IP核作为连接工具。

一、Interconnect RTL IP核介绍

• 功能特点

o 多主从设备连接:能将多个 Master 模块与多个 Slave 模块连接起来,实现 N Master 与 M Slave 模块间的通信,显著降低了相互间通信的复杂度。

o 总线协议转换:支持多种 AXI 协议标准,如 AXI4、AXI4 - Lite 和 AXI4 - Stream 等,可实现不同协议标准接口之间的数据和指令传输,能在不同速度、不同位宽的 IP 模块之间进行数据交互,完成数据位宽转换、时钟速率转换等功能。

o 数据缓存与 FIFO 功能:内部可实现 FIFO(先入先出队列),能进行数据缓存,支持 Packet mode,有助于解决数据传输中的速度匹配问题,避免数据丢失。同时,还可实现时钟域转换,减少外部干预。

o 共享地址与独立数据通道:采用共享地址通道、独立的多数据通道架构(SAMD)。具有并行 crossbar 读和写通道,在多读写操作时可完全并行,互不干扰,提高了数据传输的效率和灵活性。还能根据配置连接的映射来减少 crossbar 数据路径,进而降低资源使用。

• 工作原理:AXI Interconnect RTL IP 核基于 AXI 总线协议进行工作。AXI 总线包含多个通道,如读地址通道(AR)、读数据通道(R)、写地址通道(AW)、写数据通道(W)和写响应通道(B)。Master 设备通过这些通道向 Slave 设备发送地址、数据和控制信号,Slave 设备则通过相应通道返回数据和响应信号。IP 核内部的逻辑电路负责解析和处理这些信号,根据配置信息将 Master 设备的请求正确路由到对应的 Slave 设备,并将 Slave 设备的响应返回给 Master 设备。

• 应用场景

o 系统集成:用于连接各种不同功能的 IP 模块,如处理器、存储器、外设等,构建一个完整的系统级通信架构,使各模块能够协同工作。

o 通信接口扩展:当需要扩展系统的通信接口数量或连接不同类型的通信接口时,可使用 Interconnect RTL IP 核进行连接和协议转换,实现多种通信接口的集成。

o 数据处理与传输:在数据处理系统中,可将数据从一个处理模块传输到多个不同的处理模块,或者将多个数据源的数据汇集到一个处理模块进行集中处理,能优化数据传输路径,提高数据处理效率。

二、使用vivado建立interconnect RTL IP核

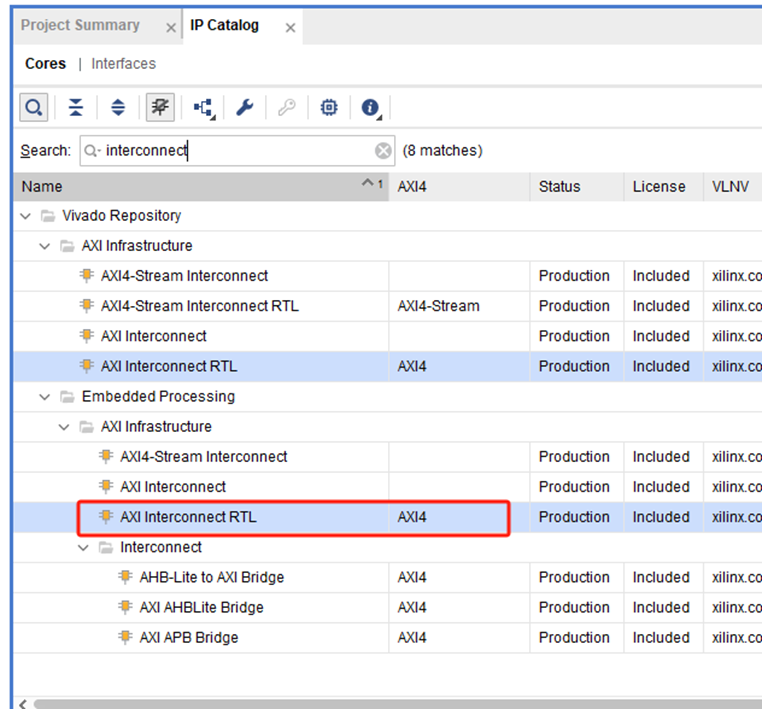

在 IP Catalog搜索框中,搜索interconnect,选中AXI Interconnect RTL。如图所示。

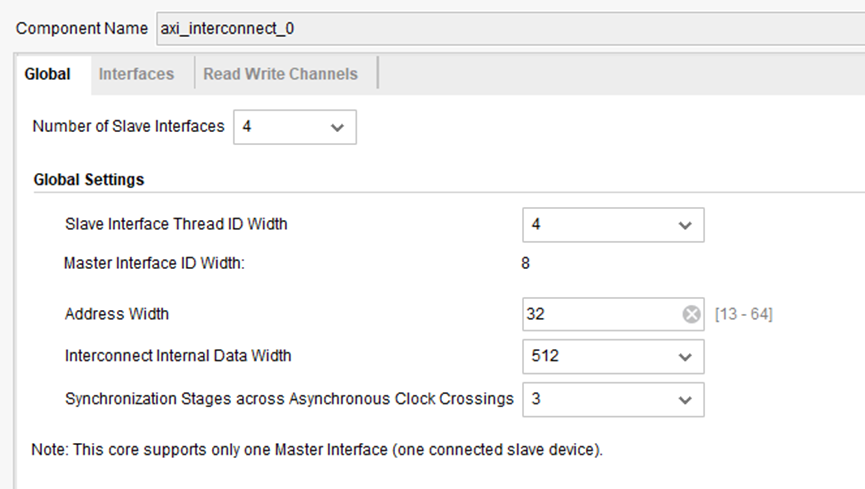

在Global界面,打算实现4个通道同时读写ddr4。选择从机接口数量为4。只有一个主设备,四个从设备,多个主机读写一个从机是通过主机的ID号不同来实现的,每个主机具有不同的ID号,连接到AXI Interconnect RTL IP的从机接口,AXI Interconnect RTL IP的主机接口连接到DDR4。DDR4作为从机,四个读写通道作为主机。每个主机都提供不同的ID号,当多通道同时发出读请求时,AXI Interconnect RTL IP根据id的不同,将读出来的数据传到对应的各个通道。在这里将主机id位宽设置为4,那么作为从机的DDR4的id位宽为8。

地址位宽为32位,数据位宽为512位。Global界面配置如图所示。

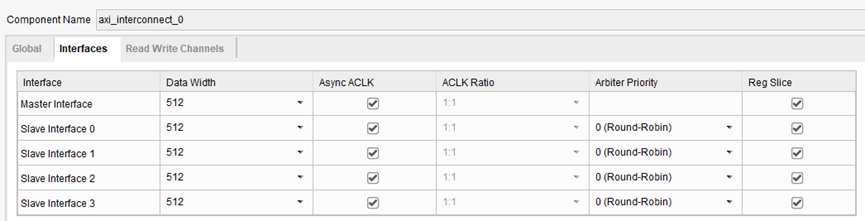

在interfaces界面中,数据位宽为512位,不进行转换,使用异步时钟,仲裁模式选择轮询仲裁,插入寄存器切片,用于解决时序问题,减少时钟域之间的延迟,并确保数据在跨时钟域传输的正确性。配置如图所示。

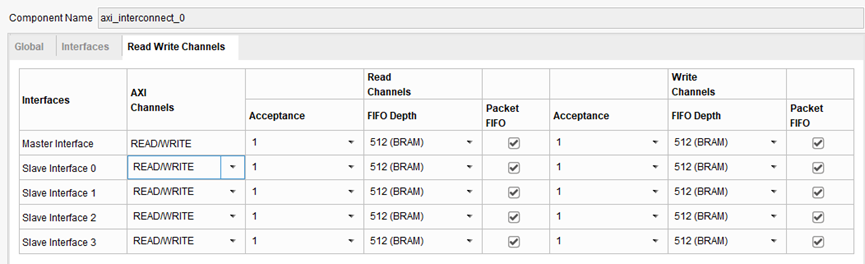

Acceptance表示该接口可以同时容纳读写请求的数量。在这里设置1,使用fifo缓存功能,用于缓存不同速率的数据。启用包模式,当fifo中有空余深度能存下整个请求包时,再开始传输。这样可以保证读写数据包的完整性。配置如图所示。

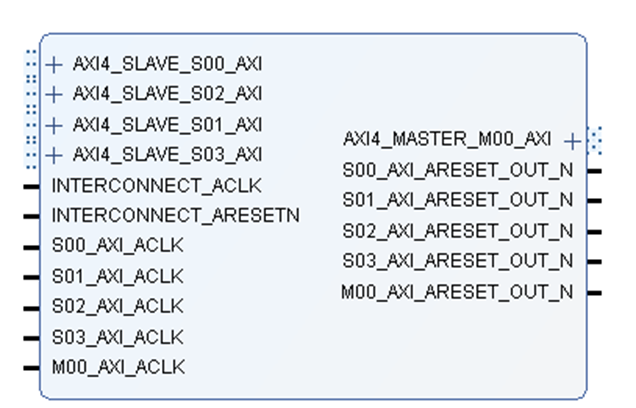

配置完AXI Interconnect RTL IP后,IP接口如图所示。有4个axi从接口,1个axi主接口。分别连接到外部的四个读写通道和一个ddr4接口。

三、AXI Interconnect RTL IP核接口

配置完的IP拥有4个axi4_slave接口和一个axi4_master接口。4个axi4_slave接口对应于4个读写通道。1个axi4_master接口对应于DDR4的axi4接口。

INTERCONNECT_ACLK和INTERCONNECT_ARESETN为AXI Interconnect RTL IP核的时钟和复位信号。四个读写通道可以使用四个不同的时钟,来实现4个不同时钟域下同时读写DDR4,读写通道的复位信号则由IP核提供。MOO_AXI_ACLK为DDR4的用户时钟,M00_AIX_ARESET_OUT_N则为DDR4的AXI接口的复位信号。

四、本章总结

本章节介绍了AXI Interconnect RTL IP核的功能特点、工作原理和应用场景,并详细介绍了IP核的应用配置。下一章节来用仿真观察四个通道同时读写DDR4内存的时序,

本文章由威三学社出品

对课程感兴趣可以私信联系

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献10条内容

已为社区贡献10条内容

所有评论(0)