计算机系统结构知识点讲义第十一讲——流水线的基本概念

流水线技术通过时间并行性显著提升了计算机系统的性能,但其设计需权衡吞吐率、延迟与硬件复杂度。

·

一、什么是流水线?

1. 基本定义

流水线(Pipeline)是一种将重复的时序处理过程分解为若干子过程,通过时间重叠的并行执行来提高系统吞吐率和效率的技术。其核心思想借鉴工业生产流水线,通过功能段(Stage)的划分与并行操作,实现任务处理速度的指数级提升。

2. 核心要素

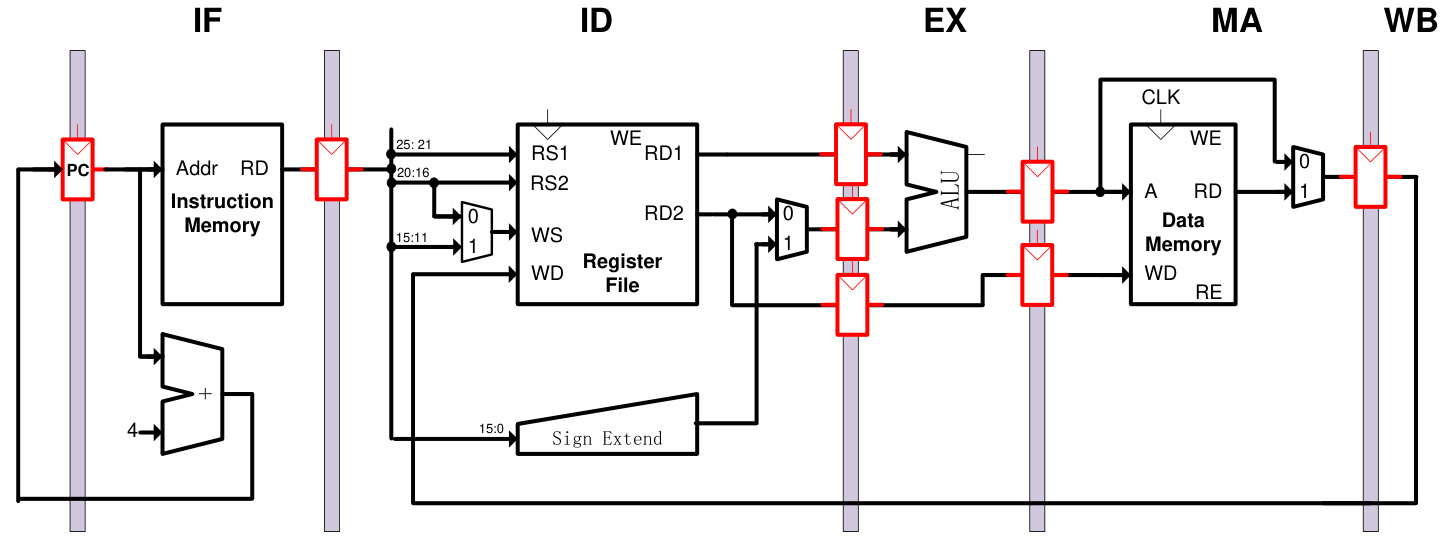

- 功能段划分:将完整任务分解为多个子过程(例如指令流水线的取指、译码、执行、访存、写回五级),每个阶段由独立硬件模块实现。

- 缓冲寄存器(锁存器) :位于各功能段之间,用于隔离不同阶段的数据流,保证并行执行时的数据完整性。

- 流水线周期:由最长的功能段执行时间决定,称为瓶颈段,需通过细分或重复设置来优化。

- 时空图表示:通过时间轴与空间轴展示各功能段的占用状态,直观反映并行性。

3. 工作原理

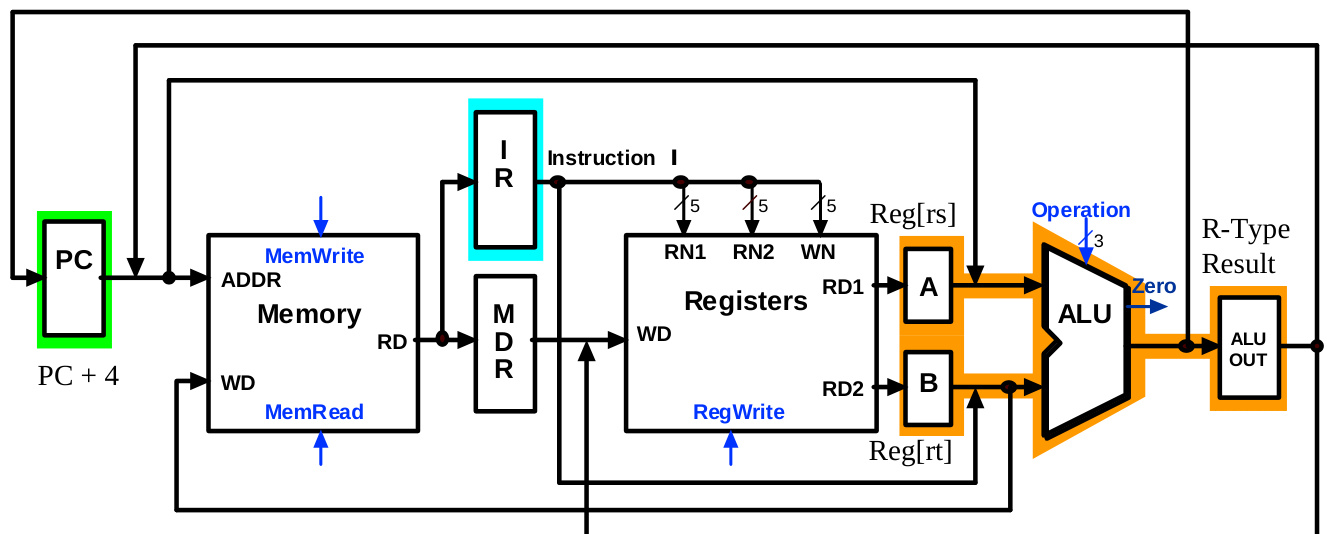

以MIPS五级流水线为例:

- 取指(IF) :从指令存储器读取指令。

- 译码(ID) :解析指令并读取寄存器操作数。

- 执行(EX) :通过ALU完成算术/逻辑运算。

- 访存(MEM) :访问数据存储器。

- 写回(WB) :将结果写回寄存器文件。

每条指令在不同时间进入流水线,通过阶段重叠实现指令级并行(ILP)。例如,当第一条指令处于EX阶段时,第二条指令可同时处于ID阶段,第三条指令处于IF阶段。

4. 关键参数

- 吞吐率(TP) :单位时间完成任务数,TP=n/T,其中n为任务总数,T为总时间。

- 加速比(S) :流水线相对于非流水线的速度提升,S=T非流水/T流水。

- 效率(η) :功能段时空区的利用率,η=有效工作时间总时间。

二、流水线的分类

1. 按处理级别划分

| 类别 | 定义 | 实例 |

|---|---|---|

| 部件级流水线 | 在算术逻辑部件内部细分操作(如浮点加法分为求阶差、对阶、尾数加、规格化) | 浮点加法器流水线 |

| 处理机级流水线 | 将指令处理过程划分为多个阶段(如取指、译码、执行) | MIPS五级指令流水线 |

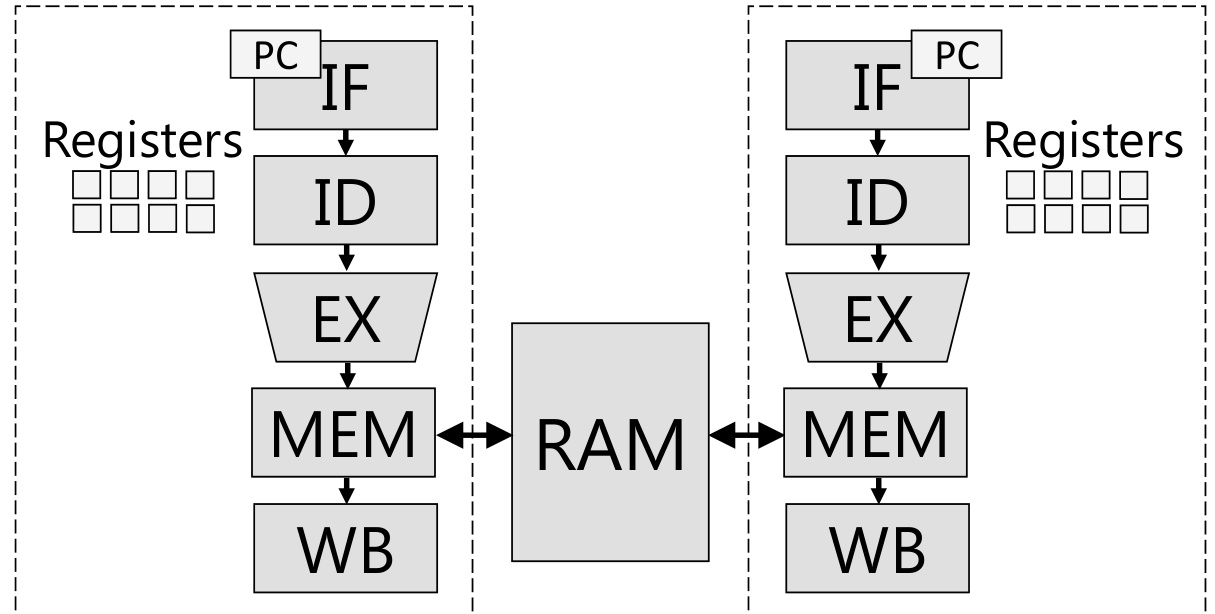

| 系统级流水线 | 多台处理机串行处理同一数据流(如分布式系统中的任务流水) | 多处理机协同的图像处理流水线 |

2. 按功能划分

| 类别 | 特点 | 应用场景 |

|---|---|---|

| 单功能流水线 | 仅支持单一固定功能(如专用乘法流水线) | 数字信号处理器(DSP)中的专用运算单元 |

| 多功能流水线 | 可通过配置支持多种功能(如动态切换浮点加/乘操作) | 通用CPU中的ALU流水线,支持多种指令类型 |

3. 按工作方式划分

| 类别 | 特点 | 优势与限制 |

|---|---|---|

| 静态流水线 | 同一时间段内仅执行一种功能,需重新配置后才能切换功能 | 硬件设计简单,但灵活性低 |

| 动态流水线 | 支持多功能同时执行(如浮点加与整数乘并行) | 提升资源利用率,但需复杂冲突解决机制(如Tomasulo算法) |

4. 按结构划分

| 类别 | 特点 | 典型架构 |

|---|---|---|

| 线性流水线 | 各阶段严格顺序执行,无反馈或资源复用 | 单发射RISC流水线(如ARM Cortex-M系列) |

| 非线性流水线 | 存在反馈回路或资源复用(如循环展开优化中的迭代控制) | 向量处理器中的循环流水线,支持数据重用 |

5. 按任务顺序划分

| 类别 | 特点 | 应用场景 |

|---|---|---|

| 顺序流水线 | 任务流出顺序与流入顺序一致,保证指令执行顺序性 | 简单嵌入式处理器(如8051) |

| 乱序流水线 | 允许任务按数据就绪顺序流出(通过重排序缓冲ROB实现) | 高性能CPU(如Intel Core系列、AMD Ryzen) |

三、流水线技术的关键挑战

-

冲突问题:

- 结构冲突:资源争用(如访存与取指竞争同一总线),通过增加资源副本解决。

- 数据冲突:RAW(写后读)、WAR(读后写)、WAW(写后写),通过旁路(Bypassing)或换名(Renaming)技术缓解。

- 控制冲突:分支预测错误导致流水线清空,采用动态分支预测(如两级自适应预测器)降低惩罚。

-

额外开销:

- 流水寄存器延迟(约占总周期时间的10%-20%)。

- 时钟偏移与同步问题,需精密时序设计。

四、总结

流水线技术通过时间并行性显著提升了计算机系统的性能,但其设计需权衡吞吐率、延迟与硬件复杂度。随着超标量(Superscalar)和超流水线(Super Pipeline)技术的发展,现代处理器已能实现更高层次的指令级并行。理解流水线的基本概念与分类,是掌握计算机体系结构优化与并行计算的关键基础。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献16条内容

已为社区贡献16条内容

所有评论(0)