芯片设计中的RTL是什么含义?

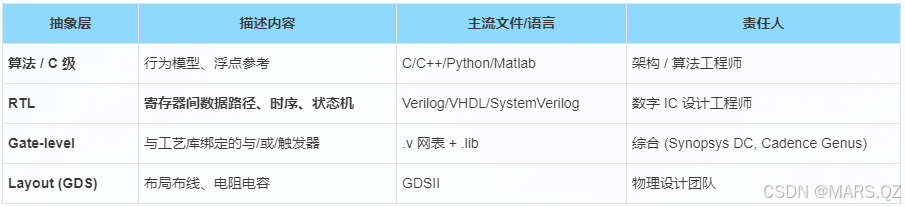

RTL(寄存器传输级)是芯片设计的关键抽象层,使用Verilog/VHDL等硬件描述语言编写。它定义时钟驱动的寄存器之间的数据处理流程,通过综合工具转换为门级网表。RTL设计包含寄存器、组合逻辑和时钟约束,确保时序正确性。与顺序执行的软件不同,RTL描述的是并行硬件网络。示例展示了48位DMA地址生成器的RTL实现,说明硬件能力由RTL设计决定。最终RTL固化的硬件结构只能由软件通过寄存器配置使用

·

在数字电路/芯片设计语境里,RTL(Register-Transfer Level)是一种抽象层次(level of abstraction),用来描述 时钟驱动的寄存器之间如何传递和处理数据。设计者通常用 Verilog、SystemVerilog、VHDL 这类硬件描述语言(HDL)编写 RTL 代码,然后交给综合器(synthesis tool)转换成门级网表,最终再流片成硅。

RTL 的核心概念

- 寄存器 (Register) 被时钟沿锁存 的触发器阵列,存放状态。

- 组合逻辑 (Combinational Logic) 寄存器输出 → 逻辑门 → 计算 → 下一拍被寄存器采样。

- 时钟周期 “Register ↔ Register” 之间路径的最长延迟必须 < 时钟周期,以确保正确时序。

- 同步复位 / 异步复位 控制寄存器初始状态。

RTL 代码 = 用 always@posedge clk {...} / process(clk) 形式把这些东西写出来。

与软件“驱动代码”的区别

- C/汇编 = 顺序执行; RTL = 并行硬件网络,每拍同时处理成千上万位。

- pci_set_dma_mask() 之类函数只是写寄存器,它们不改变 RTL; RTL 位宽(如 DMA 引擎地址寄存器是 32 位还是 64 位)由硬件设计时在 Verilog 里早已定好,软件只能“遵守”或“避让”。

小例子:简化 DMA 读地址计数器

// RTL 示例:48-bit DMA 地址递增 module dma_addr_gen ( input clk, input rstn, input start, input [47:0] base_addr, input [15:0] pkt_len, output [47:0] dma_addr, output valid ); reg [47:0] addr_r; reg vld_r; always @(posedge clk or negedge rstn) begin if (!rstn) begin addr_r <= 48'd0; vld_r <= 1'b0; end else if (start) begin addr_r <= base_addr; vld_r <= 1'b1; end else if (vld_r) begin addr_r <= addr_r + pkt_len; // 48-bit 运算 ! end end assign dma_addr = addr_r; assign valid = vld_r; endmodule

这里把地址寄存器定义成 48 位,在综合之后就成为真正的 48-bit 加法器和触发器阵列——这就是“RTL 决定硬件能力”的直观例子。

小结

- RTL(Register-Transfer Level) 是芯片设计流程中的核心描述层,用 Verilog/VHDL 定义 寄存器→组合逻辑→寄存器 的数据流和时序。

- 软件(驱动、固件)只能通过读写寄存器配置/使用这些已经用 RTL 固化下来的硬件通路,无法在运行时改变其位宽或结构。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)