深入解析计算机内存地址体系:逻辑地址、物理地址与虚拟内存的终极指南

计算机内存地址体系是操作系统与硬件协同管理的核心机制,涵盖逻辑地址、物理地址、虚拟内存及主存与外存的协作。

·

一、核心概念定义与作用

1. 逻辑地址(Logical Address)

- 定义:程序编译后生成的地址,又称相对地址或虚拟地址(部分文献中)。它是相对于程序起始位置的偏移量,与物理内存位置无关。

- 特点:

- 编译时从0开始编址:例如,C语言程序中

main()函数的局部变量int a;的逻辑地址可能为0x08048000。 - 进程间可重复性:不同进程的

main()函数可能共享相同的逻辑地址(如0x08048000),但通过页表隔离访问。 - 由CPU生成:程序员通过指针、数组索引等直接操作逻辑地址(如

*p = 5)。

- 编译时从0开始编址:例如,C语言程序中

- 误区澄清:

❌ 逻辑地址=物理地址 → 早期单道程序系统中成立,现代多道程序系统中需通过MMU转换。

2. 物理地址(Physical Address)

- 定义:内存条上电路单元的实际位置,是逻辑地址经转换后的最终结果。

- 作用:CPU通过地址总线访问物理内存的唯一标识。

- 关键点:

- 共享性:物理地址空间为所有进程共享,操作系统通过MMU和页表隔离进程访问。

- 与网络地址无关:物理地址(如内存地址)与网络中的MAC地址(硬件设备标识)无关,后者是网络层的概念。

3. 虚拟内存地址(Virtual Memory Address)

- 定义:操作系统为进程抽象的连续地址空间(32位系统为4GB,64位更大),与实际物理内存解耦。

- 核心机制:

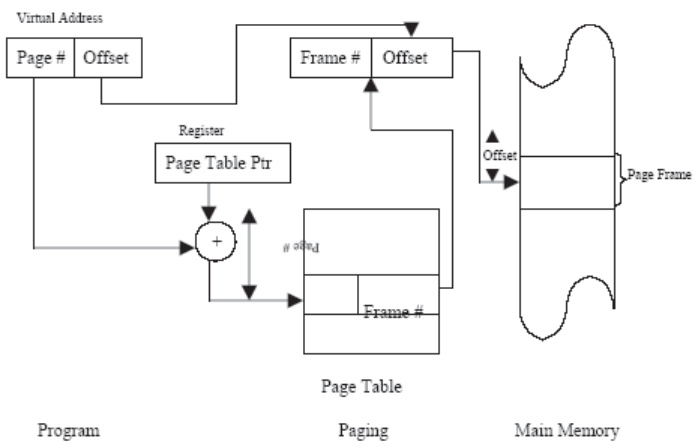

- 分页:虚拟地址拆分为页号(Page Number)和页内偏移(Page Offset),通过页表映射到物理页帧。

- 示例:32位地址中,高20位为页号,低12位为偏移量(页大小4KB)。

- 页表(Page Table) :存储虚拟页→物理页帧的映射关系,由MMU管理。

- TLB(快表) :缓存近期页表项,加速地址转换。

- 虚拟内存的实现:

- 分页机制:通过页表将虚拟页映射到物理页帧,解决物理内存不足问题。

- 交换空间:外存(硬盘/SSD)作为交换区,将暂时不用的页换出到磁盘,减少物理内存占用。

4. 主存(内存)与外存(辅存)

| 特性 | 主存(RAM) | 外存(硬盘/SSD) |

|---|---|---|

| 速度 | 纳秒级,直接供CPU访问 | 毫秒级,需通过I/O接口传输 |

| 易失性 | 断电数据丢失 | 非易失性,长期保存 |

| 容量 | 较小(GB级) | 较大(TB级) |

| 作用 | 存储正在运行的程序和临时数据 | 长期存储程序与数据 |

| 联系 | 虚拟内存依赖外存作为交换空间(Swap),将暂时不用的页换出到磁盘。 |

二、地址转换流程详解

以分页机制为例(现代OS主流方案):

2.1 线性地址的计算

- 逻辑地址 → 线性地址:

在平坦模型下,逻辑地址(编译生成的偏移量)直接作为线性地址。例如,C语言程序中main()函数的局部变量int a;的逻辑地址可能为0x08048000。- 公式:线性地址 = 段基址 + 段内偏移(Linux等系统中段基址通常为0)。

2.2 TLB加速地址转换

- TLB(Translation Lookaside Buffer):

- 作用:高速缓存最近使用的页表项(PTE),通过快速查找TLB而非遍历多级页表,显著减少地址转换延迟。

- 命中流程:

- CPU生成逻辑地址(如

0x0804A000); - MMU解析出页号(

0x0804A)和页内偏移(0x000); - 查询TLB:

- 命中:直接从TLB获取物理页帧号(如

0x12345),物理地址 =0x12345000; - 未命中:需访问主存中的页表,进一步查找物理页帧号。

- 示例:在80386架构中,TLB通过缓存虚拟页号和物理页帧号的映射,加速地址转换。

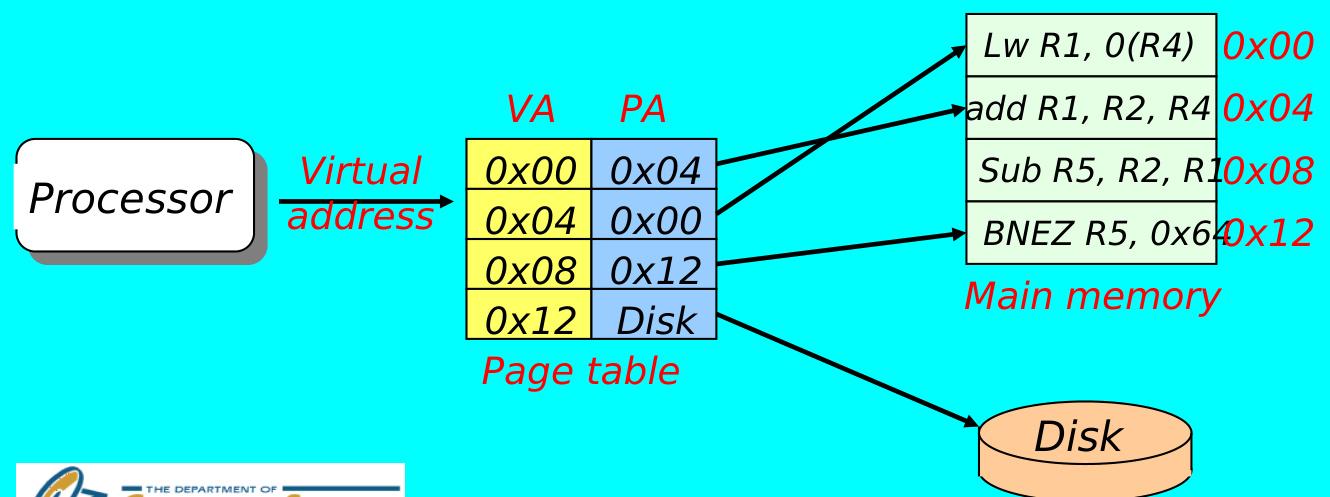

2.3 缺页中断(Page Fault)处理

- 触发条件:

当访问的虚拟页未被映射到物理内存时,触发缺页中断。例如,当TLB未命中且页表中无对应页表项时。

处理流程:

1.页表查找:

- 通过页表(Page Table)获取物理页帧号(如

0x5000); - 检查页表项的有效位(Present Bit):若为0,触发缺页中断。

2. 缺页处理:

- OS操作:

- 从外存(Swap)加载所需页到物理内存;

- 更新页表,将新页的物理页帧号写入目标页表项。

- TLB更新:将新页表项缓存到TLB,加速后续访问。

3. 重试访问:

- 重新执行引发缺页的指令,此时虚拟地址已映射到物理内存,访问成功。

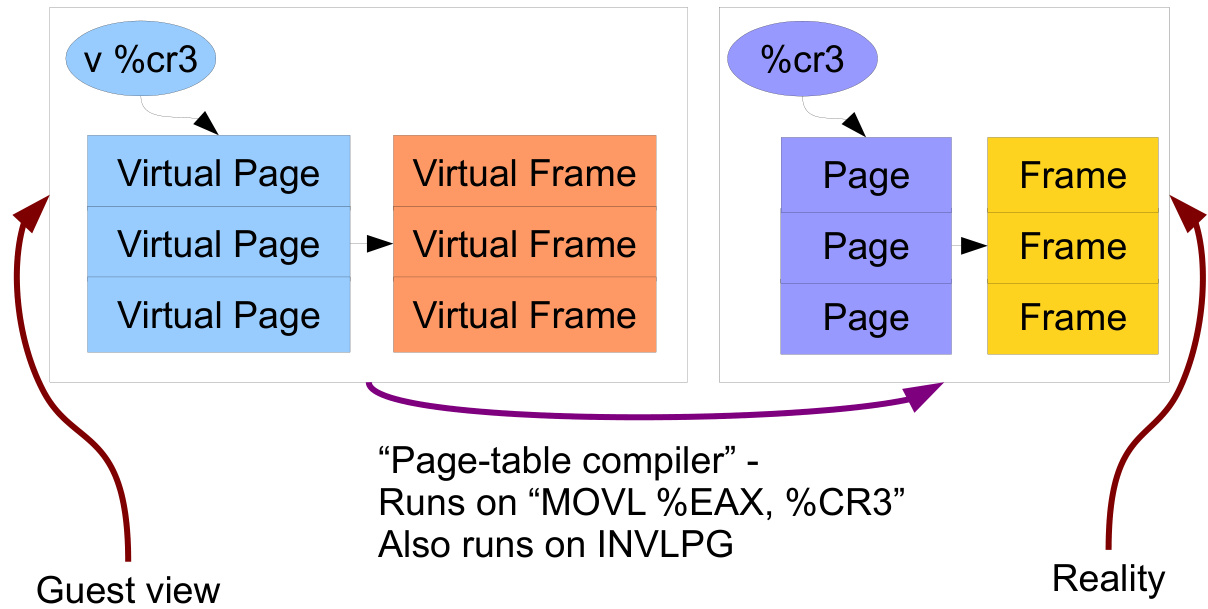

2.4 多级页表与TLB协作

- 分层映射:

- 现代系统采用多级页表(如三级页表)优化内存使用。例如,RISC-V的Sv39方案通过三级页表支持超大页(Huge Page)映射。

- 示例:

- 一级页表映射虚拟页号到二级页表的起始地址;

- 二级页表再映射到三级页表,最终指向物理页帧。

- TLB缓存策略:

- TLB通过缓存近期使用的页表项,减少对主存页表的访问。例如,Linux内核在分配物理内存时,会将新页表项缓存到TLB。

2.5 常见误区与注意事项

- 误区1:TLB总是命中

- 正解:TLB命中率取决于程序局部性。例如,随机访问模式可能导致低命中率。

- 误区2:缺页中断必然导致性能下降

- 正解:虚拟内存通过预取和缓存策略(如预加载常用页)可减少缺页频率,但频繁缺页(Thrashing)仍会显著拖慢性能。

三、虚拟内存与物理内存的映射关系

3.1 页表的核心作用

页表是虚拟内存管理的核心组件,其核心作用包括:

- 虚拟页到物理页帧的映射:

页表通过记录虚拟页号(VPN)与物理页帧号(PPN)的对应关系,实现虚拟地址到物理地址的转换。例如,虚拟页0x1000可能映射到物理帧0x5000。 - 访问权限控制:

每个页表项(PTE)包含控制位,用于定义虚拟页的访问权限:- 存在位(Present Bit) :指示该虚拟页是否已映射到物理内存(如中页表条目中的有效位)。

- 访问权限位:包括读(R)、写(W)、执行(X)等标志,例如RISC-V架构中的

XD位(禁止执行)。 - 修改位(Dirty Bit) :标记虚拟页是否被修改过,用于决定是否需要将数据写回磁盘。

- 存在位(Present Bit) :指示该虚拟页是否已映射到物理内存(如中页表条目中的有效位)。

3.2 缺页中断(Page Fault)的处理流程

当访问的虚拟页未被映射到物理内存时,触发缺页中断(Page Fault),其处理流程如下:

- 触发中断:

CPU检测到虚拟地址未命中页表,立即触发Page Fault异常。 - 页面调度:

操作系统(OS)从磁盘加载所需页到物理内存,并更新页表中的映射关系。- 置换策略:选择当前最少使用的物理页帧(如提到的“最少使用页帧”),将其写入磁盘并释放。

- 页表更新:将新页的物理页帧号写入目标页表项。

- 重试访问:

OS重新执行引发Page Fault的指令,此时虚拟地址已映射到物理内存,访问成功。

3.3 页表的层级结构与扩展

现代操作系统采用多级页表(如三级页表)优化内存使用:

- 分层映射:

- 一级页表映射虚拟页号到二级页表的起始地址,二级页表再映射到三级页表,最终指向物理页帧(如所述)。

- 例如,RISC-V架构的Sv39方案通过三级页表支持超大页(Huge Page)映射。

- TLB缓存:

页表项(PTE)的访问由内存管理单元(MMU)通过快表(TLB)加速,减少物理页表查找开销。

4.4 虚拟内存与物理内存的协作机制

- 主存与外存的协同:

虚拟内存依赖外存(硬盘/SSD)作为交换空间(Swap),将暂时不用的页换出到磁盘,从而扩展物理内存的容量。

- 地址转换流程:

逻辑地址 → 线性地址(分段机制) → 物理地址(分页机制),最终通过页表和TLB完成转换。

4.5 常见误区与注意事项

- 误区1:页表与虚拟地址空间无关

实际上,页表是虚拟地址空间的核心,每个进程的页表独立管理其虚拟内存的映射关系。 - 误区2:缺页中断必然导致性能下降

虚拟内存通过预取和缓存策略(如预加载常用页)可减少缺页频率,但频繁缺页(Thrashing)仍会显著拖慢性能。

四、高频误区与正解

❌ 逻辑地址 = 虚拟地址

- 正解:逻辑地址是编译生成的偏移量;虚拟地址是操作系统为进程抽象的整体地址空间(含逻辑地址)。

❌ 虚拟内存 = 外存

- 正解:虚拟内存是机制(分页+交换),外存是物理介质。虚拟内存由物理内存+磁盘交换区组成。

❌ 物理地址由程序员控制

- 正解:物理地址对用户透明,仅由MMU和操作系统管理。

❌ 分页机制中段基址无效

- 正解:x86架构兼容分段,但Linux等OS采用平坦模型(段基址=0)。

❌ 虚拟内存必然提升速度

- 正解:虚拟内存避免物理内存不足的崩溃,但频繁缺页中断(Thrashing)会严重拖慢性能。

五、总结

地址体系是计算机系统的核心,理解其层次结构、空间划分和存储协作机制是掌握操作系统和计算机体系结构的关键。

- 地址转换:由MMU硬件加速(TLB+页表),但缺页处理依赖操作系统,这是用户态与内核态协作的经典案例。

- 虚拟内存:通过分页机制和外存交换,实现了内存的灵活管理,是现代操作系统的重要特性。

- 性能优化:通过TLB命中率、大页和多大小页支持,可以显著提升地址转换效率,减少系统开销。

理解地址体系需掌握三条主线:

- 层次关系:逻辑地址 →(分段)→ 线性地址 →(分页)→ 物理地址;

- 空间划分:虚拟地址空间(进程视角) vs 物理地址空间(硬件视角);

- 存储协作:主存(高速临时存储) + 外存(低速永久存储) = 虚拟内存的物理基础。

关键点:地址转换由MMU硬件加速(TLB+页表),但缺页处理依赖操作系统,这是用户态与内核态协作的经典案例。

通过深入理解这些机制,开发者可以更好地设计和优化内存管理策略,提升系统性能和稳定性。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献16条内容

已为社区贡献16条内容

所有评论(0)