使用DDR4控制器实现多通道数据读写(七)

DDR4写模块根据ddr4_test模块发来的写开始信号,写数据数量,初始地址,首先通过写地址通道发送写数据的初始地址、写数据数量、和控制参数,wstrb信号作为写数据的掩码。在DDR4读模块中,根据ddr4_test模块发出的读开始信号,在读地址通道中发送读起始地址、读长度和控制信号,给DDR4发起读请求,根据读数据通道读出数据,rd_data作为读数据,rd_en作为读数据有效信号发送给ddr

一、 概述

在上一节中,我们使用DDR4的AXI接口做了一个简单的读写测试,这一节我们使用数据掩码(wstrb)来控制写入数据的有效字节。再使用不同的传输方式向DDR4中读写数据,这样可以更清晰的了解FIXED、INTR、WRAP的传输模式。

二、 使用wstrb信号控制写入DDR4的有效字节

wstrb:输入的数据字节掩码,数据位宽512位,含有64个字节,wstrb位宽为64位,每一位对应数据wdata的字节位,在本次仿真测试中,使wdata的全部字节有效。

在之前的测试中,我们使wstrb的每一位都为1,表示写入的wdata的全部字节有效。这次我们只使数据的低32字节有效,写入和读取的数据数量为16个。

测试流程:

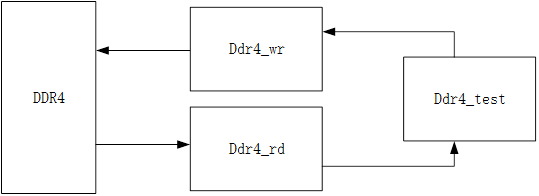

首先在ddr4_test模块来产生数据,将数据通过ddr4_wr模块使用axi协议写进ddr4中,当数据写入ddr4后,再通知ddr4_rd模块使用axi协议读出ddr4中的数据。流程图所示。

Ddr4_test模块功能:

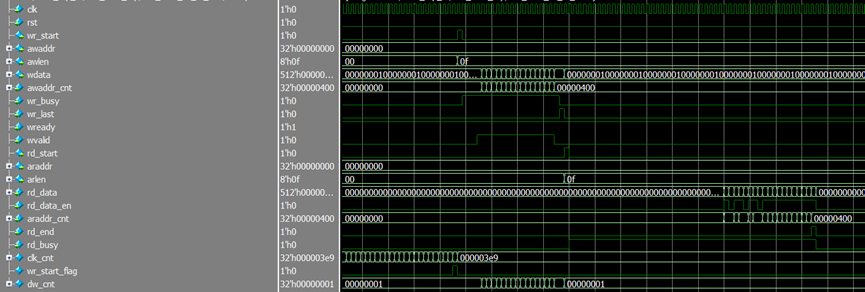

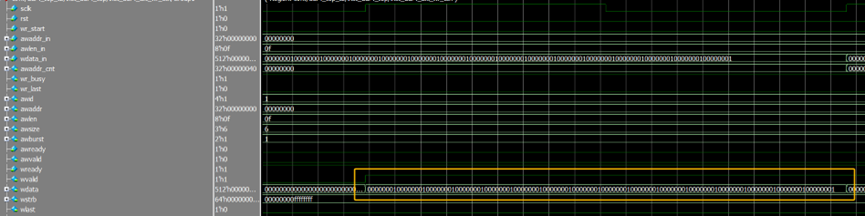

这个模块来控制读写DDR4的初始地址和数据数量。可以控制写进DDR4的数据值,和读出DDR4度出的数据值。在DDR4写数据完成后读出DDR4的数据。读写数据波形图如图所示。

Ddr4_wr模块功能:

DDR4写模块根据ddr4_test模块发来的写开始信号,写数据数量,初始地址,首先通过写地址通道发送写数据的初始地址、写数据数量、和控制参数,wstrb信号作为写数据的掩码。再通过写数据通道开始向DDR4中写入数据。当接收写响应通道的写响应成功标志时,表示DDR4写数据完成。写数据波形图如图所示。标注了写地址通道、写数据通道、写响应通道握手情况。

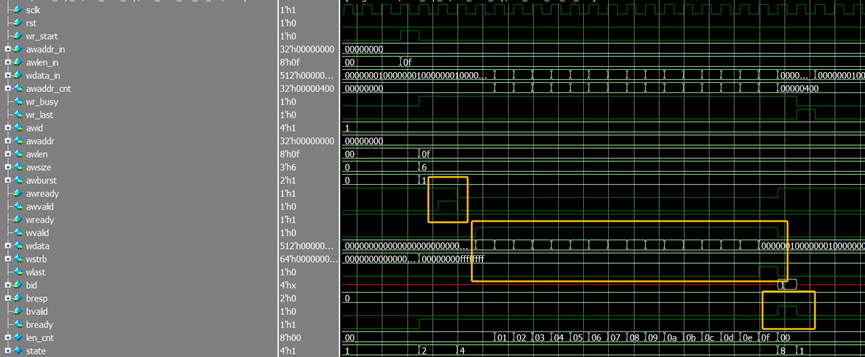

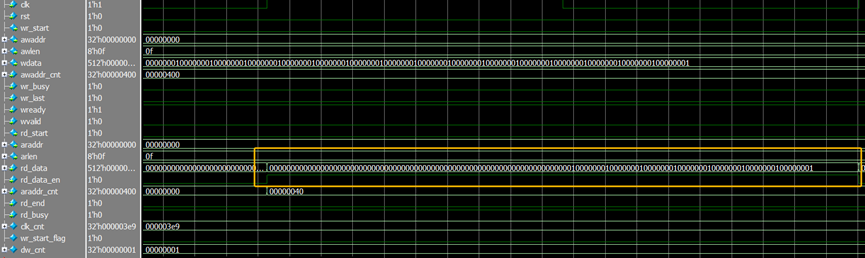

Ddr4_rd模块功能:

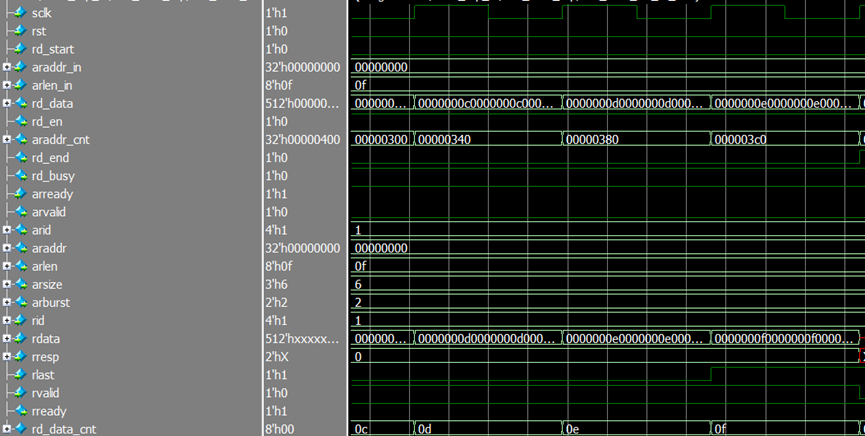

在DDR4读模块中,根据ddr4_test模块发出的读开始信号,在读地址通道中发送读起始地址、读长度和控制信号,给DDR4发起读请求,根据读数据通道读出数据,rd_data作为读数据,rd_en作为读数据有效信号发送给ddr4_test模块。如图所示,标注了读地址通道、读数据通道握手情况。

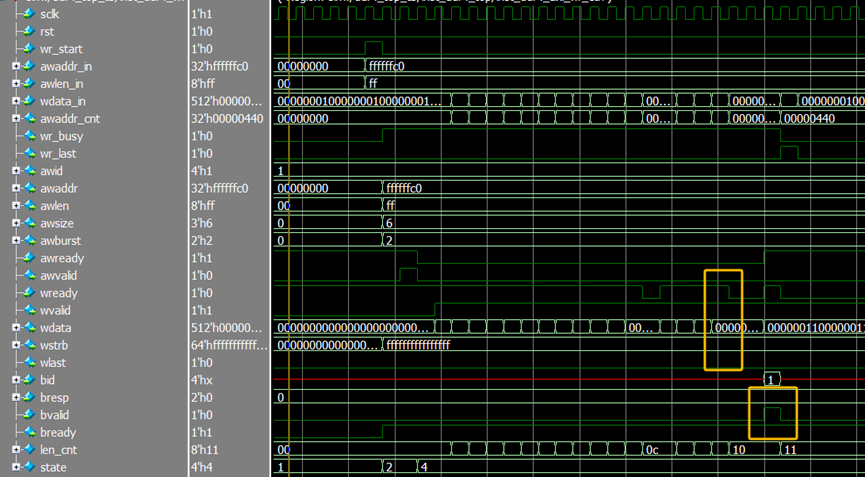

可以通过下图可以看到,ddr4_wr模块中的写数据中,将写数据512位分割16份,每一份的值都为1。

通过下图可以看到,读出来的数据的高256位已经被清零,只留下低256位与写数据一致。

三、 FIXED突发模式说明

在FIXED模式下,所有传输的地址保持不变,每次写入DDR4的数据都对应同一地址。所以对于DDR4内存来说,使用FIXED模式向同一地址写入数据时,都会覆盖之前写入的数据。通常,在使用DDR4时需要处理大量的数据,所以基本会使用INCR模式进行数据传输。

四、 WRAP突发模式说明

使用WRAP模式进行读写测试时,在下图中可以看到,我发出的写长度为’hff,但只发送了16个数据后,写响应通道就给出了响应,由此说明在使用WRAP模式时,对于突发长度大于16时不能正确写入。WRAP模式在地址递增中类似于INCR模式,每传输一个数据,地址增加64,当写入地址抵达回绕上界时,地址会移动到回绕下界,之后再递增。突发长度必须为2、4、8、16其中之一。起始地址必须为数据字节数量的整数倍。

关于WRAP模式下,回绕边界的计算:

1、回绕边界=突发长度x数据字节数量。

2、地址下界=(初始地址/(突发长度x数据字节数量))x(突发长度x数据字节数量)。

计算地址下界时,舍弃小数,只保留整数。

3、地址上界:

地址下界+回绕边界。

例子1: 起始地址:64,

突发长度:16,

数据位宽:512,

本次写操作时,数据字节数量为512/8=64。地址下界为64/(16x64)=0。地址上界为0+(16x64)=1024。

那么地址递增规律为:

64—128—192—256—320—384—448—512—576—640—704—768—832—896—960—0。

例子2: 起始地址:512,

突发长度:16,

数据位宽:512,

本次写操作时,数据字节数量为512/8=64。地址下界为512/(16x64)=0。地址上界为0+(16x64)=1024。

那么地址递增规律为:

512—576—640—704—768—832—896—960—0–64—128—192—256—320—384—448。

可见WRAP模式下,不论在哪个地址中开始写入,都会将回绕边界中的地址写满,可以更方便进行DDR4的循环访问。

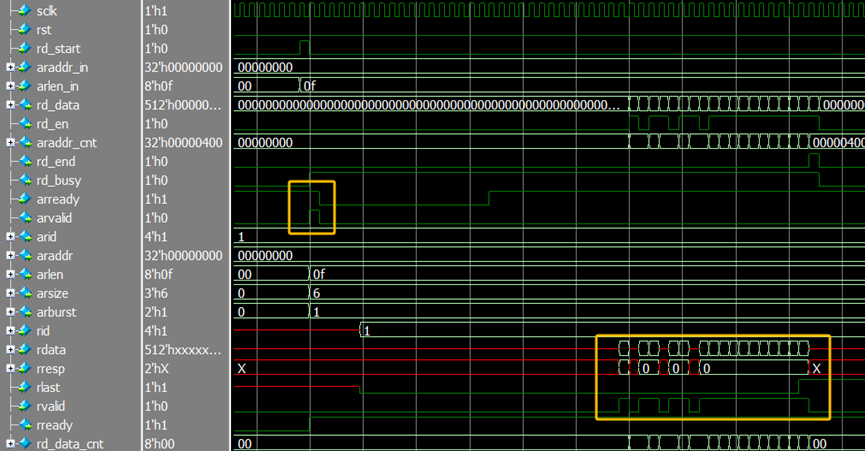

WRAP模式仿真波形:

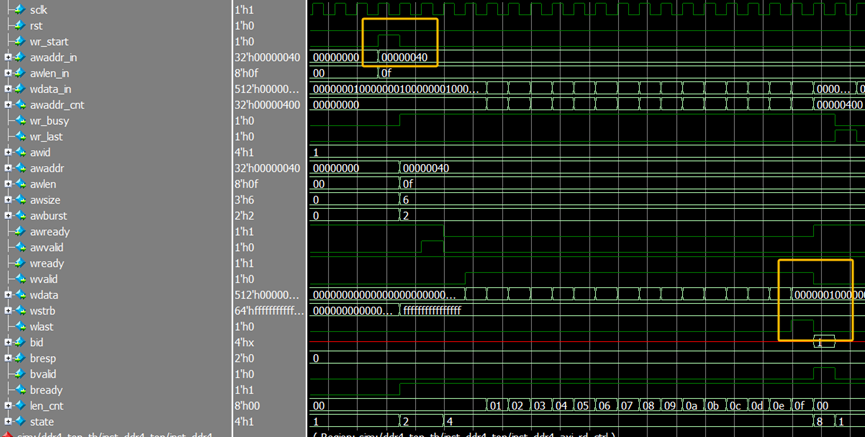

如图所示,在WRAP模式下,写突发长度16,发送的最后一个数据中,每个dw的值为0x10,。

如图所示,读起始地址为0,读出16个数据,读出的第一个数据中,每个DW值为0x10。

在下图中,可以看到最后读出来的数据,每个dw值为0x0f。根据读写地址和数据,可以看出该波形正好对应之前的例子1。

五、 结尾

对于DDR4的AXI4协议的说明告一段落,通过这几章的内容,应该会对DDR4的AXI协议有了一些了解,后边会把工程的架构说明,并放出工程框架,供大家参考。

本文章由威三学社出品

对课程感兴趣可以私信联系

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献10条内容

已为社区贡献10条内容

所有评论(0)