CPU自制入门-CPU的设计与实现-计算机系统

I/O( Input/Output)是进行数据输入输出的装置。计算机通过 I/O 和外部实现数据交换。计算机的处理操作按照从外部读取数据、在内部处理数据、再向外部输出结果的顺序进行。以个人电脑为例,如图 1-11 所示,它从鼠标或键盘输入数据,处理器根据程序处理数据,通过显示器等向外部输出结果。字节序将多字节数据存储在内存中时,各字节的存储顺序称为字节序。比如,将 4 字节数据0x12345678

1.2.1 什么是计算机

计算机是根据程序进行运算和数据处理的计算机器。近年来,随着 PC( Personal

Computer,个人电脑)在普通家庭中的广泛普及, 计算机对我们的生活产生了深远的影

响。如今,不仅是 PC,与我们生活息息相关的手机、家电等也广泛应用了计算机。

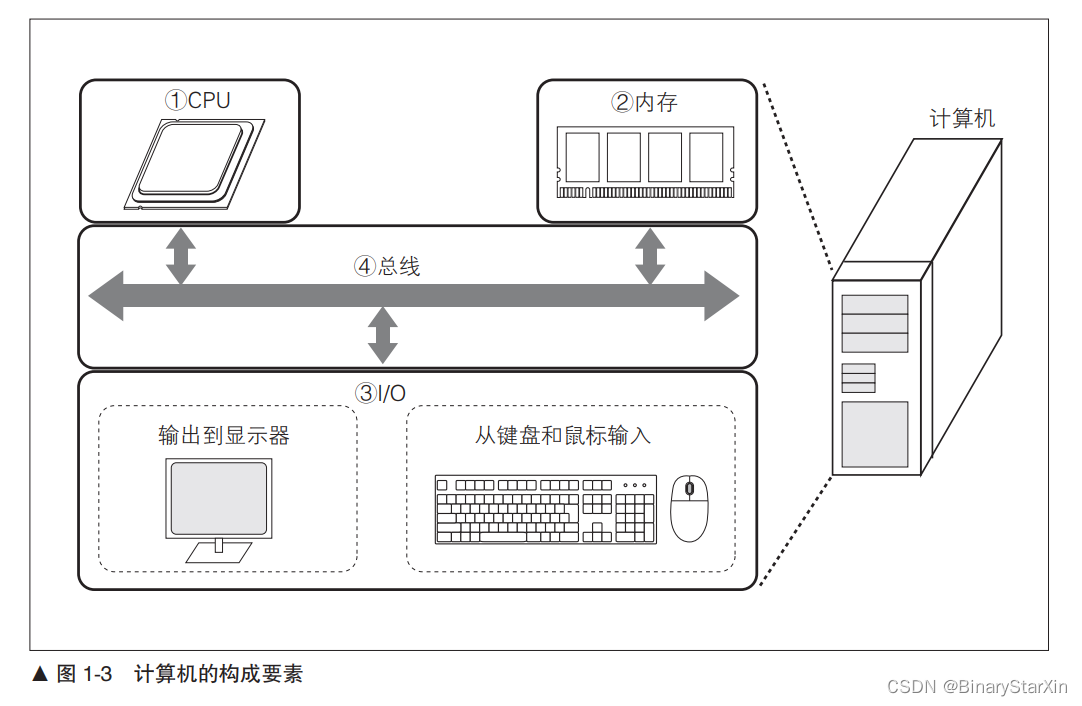

通常,计算机由以下几部分组成:负责计算和处理数据的 CPU、负责存储程序和数据的存储器, 以及和外部进行数据交换的 I/O( Input/Output,输入输出装置)。各部分通过总线连接就构成了一台计算机。

计算机的构成要素如图 1-3 所示。以 PC 机的组成为例,一般使用 Intel 或 AMD 公司的 CPU, DDR3 SDRAM 之类的内存,另外还有键盘、鼠标、显示器等 I/O。这些CPU、内存、 I/O、总线并不局限于 PC,多数计算机都是由这四大要素组成。

1.2.2 什么是 CPU

CPU 是计算机中进行各种运算和数据处理的装置。 CPU 是 Central Processing Unit

(中央处理器)首字母的缩写。 近年来,商用 CPU 基本都基于集成电路技术制造,然后

封装到图 1-4 所示的包装后出售。

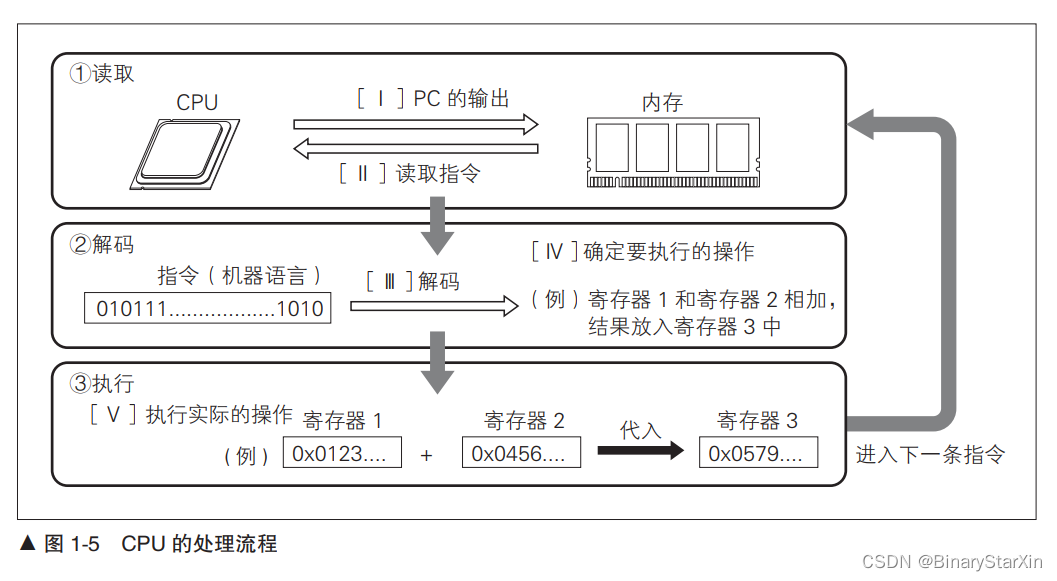

CPU 是一种根据指令进行各种处理的电子电路。图 1-5 展示的是 CPU 的处理流程。

内存存储着可由 CPU 执行的指令集合所组成的程序。 CPU ①读取( Fetch)内存中的指

令,然后对其要处理的操作进行②解码( Decode),最后进行③执行。

CPU 基本上就是在这三种状态之间进行任务处理。 这种将存储在内存中的程序读出

再执行的架构称为存储程序式架构 A。

■ ①读取

首先, CPU 要把即将执行的指令从内存中读取出来。 CPU 中有个 PC( Program

Counter,程序计数器)寄存器, 其中保存着即将执行的指令的地址。指令的读取是通过

将 PC 寄存器的值输出给内存,由内存返回该值对应地址中的指令。

■ ②解码

然后, CPU 对读取的指令所对应的操作进行解码。指令有很多种,有进行各种运算

的指令、控制下一条命令的指令、对内存和 I/O 进行读写的指令, 还有对 CPU 进行控制

的指令。这些指令由 CPU 中被称为指令解码器的模块进行解码。可以用来保存地址和

运算结果的寄存器称为通用寄存器( General Purpose Register)。

■ ③执行

最后, CPU 对解码器确定的操作进行处理。 CPU 可以从内部存储装置——寄存器或外部的内存读取数据并处理,然后将结果写回寄存器或内存。

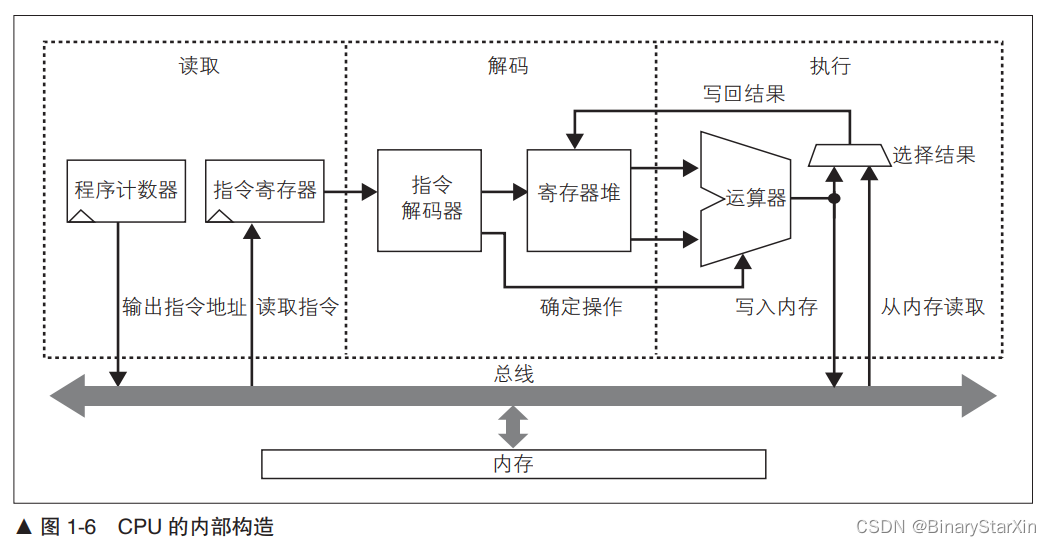

简化的 CPU 内部构造图如图 1-6 所示。读取指令时, CPU 将 PC 寄存器的值输出到

内存,然后从内存中将对应的指令取回。取回的指令保存在指令寄存器中。指令解码是将储存在指令寄存器的指令解码, 确定将要处理的操作。大多数情况下,在确定即将处理的操作的同时, CPU 会从通用寄存器中读取运算要使用的数据。指令执行时,从通用寄存器将操作数值取出, 通过运算器处理然后将结果写回。 CPU 执行的运算结果可以写回通用寄存器,也可写入内存。 CPU 也可以从内存读取数据作为结果返回。

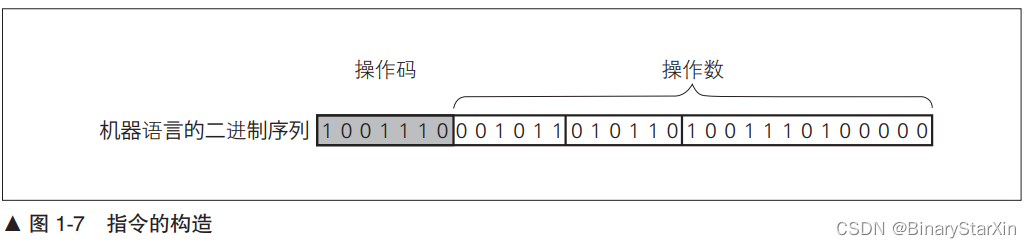

CPU 执行的指令,由代表操作种类的操作码和代表操作对象的操作数两部分组成。指令的构造如图 1-7 所示。指令本身用特定的二进制序列来表示,这种二进制序列称为机器语言。

▲ 图 1-7 指令的构造

操作数是由寄存器地址、内存地址或立即数来指定的。立即数是指嵌入指令中的固定常数。操作数的数量和位宽根据 CPU 和指令的不同而不同。根据可使用的操作数的数量,指令可以分为 3 操作数形式、 2 操作数形式和 1 操作数形式等。

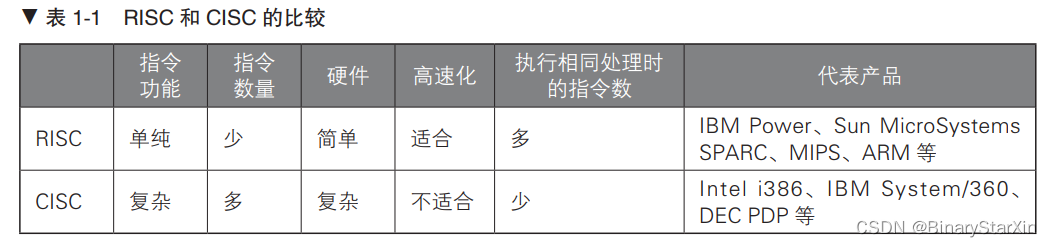

根据执行的指令的特征, CPU 分为 RISC( Reduced Instruction Set Computer,精简

指令集计算机)和 CISC( Complex Instruction Set Computer,复杂指令集计算机)两种。

表 1-1 比较了 RISC 和 CISC 的特征,并给出了其代表产品。

RISC 类 CPU 的指令功能单纯,种类较少。相对应地, CISC 类 CPU 的指令功能复

杂,种类繁多。 RISC 指令精简的好处是 CPU 内部构造可以简化,适合高速操作。但是在进行相同操作时, 由于每一条指令都功能单纯,所以与 CISC 相比,它需要使用更多的指令数量。 虽然 CISC 的内部构造复杂不适合高速操作,但进行相同处理时指令数比RISC 要少。

RISC 架构最大的特点是只使用载入和存储指令访问内存, 这种架构称为载入存储架构( Load/Store Architecture)。这样做的好处是可以简化指令集和流水线设计。在这种架构下,运算指令只能对寄存器中的数据进行操作。

RISC 和 CISC 两种架构各有所长,孰优孰劣不能一概而论。在追求高速运作的CPU 的领域中, RISC 被认为更具优势。这些年,虽然 Intel 和 AMD 两家公司的 CPU指令集依然是 CISC 的,但内部却将复杂指令分解为简单指令, 使得内部可以像 RISC一样工作。

CPU 的位宽

CPU 的位宽表现了 CPU 可以访问的地址空间或数据的大小。比如,32 位 CPU 可以处

理 32 位的数据,可以访问的地址空间为 4G 字节(2 的 32 次方)。随着程序、数据的规模和内存容量的增大,32 位 CPU 有些不太够用,最近的 CPU 一般都是 64 位。 CPU 的位宽并没有明确的定义。有根据寄存器或地址的宽度划分的,也有根据指令或总线宽度划分的各种标准。现在大家普遍将 CPU 可以处理的整数型数据的宽度定为位宽。实际上,根据 CPU 厂家的想法和主张,解释也不尽相同。除了位宽,CPU 可以访问的地址空间或数据的大小还用字(word)来表示。通常,CPU 的字长和位宽是一致的。1.2.3 什么是内存

内存是用来存放运行时指令(程序)和数据的存储器。为了和计算机中长期保存数据和程序的存储器区别,内存有时也称为主存( Main memory)。

最近的计算机通常采用 DRAM( Dynamic Random Access Memory,动态随机存储器)技术的内存。 DRAM 是通过在电容器中积蓄电荷来保存数据的存储元件。电容器中充电状态是 1, 放电状态是 0,以此来表示数值。由于电容器中的电荷一段时间后会衰减,所以 DRAM 需要定期进行重新写入数据的刷新( Refresh)操作。根据访问方式和规格的不同, DRAM 分为 SDRAM( Synchronous DRAM,同步 DRAM)和 DDRSDRAM( Double Data Rate SDRAM,双倍数据率 SDRAM)等种类。

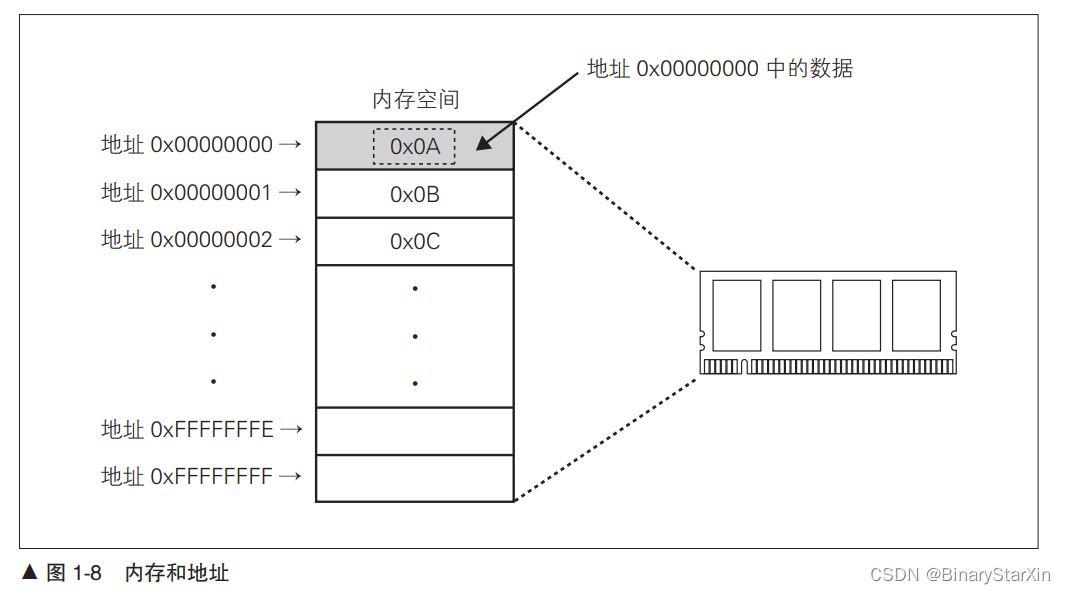

内存使用地址的概念来管理存储的数据。 地址表示的是数据存储的位置,如同数据的住所一样。 每个数据单元都有一个地址。大多情况下数据单元是一个字节( 8 位)长度。这种方式称为字节编址。图 1-8 说明了内存和地址的关系。

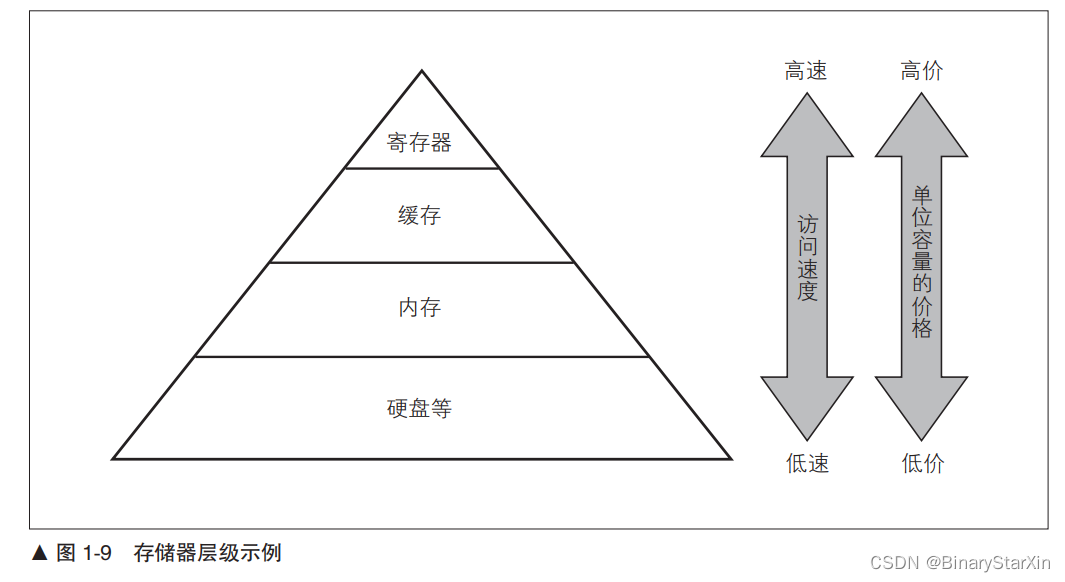

内存等存储器的特点是速度越快成本越高。因此通常使用“高速小容量”、“中速中等容量”到“低速大容量”等多种存储器组合的混合型架构。这种构造称为存储器层级。图1-9 是存储器层级的示例。

在存储层面, 速度最快的是 CPU 中的寄存器。 CPU 比内存速度快很多,由 CPU 直接访问内存效率较低。 为了提高内存访问速度,在 CPU 和内存间增加了被称为缓存的高速小容量存储器。缓存可以暂时性地缓冲存储从内存中读取的数据。 CPU 在访问内存时,如果需要的数据已经保存在缓存中, 则可直接从缓存中读取,以提高访问效率。根据容量和速度的不同,缓存也分为多个层级,通常为一级缓存、二级缓存等多个级别。

1.2.4 什么是 I/O

I/O( Input/Output)是进行数据输入输出的装置。计算机通过 I/O 和外部实现数据交换。计算机的处理操作按照从外部读取数据、在内部处理数据、再向外部输出结果的顺序进行。以个人电脑为例,如图 1-11 所示,它从鼠标或键盘输入数据,处理器根据程序处理数据,通过显示器等向外部输出结果。

字节序

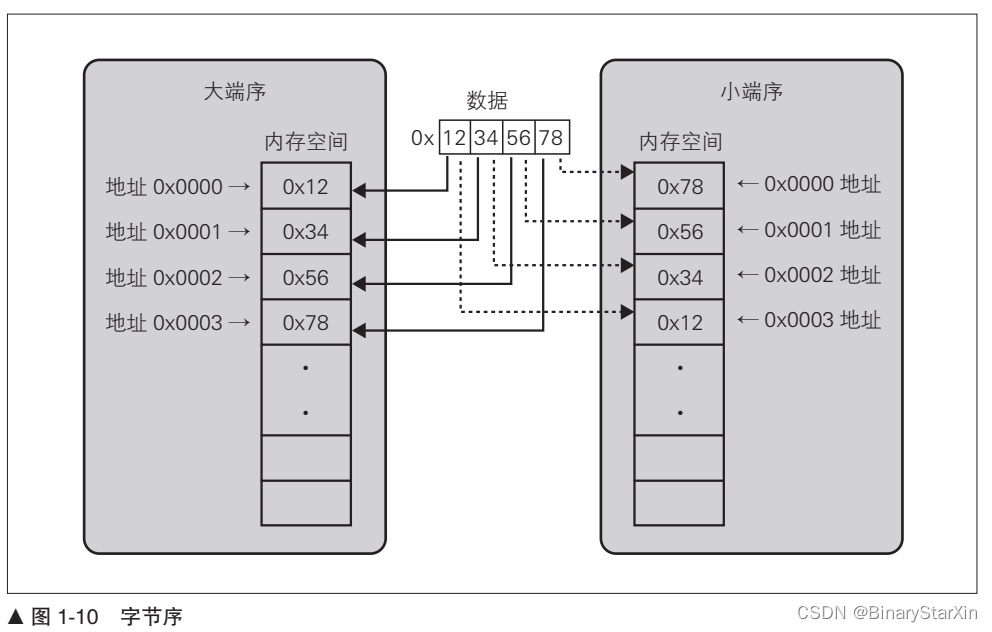

将多字节数据存储在内存中时,各字节的存储顺序称为字节序。比如,将 4 字节数据

0x12345678 放入内存时,地址 0 中放 0x12、地址 1 中放 0x34、地址 2 中放 0x56、地址 3

中放 0x78 的方式,称为大端序。相对地,地址 0 中放 0x78、地址 1 中放 0x56、地址 2 中

放 0x34、地址 3 中放 0x12 的方式,称为小端序。这两种数据存储方式请参见图 1-10。

对人类来说,大端序理解起来比较容易,然而对计算机来说,小端比较容易操作,因为不同长度数据的低位位置是相同的。

不同的 CPU 采用的字节序也不尽相同,由此产生的软件通用性和可移植性的问题也屡屡发生。Intel 公司的 x86 架构采用的是小端序,而 Sun(现属 Oracle)公司的 SPARC 处理器和 MIPS 科技公司的 MIPS 处理器等采用的是大端序。

最近,很多处理器考虑到软件的通用性和可移植性,同时支持两种字节序并可依据程序

切换,这种方式称为双端序。

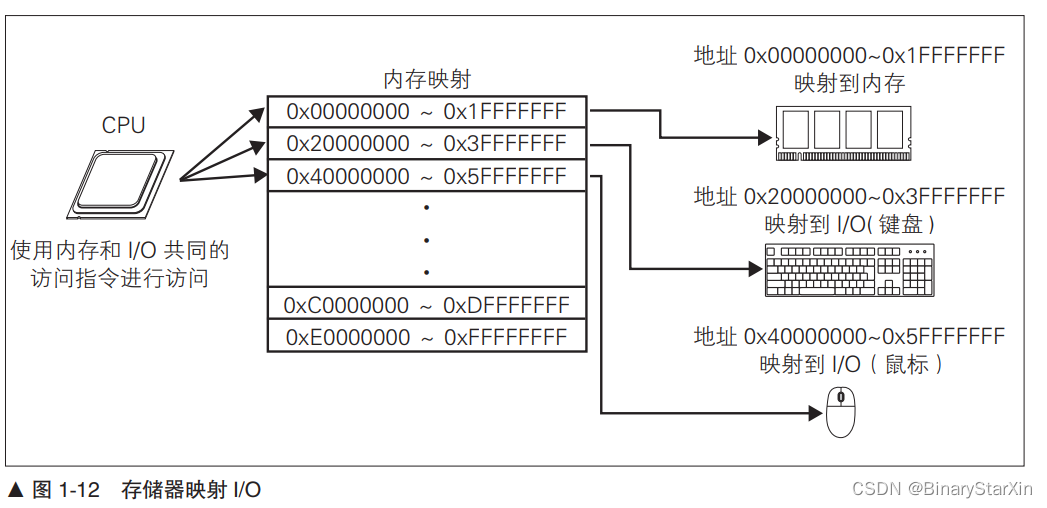

访问 I/O 的方式大致分为存储器映射 I/O 和端口映射 I/O 两种。存储器映射 I/O 方式中, I/O 也和内存一样使用地址进行管理,可以和访问内存一样的方式进行访问。 存储器映射 I/O 的概要如图 1-12 所示。存储器映射 I/O 方式中,由于使用访问内存的指令进行 I/O 访问,硬件上较为简化。但缺点是, I/O 也会占用地址空间。

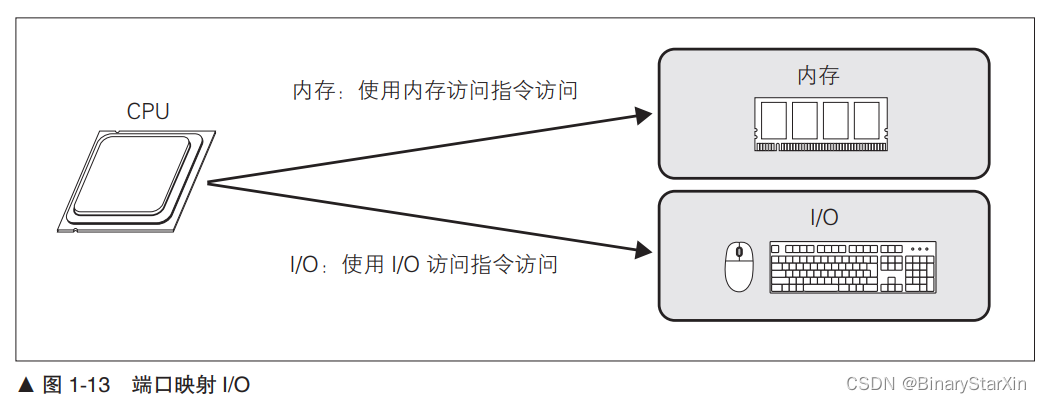

端口映射 I/O 方式中, CPU 含有支持访问 I/O 的专用指令。端口映射 I/O 的概要如图 1-13 所示。端口映射 I/O 方式的优点,一是地址空间可以全部分配到内存,二是内存和 I/O 的访问可以在指令级别区分。但是,由于需要专用指令,缺点是硬件设计变得复杂。

1.2.5 什么是总线

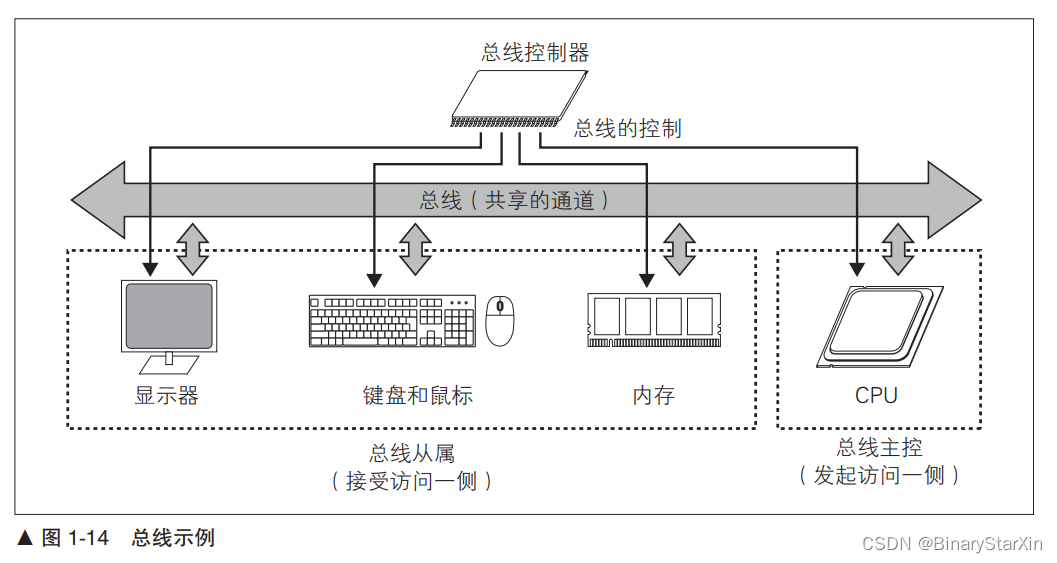

总线是 CPU、内存和 I/O 之间交换数据的共同通道。总线将一根信号线在多个模块间共享进行通信。图 1-14 是总线的示例。两个模块通过总线交换数据时, 发起访问的一侧称总线主控,接受访问的一侧称为总线从属。图 1-14 的示例中, CPU 为总线主控,内存、 I/O 等为总线从属。

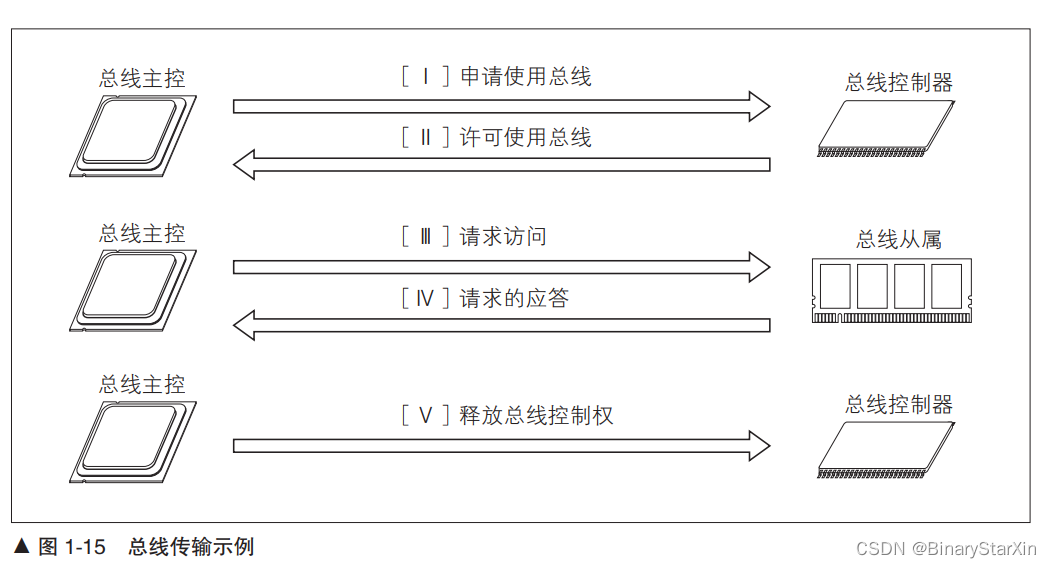

总线一般由数据总线、地址总线和控制总线构成。数据总线用来传输交换的数据,地址总线用来指定访问的地址, 控制总线负责总线访问的控制。各个信号的时序、进行交换的规则等称为总线协议。 通过总线交换数据的整个过程称为总线传输。总线传输的示例请参见图 1-15。

[Ⅰ]申请使用总线

多数情况下,总线上接有多个总线主控,由于总线是共享的通道,不能同时使用多个总线主控。因此,需要对多个总线主控的使用请求进行调停。访问总线的权力称为总线控制权,对多个访问的调停称为总线仲裁。总线仲裁由总线控制器内的仲裁器实施。总线主控在访问总线之前先向总线控制器申请总线控制权。

[Ⅱ]许可使用总线

总线控制器对多个总线主控的请求进行调停,依据仲裁规则对总线的使用进行许可授权。

[Ⅲ]请求访问

获取总线控制权的总线主控对总线从属发送访问请求。请求中包含“要访问哪个地址”、“是读取访问还是写入访问”和“写入时的数据”等信息。由于总线是共享的通道,总线主控输出的信号会发送到所有总线从属。因此使用片选信号( Chip select,芯片选择信号)等控制信号来区别对哪个从属进行访问。每个总线从属都设有片选信号,可以使用片选信号选择要访问的总线从属。一般的总线结构会为每个总线从属分配地址空间。总线控制器内的地址解码器根据要访问的地址产生片选信号。

[Ⅳ]请求的应答

接受访问的总线从属会根据请求对总线主控进行应答。针对请求,应答时采用Ready 等控制信号。在接受读取请求时,应答的同时输出读出的数据。

[Ⅴ]释放总线控制权

总线使用完毕,总线主控通知总线控制器释放总线控制权。

总线的优缺点

总线的优点是只要遵循总线协议,任何设备都可以简单地进行连接。并且由于使用的是

共享通道,硬件的成本也比较低。但是,数据传输的吞吐量较低。

近几年,一台计算机搭载多个 CPU 的情况比较常见。随着与总线通信的 CPU 数量的增多,总线很容易变得拥堵。因此,业内也在开发各个节点通过网络连接的技术来替代传统的通道共享的总线。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)