头歌计算机组成原理实验—运算器设计(3)第3关:4位快速加法器设计

头歌计算机组成原理实验—运算器设计(3)第3关:4位快速加法器设计

·

第3关:4位快速加法器设计

实验目的

帮助学生掌握快速加法器中先行进位的原理,能利用相关知识设计4位先行进位电路,并利用设计的4位先行进位电路构造4位快速加法器,能分析对应电路的时间延迟。

视频讲解

实验内容

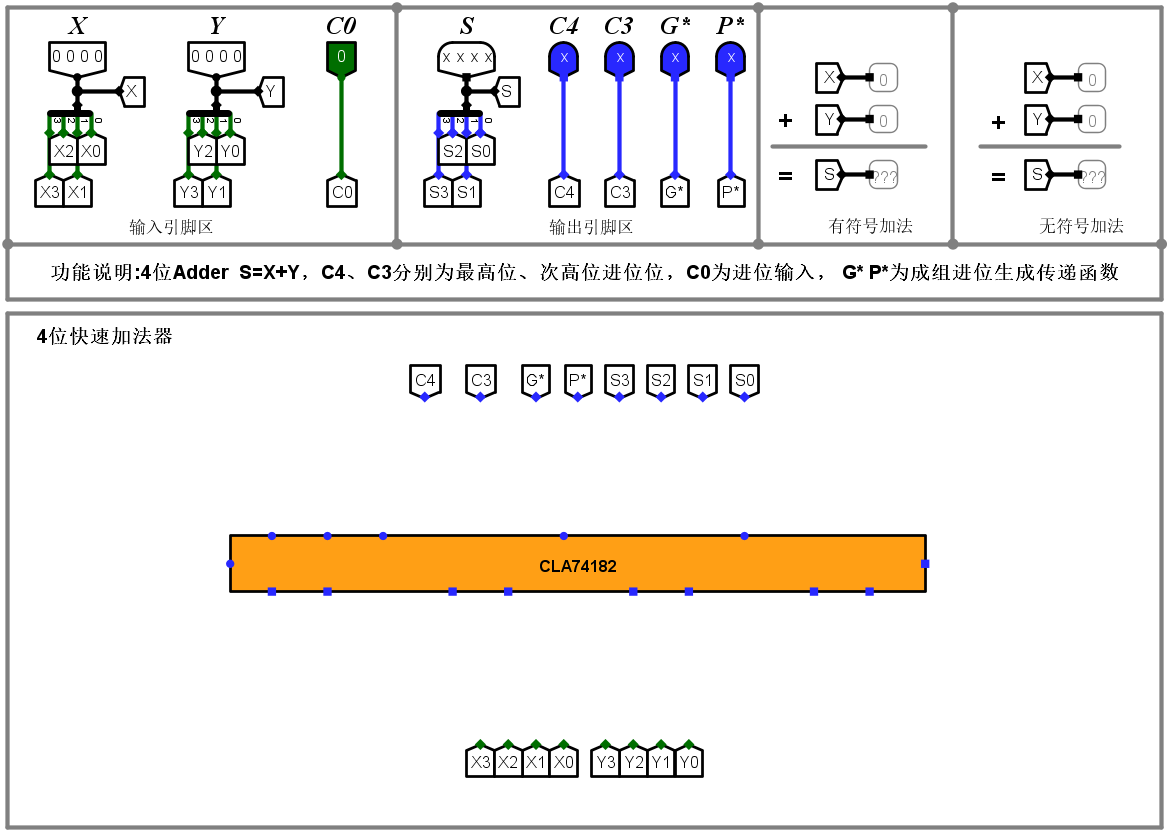

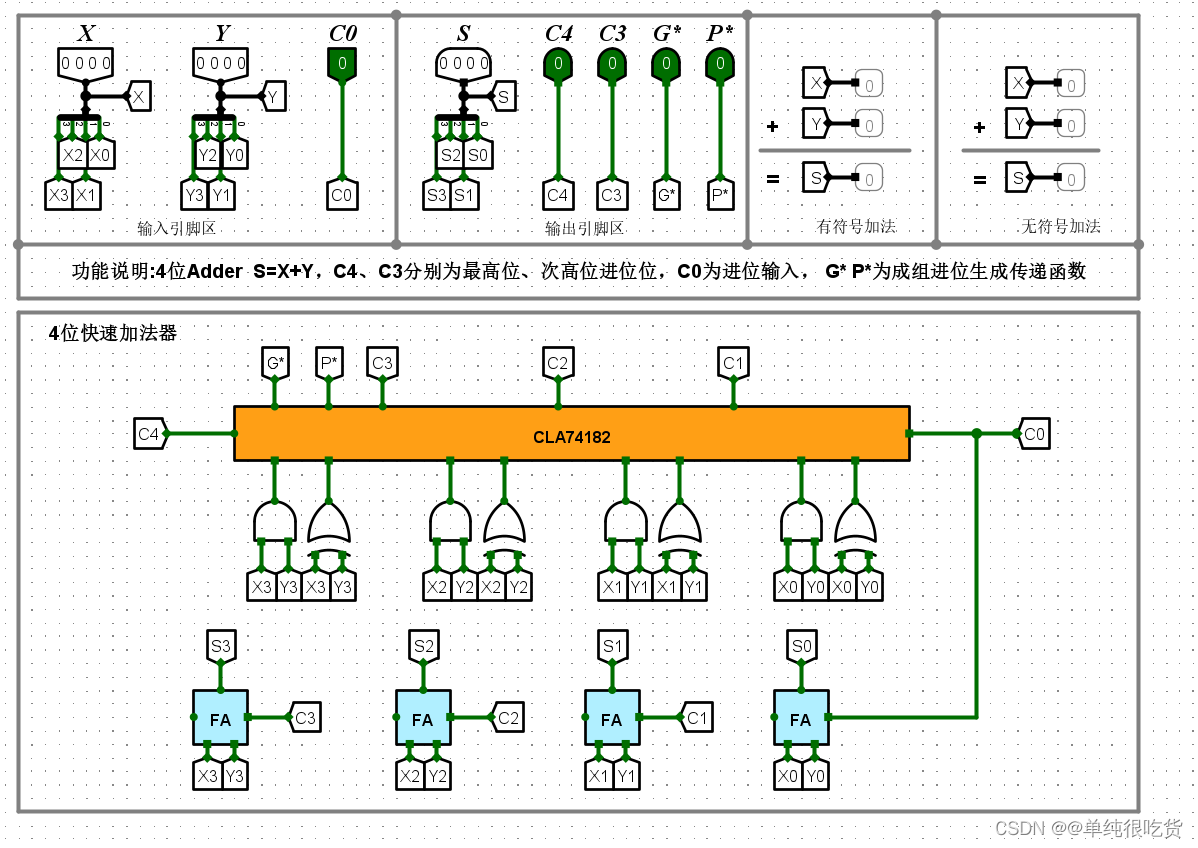

利用前一步设计好的四位先行进位电路构造四位快速加法器,其引脚定义如图所示,其中 X,Y 为四位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为 4 位成组进位生成函数和成组进位传递函数。

电路框架

alu.circ

电路引脚

| 信号 | 输入/输出 | 位宽 | 说明 |

|---|---|---|---|

| X | 输入 | 4 位 | 加数 |

| Y | 输入 | 4 位 | 加数 |

| C0 | 输入 | 1 位 | 进位输入 |

| S | 输出 | 4 位 | 运算和 |

| C4 | 输出 | 1 位 | 最高位进位位 |

| C3 | 输出 | 1 位 | 第 3 位进位位 |

| G* | 输出 | 1 位 | 成组生成函数 |

| P* | 输出 | 1 位 | 成组传递函数 |

电路测试

完成实验后,利用文本编辑工具打开 alu.circ 文件,将所有文字信息复制粘贴到 Educoder 平台的 alu.circ 文件中,再点击评测按钮即可进行本关测试。平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装,本关测试用例如下:

Cnt X Y C0 Sum G P C4 C300 0 0 1 1 0 0 0 001 6 7 0 d 0 0 0 102 6 f 1 6 1 0 1 103 c 8 1 5 1 0 1 004 8 9 0 1 1 0 1 005 3 5 0 8 0 0 0 106 8 e 0 6 1 0 1 0...

开始你的闯关任务吧,升级打怪中....

参考答案:

直接复制代码,字数太多,发不了,后续会上传文件

参考电路图

如果对你有所帮助,感谢点赞加收藏!

完整的代码可以到【WRITE-BUG数字空间】我的个人学习圈查看。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献10条内容

已为社区贡献10条内容

https://www.writebug.com/article/ca9da204-f539-11ed-9898-0242c0a8100e

https://www.writebug.com/article/ca9da204-f539-11ed-9898-0242c0a8100e

所有评论(0)