一文讲透什么是ADC/DAC中的DDC、DUC、采样率以及数据率等概念

摘要:ADC/DAC中的采样率与数据率概念不同,采样率是转换器的时钟速率,而数据率是数字输出的实际速率。抽取通过滤波降低数据速率,提升信噪比但牺牲带宽;内插则通过插零和滤波提高采样率,将镜像信号移远但增加延迟和功耗。JESD204B标准的高速转换器需平衡通道数与串行速率,内插/抽取技术是关键。文章还解析了DDC、DUC的应用及优缺点,为高速数据转换设计提供参考。(150字)

点击阅读原文,获取更多优质内容,请关注公众号通信射频老兵:一文讲透什么是ADC/DAC中的DDC、DUC、采样率以及数据率等概念

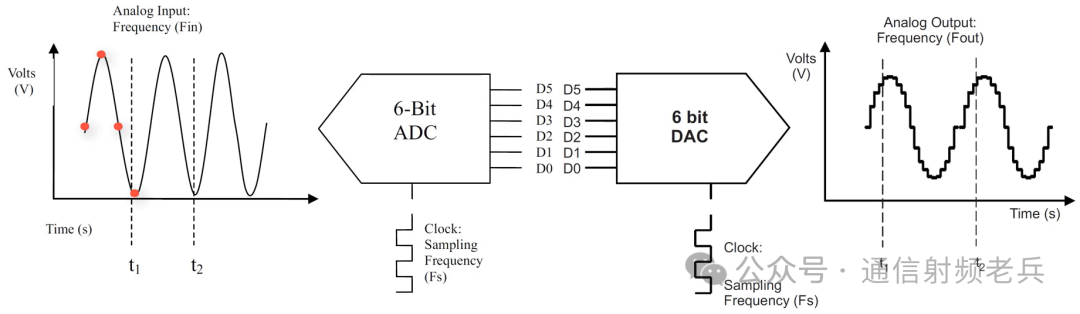

采样率是指模数转换器(ADC)对模拟输入进行采样的速度,或者数模转换器(DAC)输出模拟信号的速度。这个速率通常是提供给这些转换器的外部时钟速率。不过,现在的ADC/DAC,都有内部锁相环(PLL),它提供了一种选择,即可以使用较慢的输入时钟来生成高速采样时钟。

数据速率是指模数转换器(ADC)的数字输出数据的速率,或者是数模转换器(DAC)的数字输入数据速率。在很多情况下,这些速率与采样时钟的速率并不相同。

例如,某款16bits的ADC,以1Gsps的采样率在抽取因子为 2 的模式下运行,那么从该器件输出的实际数据速率将是1Gsps的采样率除以2,即500 Msps。如果用户使用抽取因子为 4 的模式,那么数据速率将是250 Msps。

请记住,这是等效的并行数据速率,而不是该器件输出引脚的串行器 / 解串器(SerDes)速率。这一点将在后面部分进行讨论。对于新型的高采样率数据转换器,需要更高的数据速率。在很多情况下,对于数据转换器器件,或者接收数据转换器数据或向数据转换器提供数据的现场可编程门阵列(FPGA)、专用集成电路(ASIC)来说,这些速率过高了。

另一个原因可能是可用的输入 / 输出(I/O)数量。无论哪种情况,数据速率通常都需要降低。为了实现这一点,就要用到内插和抽取技术。在使用抽取或内插时,一个不错的经验法则是选择一个能够支持信号带宽的数据速率,以及一个能够支持频谱纯度的采样率。

下面,我们将讨论抽取的相关概念。这将包括其定义、时间与频率的对比、优缺点,以及一些具体器件的示例。

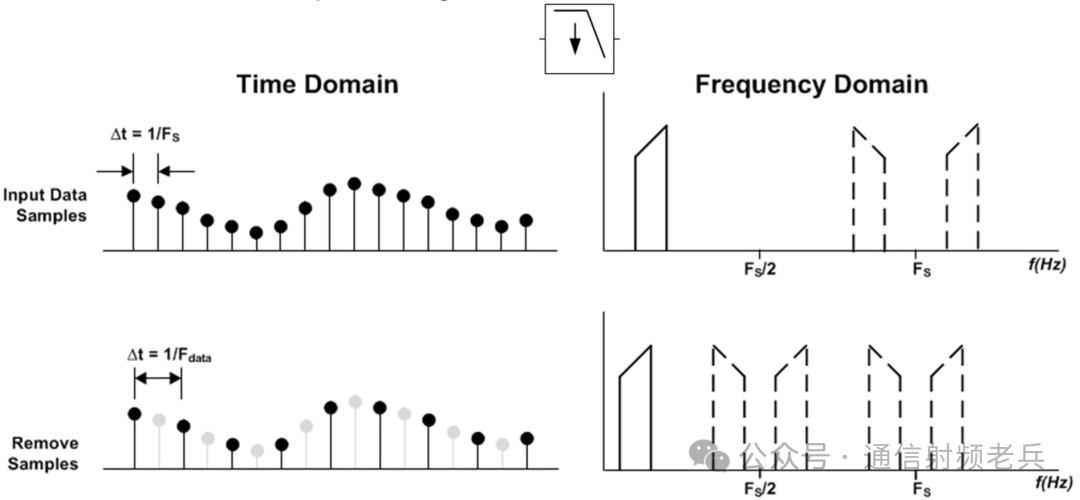

抽取究竟是什么呢?在数字信号处理中,抽取是降低信号采样率的过程。术语 “降采样” 通常指的是这个过程中的一个步骤,但有时这两个术语可以互换使用。与增加采样率的上采样或内插互补,抽取是多速率数字信号处理系统中采样率转换的一种特定情况。

当对信号的采样序列或其他连续函数执行抽取操作时,它会产生一个序列的近似值,这个近似值就如同以较低的采样率对信号进行采样所得到的结果一样。这是通过从数据流中去除采样点来实现的。抽取通常会先经过一个数字低通滤波器或抗混叠滤波器,然后再进行抽取操作。

这个操作类似于使用一个中心频率等于采样率除以抽取因子的模拟抗混叠滤波器。抽取因子通常是一个大于 1 的整数或有理分数。这个因子用于除采样率,或者等同于用输出数据速率乘以这个数,以此来确定模数转换器(ADC)实际使用的采样率。

抽取被用于将采样率降低到设备能够处理的水平,使得可以采用较高的采样率来实现更灵活的频率规划,并且通过滤波能够提升频谱性能。

下图,展示了抽取函数在时域和频域的示例。当执行抽取操作时,会产生镜像信号,就像在频域图中显示的那样。在这个例子中,围绕采样率或转换器的信号和镜像信号会向下移动到采样率的二分之一。采样率为 2 倍 Fs时的信号和镜像信号会向下移动到 Fs,以此类推。然后使用低通滤波器来提供抗混叠保护,这将去除这些镜像信号,并在低得多的数据速率下得到干净的频谱。

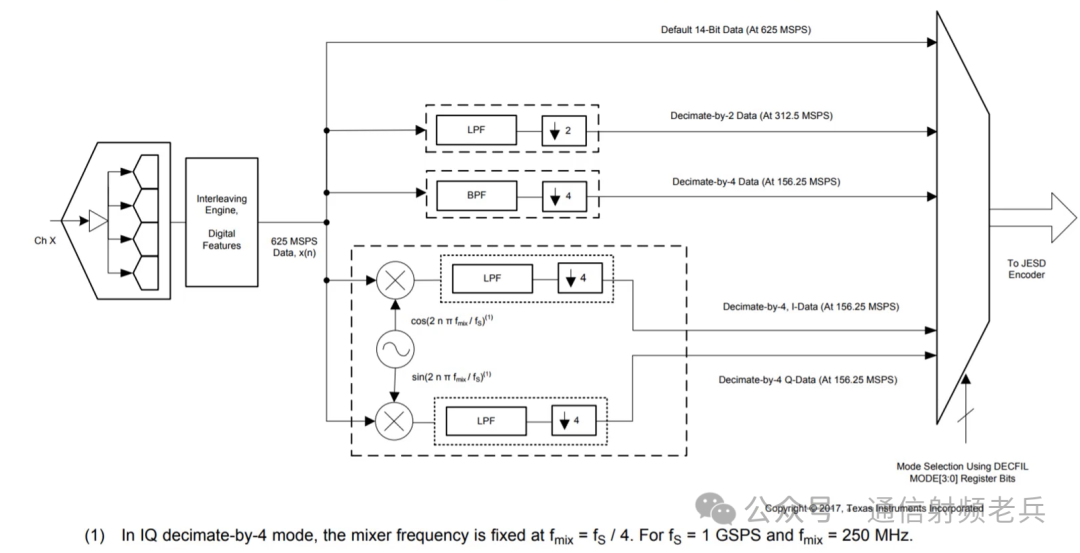

数据手册通常会包含显示数字下变频器(DDC)可用功能的方框图。下图展示了某模数转换器(ADC)内部可用的数字下变频器功能示例。从这个图中可以看到,这款器件提供了几种功能,包括抽取因子为 2 的模式、抽取因子为 4 的模式、接着是抽取因子为 4 模块的混频器移位选项,以及数字下变频器旁路模式。

如前面提到的,抽取伴随着滤波,从这个方框图中可以看到这一点。这款器件在抽取因子为 2 的模式下提供了低通滤波器或高通滤波器的选项。在抽取因子为 4 的模式下,它为带通滤波器提供了四种不同的中心频率选项。

使用抽取既有优点,也有一些缺点。优点包括它将提供信噪比(SNR)处理增益,信号的频域视图保持不变,抽取滤波器会降低噪声功率,信噪比性能得到改善,并且由于对采样进行平均处理,转换器的整体噪声会降低。不过,使用抽取也并非没有代价。一些缺点是需要更多的数字逻辑。使用更多的数字逻辑会消耗更多功率,并且整体信号带宽能力会降低。

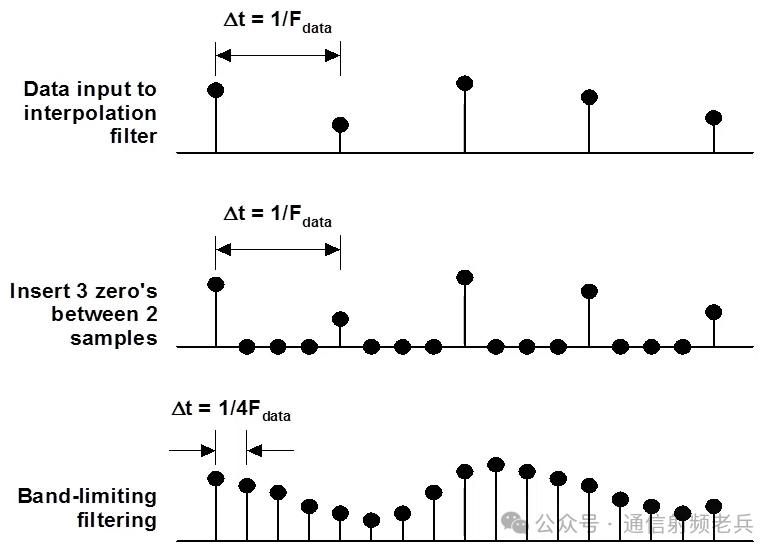

内插究竟是什么呢?在数字信号处理中,内插(或上采样)是在不影响信号本身的情况下增加信号采样率的过程。内插是一种在一组离散的已知数据点范围内构建新数据点的方法。

执行内插的一种典型方法如下:在每个采样点之间插入一个逻辑 0。这被称为零插入或上采样。对由上采样过程产生的镜像信号进行滤波。这将实现 2 倍内插。要实现 4 倍内插,再次重复这个过程。要实现 8 倍内插,再重复一次,以此类推。这种级联方法是比较好的,因为它提高了所需半带滤波器的效率。

通过内插,可以提高数模转换器(DAC)的输出速率。镜像信号可以被移到离目标感兴趣频带更远的地方,这允许有更宽的奈奎斯特区域,并且能够为数模转换器保持合理的数字数据速率。

下图展示了内插在时域中的功能。这个例子显示在原始采样点之间插入了三个零。添加零并不会改变信号的频谱内容,只是拓宽了带宽。然后使用诸如低通滤波器之类的滤波方法,对添加的采样点进行调整,以填充实际采样点之间缺失的电平,如底部的图表所示。

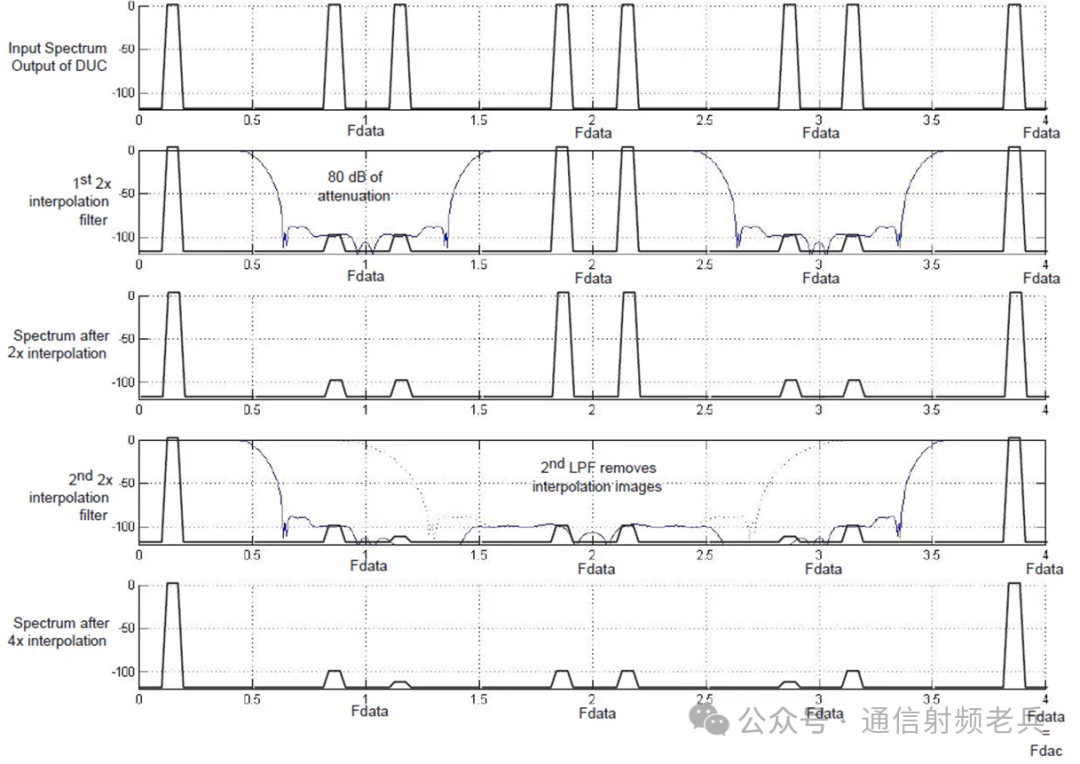

下图展示了内插在频域中的视图。上方的图表是在向原始数据添加零之后,但在应用任何滤波之前,数字上变频器的典型输出。第二张图表展示了 2 倍内插低通滤波器的效果。这个滤波器将用于衰减在 Fdata周围的数据镜像信号。通常,如果需要大于 2 倍的抽取,会分阶段进行。

第三张图表展示了在信号链中使用的第二个 2 倍内插阶段对实现 4 倍内插的效果。第四张图表则展示了第二阶段的第二个低通滤波器处理后的结果。使用这两个低通滤波器,可以使输出信号的音调保持不变,但采样率要高得多,如底部图表所示。现在,如果有需要,用户可以使用数控振荡器(NCO)将这个原始信号移到高得多的中频(IF),并且性能下降幅度最小。

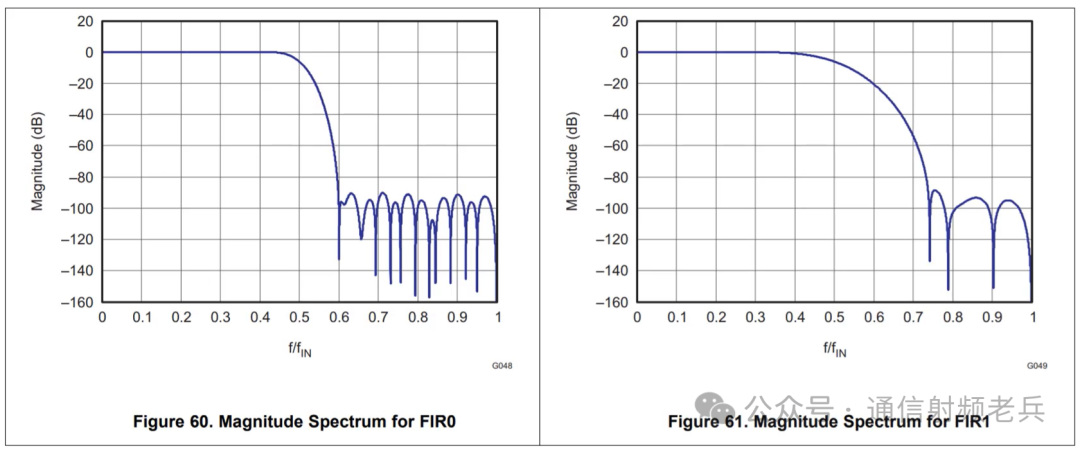

器件的数据手册应该会显示器件内插滤波器的有限脉冲响应(FIR)滤波器响应。下面图 60 和图 61 展示了 某DAC所使用的 FIR0 和 FIR1 内插滤波器的幅度频谱响应。

横轴使用了相对于 FIR 滤波器输入数据速率的归一化刻度。在器件数据手册中还能找到的其他图表包括所使用的整个级联内插模块的复合滤波器响应。请注意,当感兴趣的频率接近滤波器的转折频率时,信号幅度会有损失,这将导致信噪比(SNR)降低。此外,使用多个 FIR 滤波器会给数据路径增加延迟。这些延迟数值通常会列在数据手册中。

使用内插既有优点,也有一些缺点。优点是它会将数模转换器(DAC)的镜像信号移到离感兴趣频带更远的地方,从而使输出滤波更容易。它允许有更宽的奈奎斯特区域,以便进行灵活的频率规划,降低噪声频谱密度,降低所需的输入数据速率,并实现更高的输出采样率。

不过,使用内插也并非没有代价。一些缺点是需要更多的数字逻辑,使用更多的数字逻辑会消耗更多功率,并且会增加延迟,而且输入带宽会受到内插滤波器的限制,例如BW=0.4*Fdata。

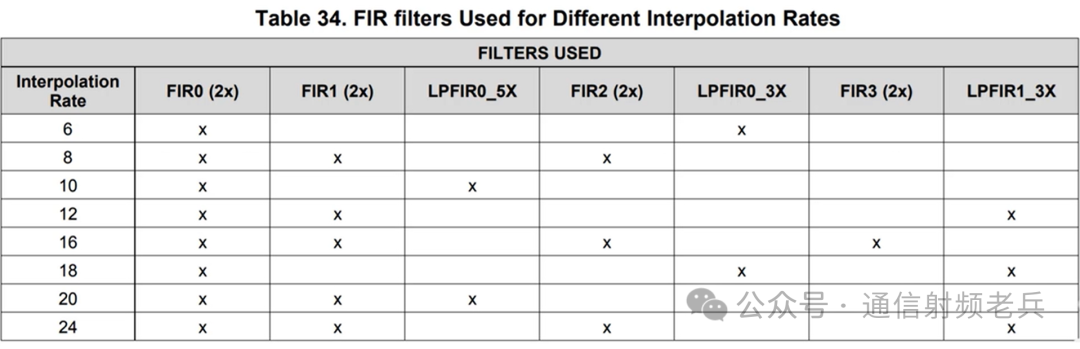

下图是某一款具有内部内插功能的数模转换器(DAC)器件示例。如图所示,这个功能允许有几种不同的内插速率。这个表格还向用户展示了用于实现各个内插速率的滤波器。

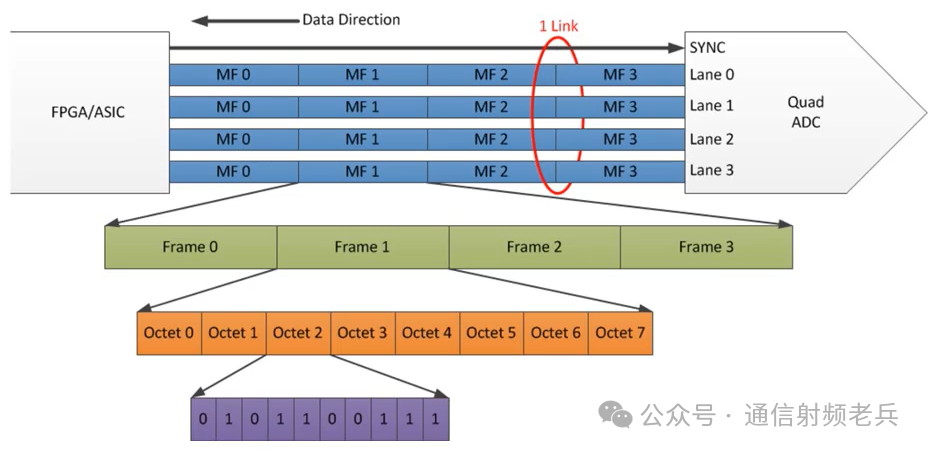

接下来我们将讨论使用 JESD204B 标准的新型高速数据转换器的采样情况。JESD204B 是数据转换器与现场可编程门阵列(FPGA)或专用集成电路(ASIC)等逻辑器件之间的标准化串行接口,并且被如今开发的大多数新型高速数据转换器所采用。

有了这个新标准,JESD204B 器件可以轻松地在Ghz范围内进行采样。一些较新的射频数模转换器(RFDAC)的采样速率可以高达9Gsps。以这样的速率进行采样有其缺点,因为这将要求每个串行器 / 解串器(SerDes)通道的输入数据速率达到每秒 90Gbits。由于 JESD204B 标准只能支持最高每秒 12.5 Gbits的速率,所以必须降低数据速率。为了实现这一点,需要使用内插技术。

许多符合 JESD 标准的数模转换器(DAC)在选择内插因子方面有多种选项。这使得用户在选择所需的串行器 / 解串器(SerDes)通道数量以及这些通道的运行速度时拥有更多选择。对于当前的 JESD204B 模数转换器(ADC)来说,这并不是太大的问题,因为它们的采样速度没有那么快。但是,如果用户想要减少通道数量,那么这就会成为一个问题,并且需要进行抽取操作。

在这个例子中,我们展示了一款 DAC,它将使用全部 4 个数模转换器、8 个串行器 / 解串器通道、内插因子为 4,并且数模转换器的最大采样速率为2.5Gsps。为了确定串行器 / 解串器的速率是否在 JESD204B 标准的规格范围内,我们将进行以下计算。

首先,我们将 JESD204B 中使用的八位字节转换为bit。由于每个采样值由两个八位字节组成,所以采样率Fs=2.5Gsps/4=625Msps,每个数模转换器每个采样值将有 1250M八位字节。JESD204B 采用 8b/10b 编码,每个八位字节将由 10 bits组成。所以这就得出每秒 12500 Mbps。

现在总比特率是每秒 12500 Mbits乘以 4 个数模转换器,即等于每秒 50 Gbps。为了使这个速率低于每秒 12.5 Gbps,我们选择 8 个串行器 / 解串器通道,将其降低到每秒 6.25 Gbps。另一个选择是使用 4 个通道,这样速率将达到每秒 12.5 Gbps。这就是客户需要权衡的地方 —— 使用更多通道但速度较慢,或者使用较少通道但速率高得多。他们不能使用少于 4 个通道,因为这将超过 JESD204B 规格中串行器 / 解串器的数据速率。

所以最终JESD204B配置为LMFS=8411,Lane rete=6.25Gsps。

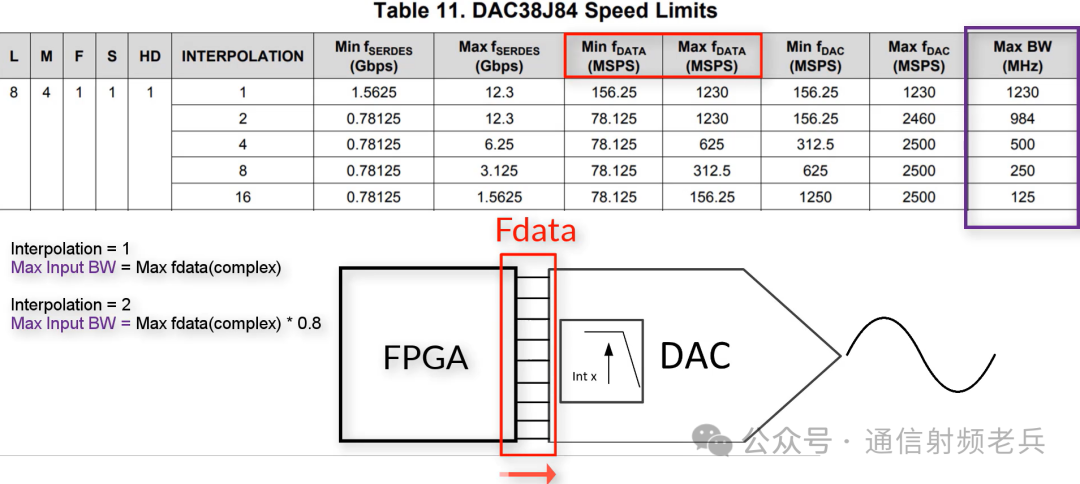

下图,你将看到一个表格,展示了这款数模转换器可以使用的最小和最大采样速率。fData 是并行数据离开 JESD204B 模块并输入到数模转换器数字输入模块的速率。fDAC 是数模转换器的实际采样速率。fDAC 等于 fData 乘以内插因子。由于串行器 / 解串器输出使用内部锁相环(PLL),它们将有一个最小和最大的工作范围。因此,JESD204B 数据转换器有相对较高的最小采样速率。在许多情况下,为了使用最大采样速率,用户必须使用一些内插操作,以使串行器 / 解串器的速率降低到每秒 12.5 Gbps以下,这是 JESD204B 标准所允许的最大速率。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)