计算机组成原理实验报告一

电路仿真需要先建立仿真波形文件,再设置各输入信号在不同时刻的取值,输入/输出信号应包含电路的所有引脚,输入信号的组合应能够反映电路功能表的所有功能。时钟周期的宽度应大于所有操作的时延。实际应用中,时钟周期的开始都用时钟脉冲信号的上升沿来标志,输入信号的长度为时钟周期的倍数、状态变化滞后于时钟脉冲信号,因为许多信号通过时钟脉冲信号产生。使功能仿真方式、时序仿真方式的结果相同,要求时钟脉冲信号的上升沿

实验一 寄存器组的设计

一、实验内容

- 测试 D 触发器的功能。

- 设计具有 1 个读端口、1 个写端口的 4×8 位寄存器组,并验证设计正确性。

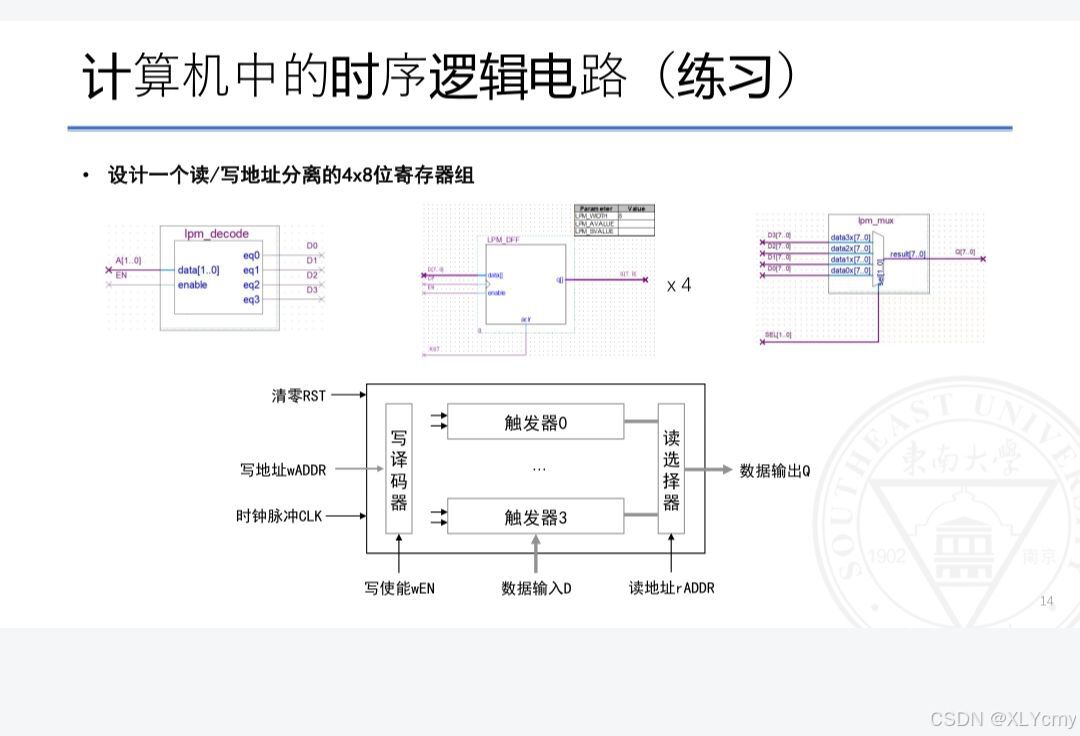

- 如图:

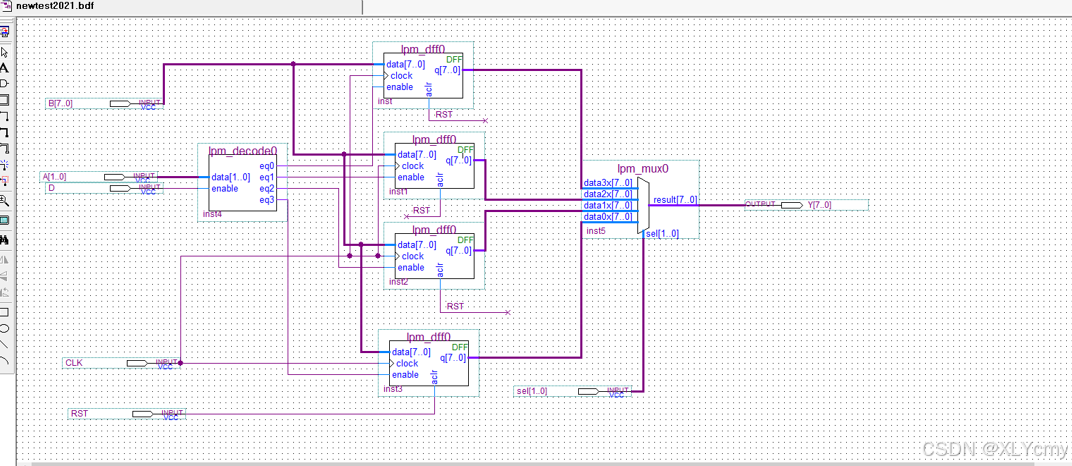

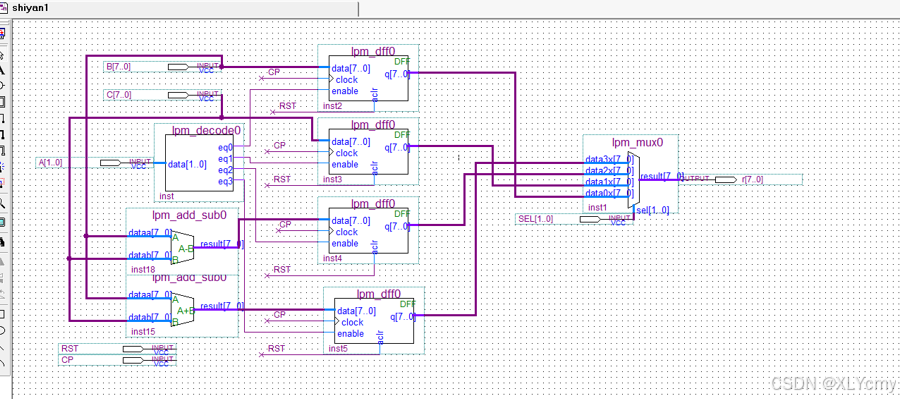

二、电路设计与实现

- 需求分析:即设计一个读/写地址分离的4x8位寄存器组。

- 模块分析:需要一个拥有使能端的写译码器,四个触发器,一个读选择器。触发器有边沿触发、电位触发两种方式,通常,前者称为触发器,后者称为锁存器。触发器的状态在时钟脉冲信号CP上升沿时发生变化(触发)、在其余时间保持不变;锁存器的状态在控制信号 E为高电平时跟随输入端发生变化、为低电平时保持不变(锁存)。

- 整体设计思路:最左边是一个译码器,可以用来选择地址,是一个总线输入,比如说两个输入,输入零零的时候是第一个输出一,输入零一的时候是第二个输出一,那么它就可以选择后面的四个触发器,因为触发器有使能端,只有选中才能进行写入,所以下一步,应该将四个输出接在四个使能端上,达到地址选择的目的,以上这些是一个地址选择的问题,然后,还需要一个四八位的一个总线端,作为数据的输入,这步就是把总线和四个D触发器数据输入都连上就好了,作为数据的输入,并不需要是四个,一个数据的输入端就够了,因为选择地址,不管怎么样,作为数据的输入,只有选中哪个地址的时候,才会把这个数据写在哪个地址的里面,四个都接上一个输入,当选择地址的时候,只会把数据写在选择的那个上面,所以一个输入就够。时钟直接接一起就好了,最后数据选择器就是读地址,D触发器的四个输出接在数据选择器的四个输入,当选择读地址的时候,就会有一个触发器被选择输出。

其余如图所示:

三、电路正确性验证

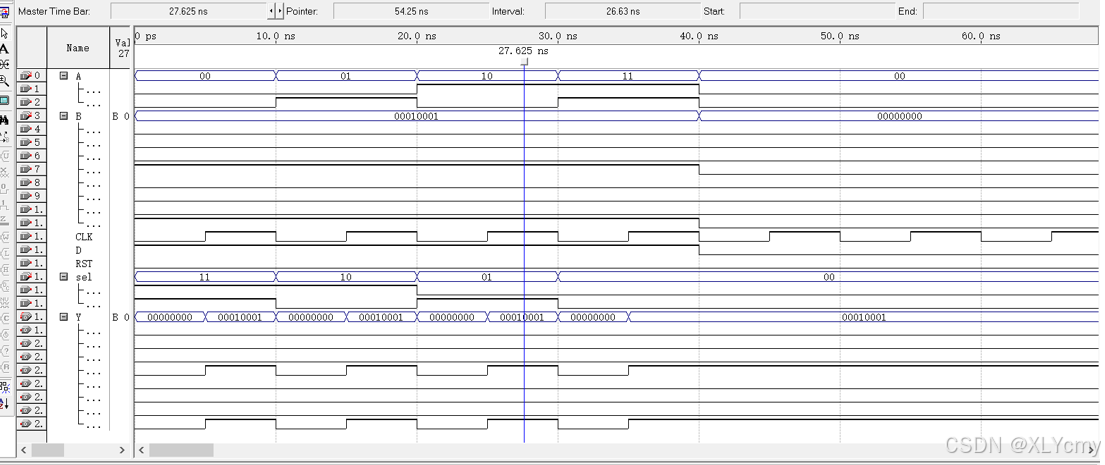

1、电路仿真

触发器功能的测试包括电路实现、电路仿真及结果分析几个步骤,仿真时先采用功能仿真方式得到结果并分析,再采用时序仿真方式查看器件操作的时延特征。电路仿真需要先建立仿真波形文件,再设置各输入信号在不同时刻的取值,输入/输出信号应包含电路的所有引脚,输入信号的组合应能够反映电路功能表的所有功能。注意,时序逻辑电路中,输入信号的时长应是时钟周期的倍数,初始化信号除外;时钟周期的宽度应大于所有操作的时延。实际应用中,时钟周期的开始都用时钟脉冲信号的上升沿来标志,输入信号的长度为时钟周期的倍数、状态变化滞后于时钟脉冲信号,因为许多信号通过时钟脉冲信号产生。使功能仿真方式、时序仿真方式的结果相同,要求时钟脉冲信号的上升沿略早于输入信号的改变,实现方法是,设置时钟脉冲信号时,修改 Time period 参数的 offset 值。

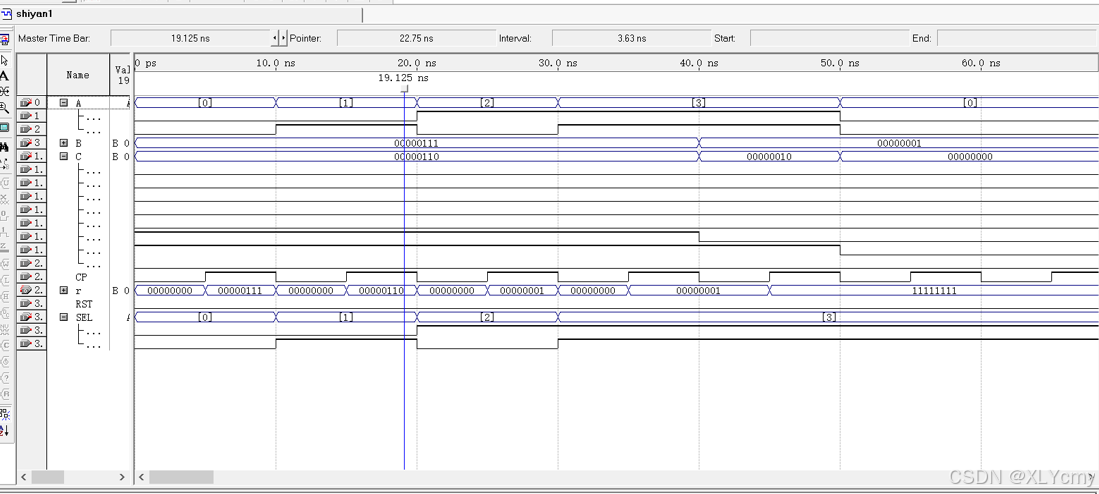

功能仿真波形图如图:

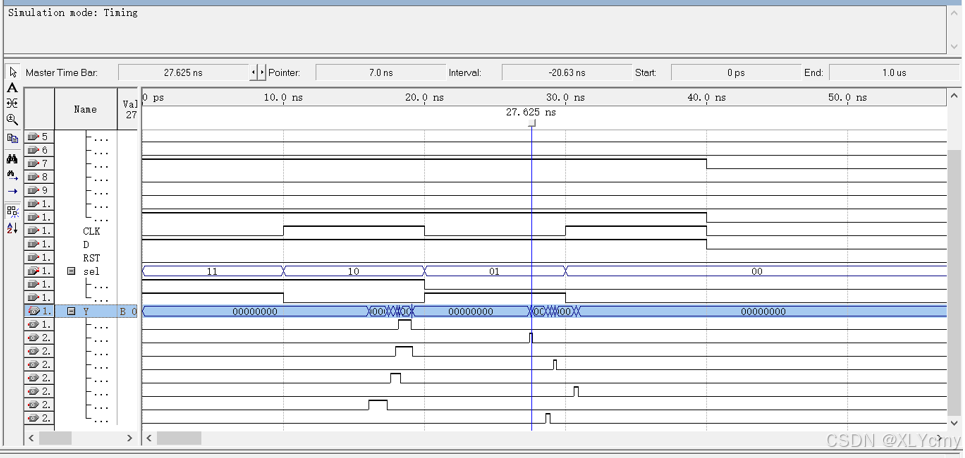

时序仿真波形图如图:

2、结果分析

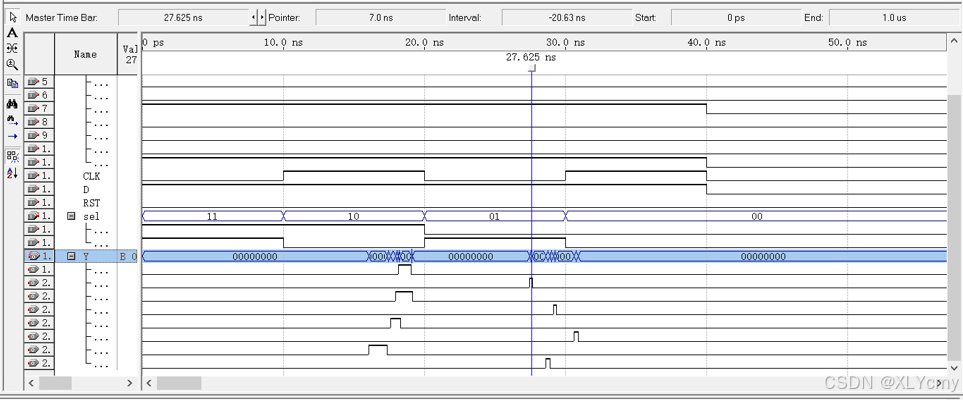

仿真结果十分完美,但是小组一名成员在时序仿真时,出现了如下图所示问题:

后经小组另外一名成员的提醒,发现是clock的输入设置有误,之后改正,如图:

依旧有微小扰动,在小组成员帮助下,最终成果显著。

四、实验小结

本次实验由于较为简单,所以小组成员各自独立实现了一个成功的实验,有成功的仿真,有待改进之处详见三。通过本次实验,我们对QuartusII的使用有了更深层次的体会,对计算机组成原理知识有了更深的理解。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)