PCB阻抗计算

阻抗线计算的两种方式验证

硬件工程师经常要根据项目情况选板子叠层评估PCB走线面积和规划高速阻抗线走线方案,因此阻抗线计算经常要用到,如下记录下个人比较熟悉的两种阻抗计算(仿真)方式。

目录

总体思路:

仿真主要以PCB原厂计算的参数做参考进行仿真拟合,如仿真结果和厂商计算结果一致,则认为仿真计算方式正确,否则就是过程不对或者参数不对,需要反过来排查,直到一致。

一.两种计算方式

1.ADS CILD

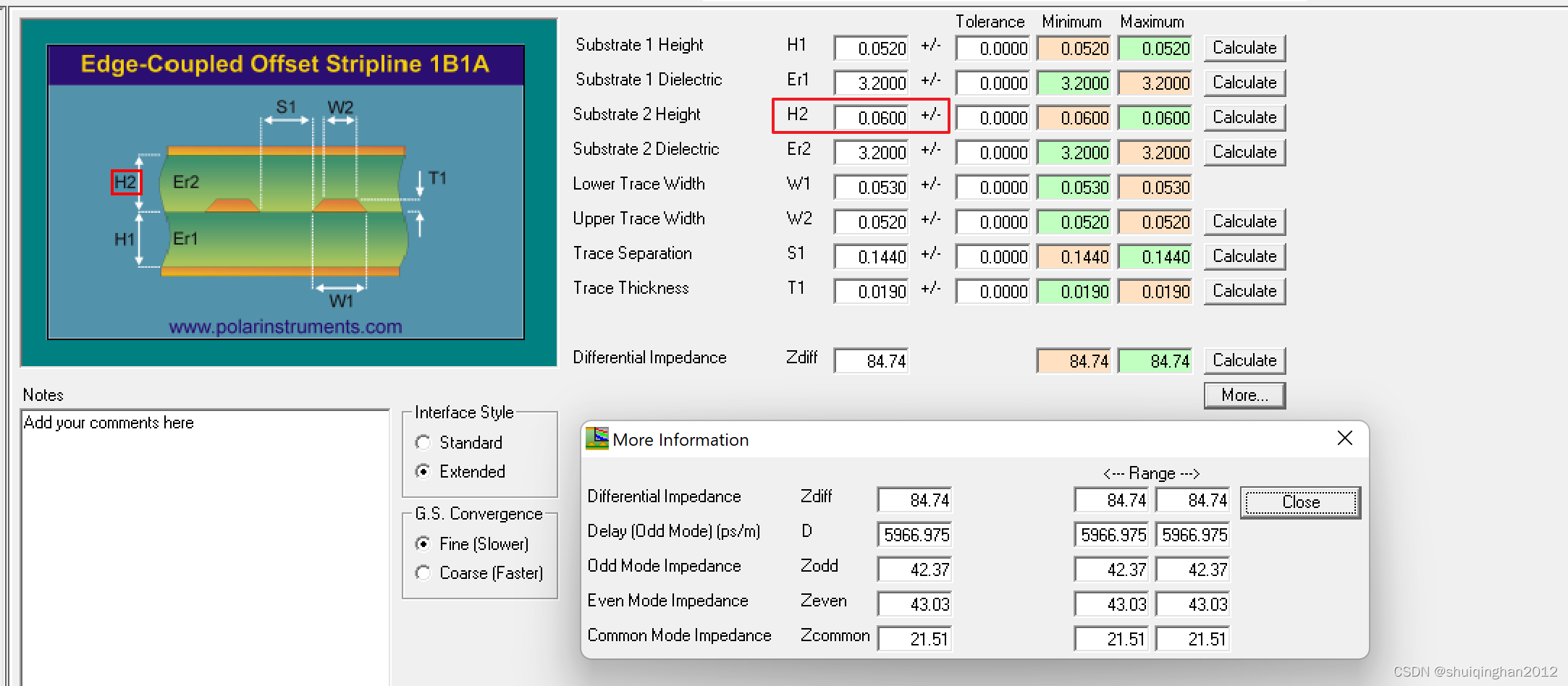

2.SI9000

二.软件使用介绍

CILD使用介绍

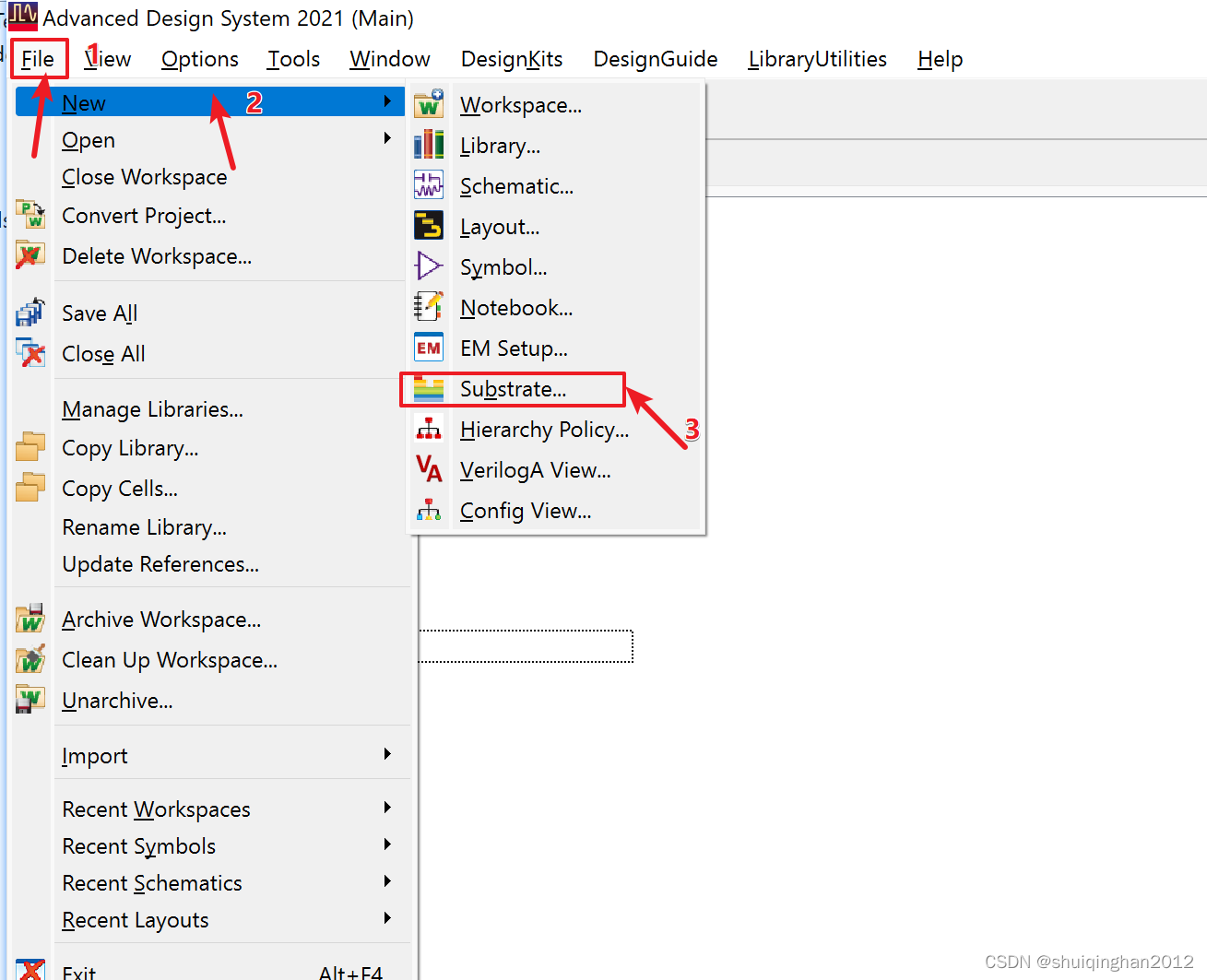

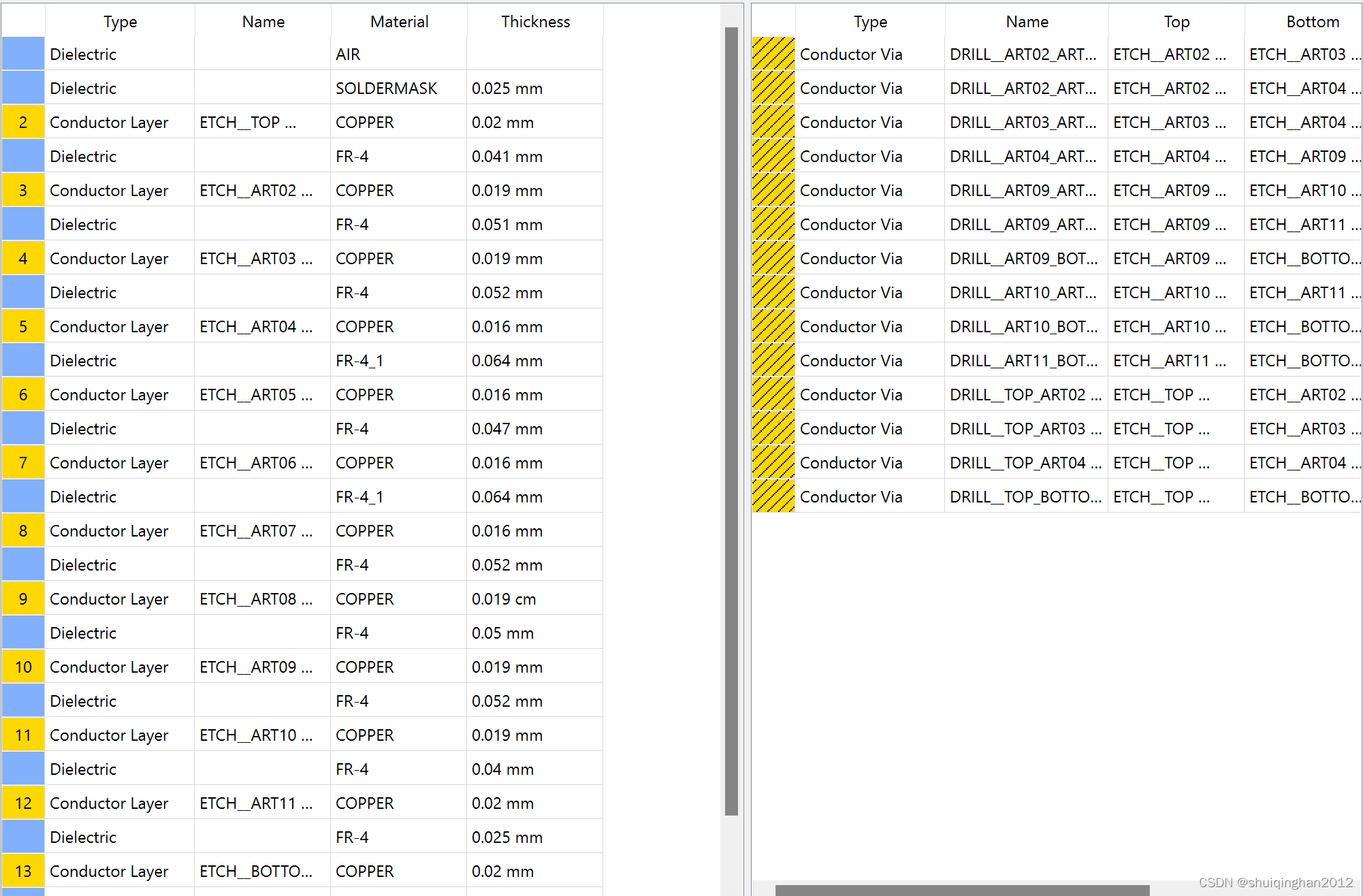

1.新建叠层

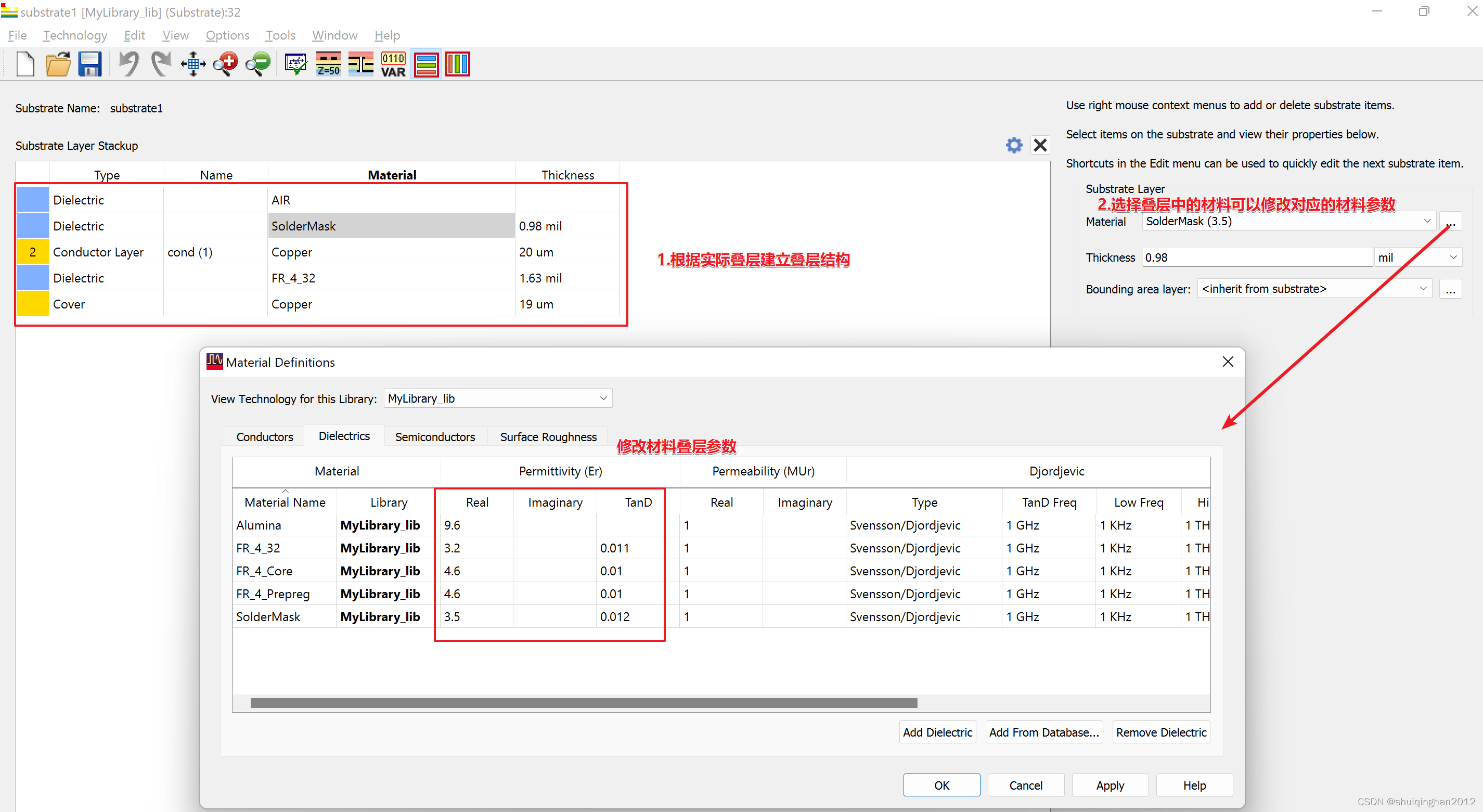

2.修改叠层参数

设置完后save。

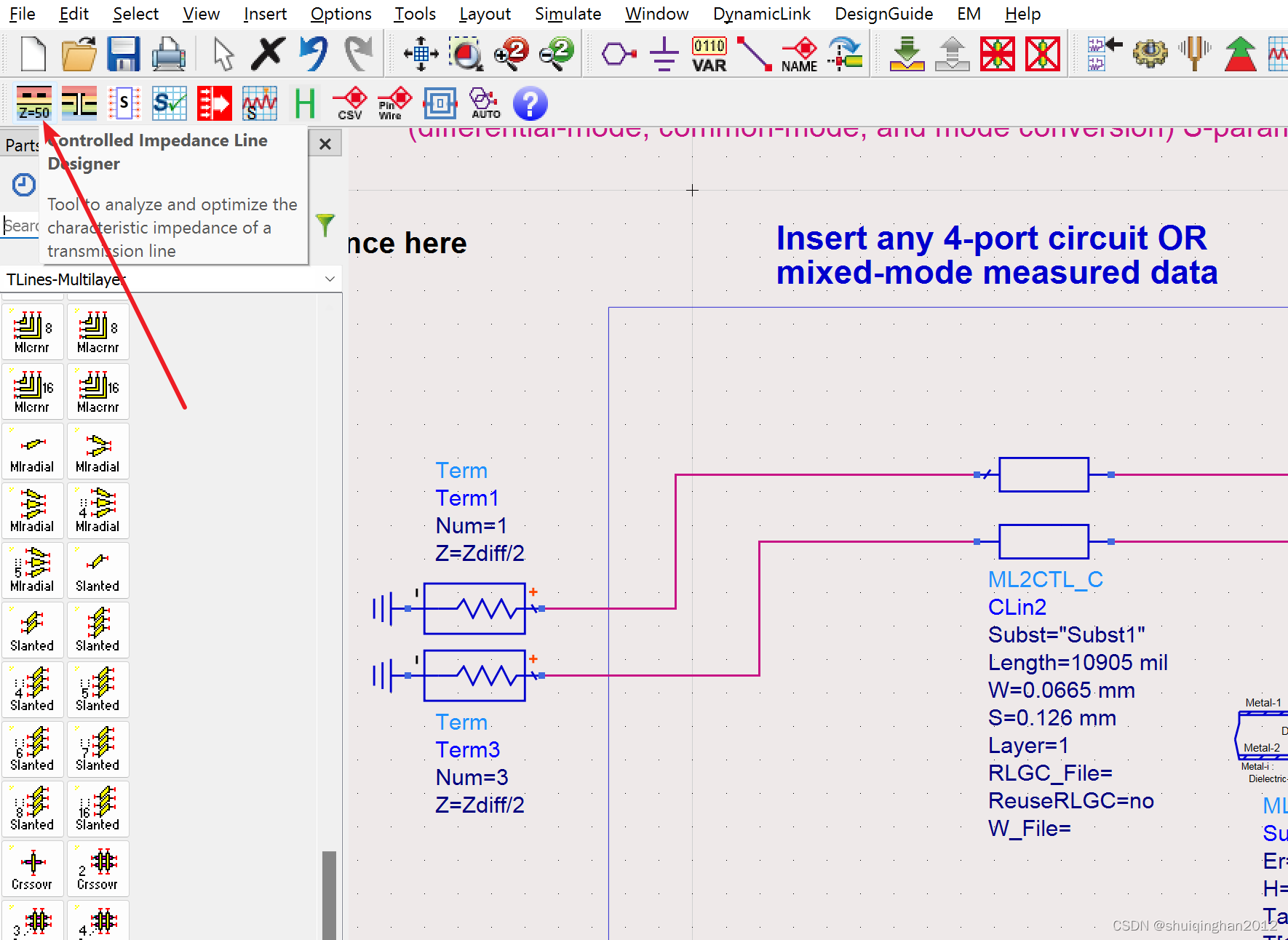

3.在任意原理图页打开阻抗计算

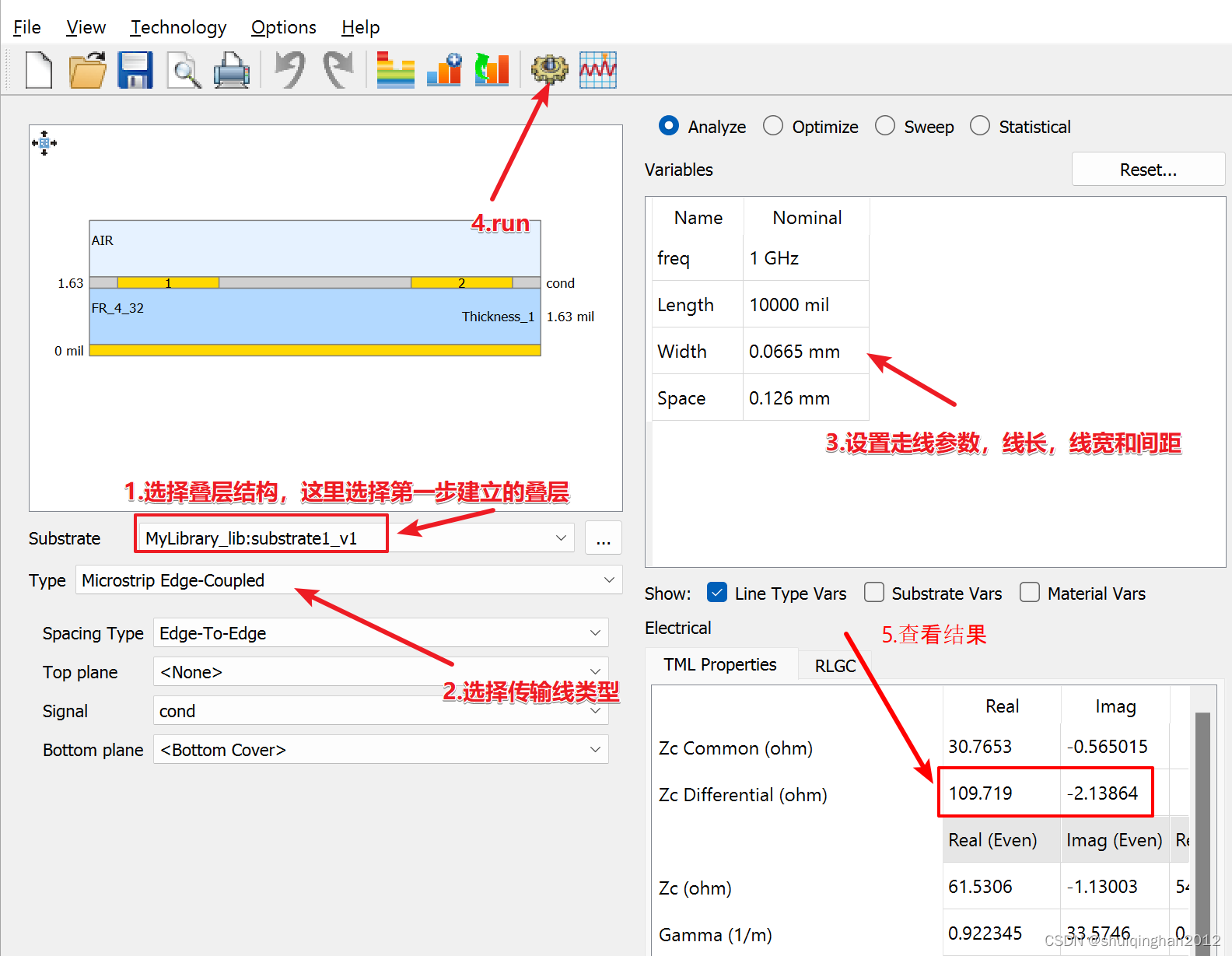

4.走线参数设置并计算阻抗

SI9000的计算教程很多,找找做参考

SI9000阻抗计算教程_qq_38823640的博客-CSDN博客_si9000

这里说明下两个软件的不同,SI9000的所有参数都在第一层,线宽,线距和板材信息等

而CLID的参数是分了层次的,首先是设置叠层结构,叠层结构中基本是选材料和高度信息,材料要单独编辑,再材料菜单中编辑,而走线参数又在CLID中编辑,这种设置更符合人类的分层抽象思维,但单纯从0开始计算阻抗时一开始使用有些不适应。

三.验证阻抗线

如下厂商提供的阻抗走线宽度,根据此计算表层阻抗是否和厂商计算一致。

|

阻抗线要求 |

单:mm |

||||||

|

阻线层 |

参考层 |

单线 |

差分 |

||||

|

40欧姆 |

45欧姆 |

50欧姆 |

85欧姆 |

90欧姆 |

100欧姆 |

||

|

L1 |

L2 |

0.112 |

0.09 |

0.072 |

0.068/0.062 |

0.061/0.067 |

0.050/0.078 |

1.单端50ohm计算

1.1.ADS CILD

1).输入叠层结构

检查发现Layout导入的叠层和厂商提供的不相同,根据厂商叠层修改

不同的原因可能是layout只导入了最初的叠层,后来根据需求厂商调整了叠层,layout没再修改layout中的叠层

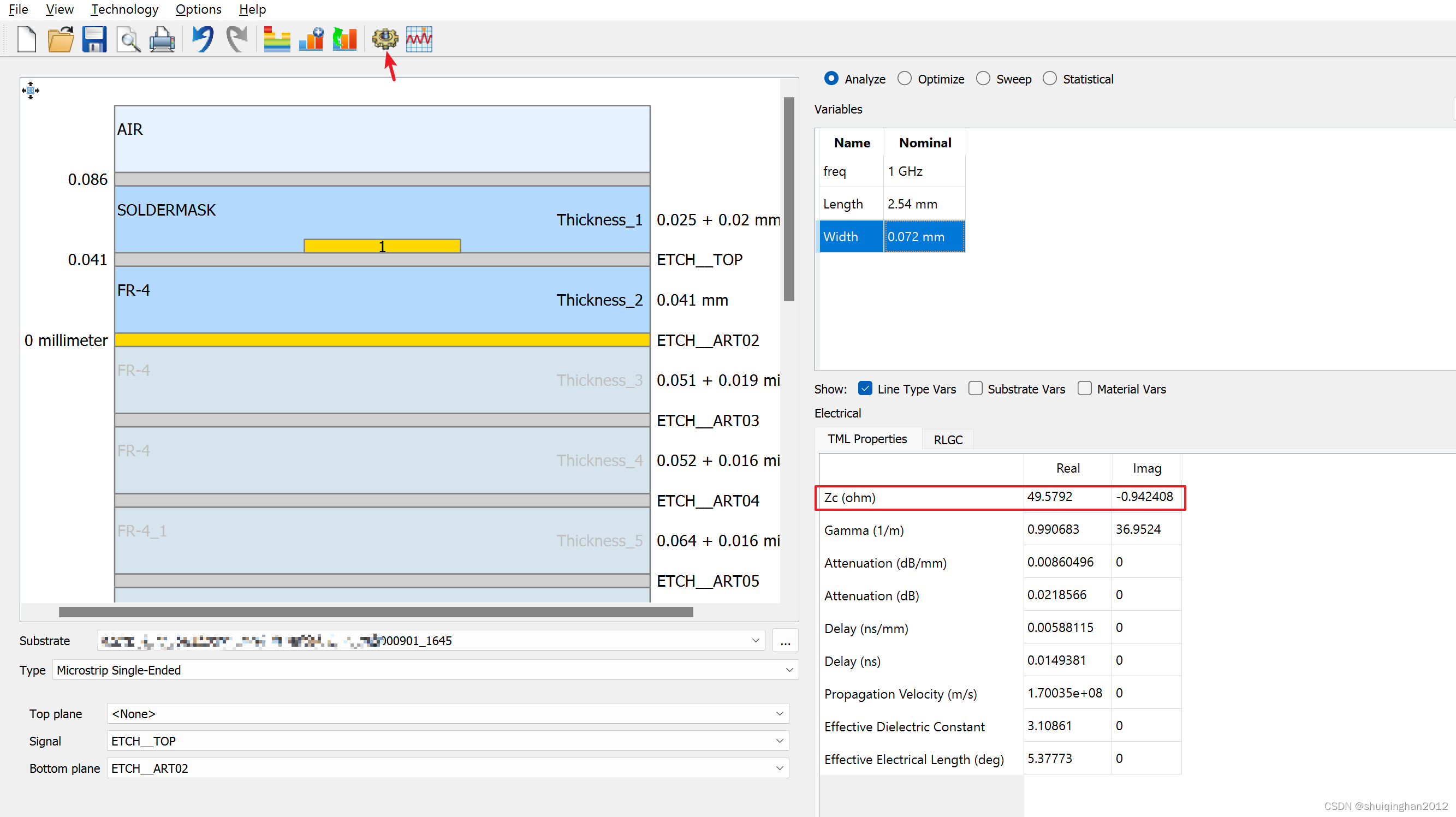

2).50 ohm 微带线计算

结论:50ohm 微带线计算基本相符,这里注意,频率越高,阻抗会越低,5G 计算时48.x. 和厂商提供数据基本一致。

因为实际Layout时微带线并不是完全没有导线,周边还有地

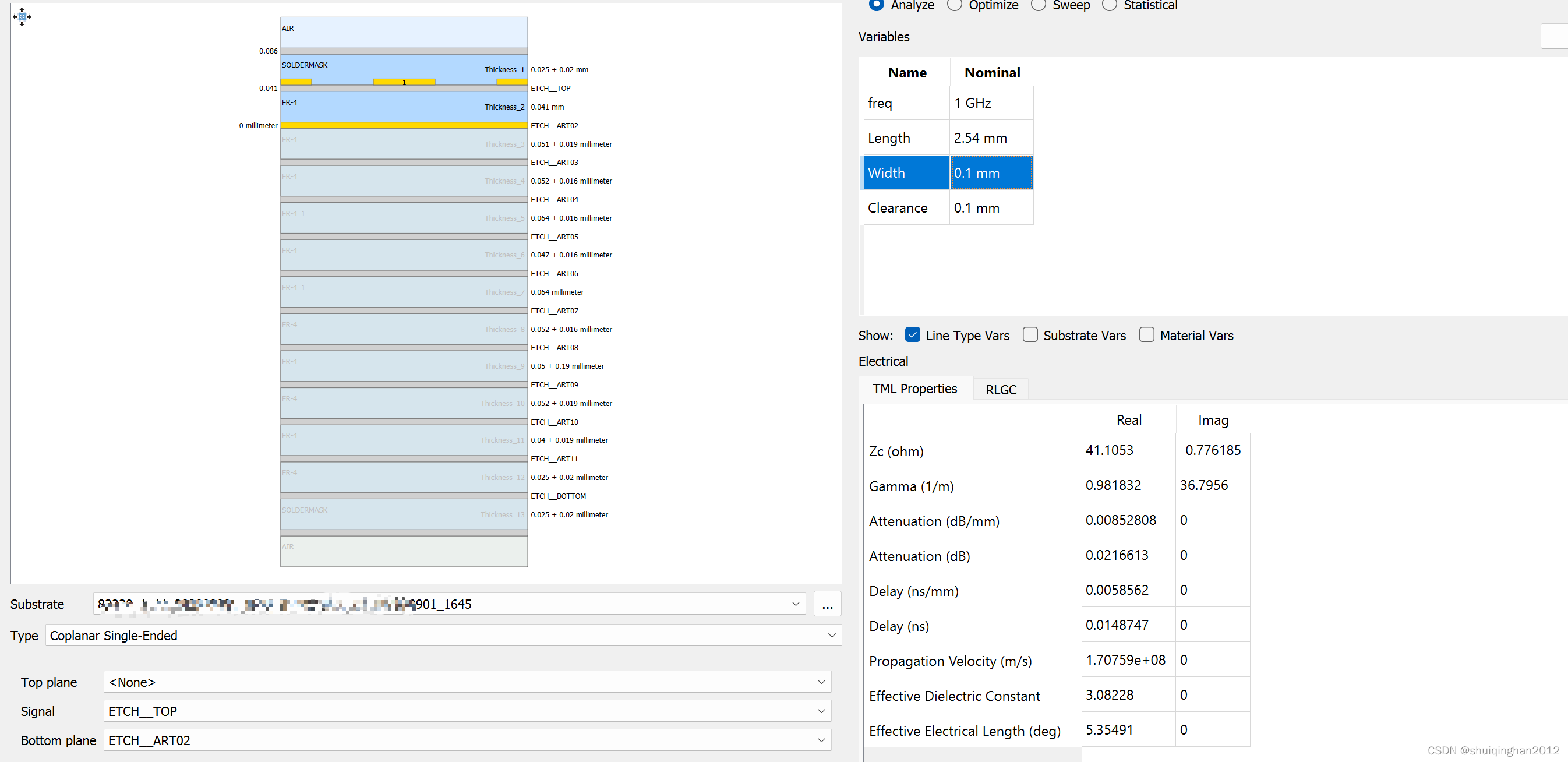

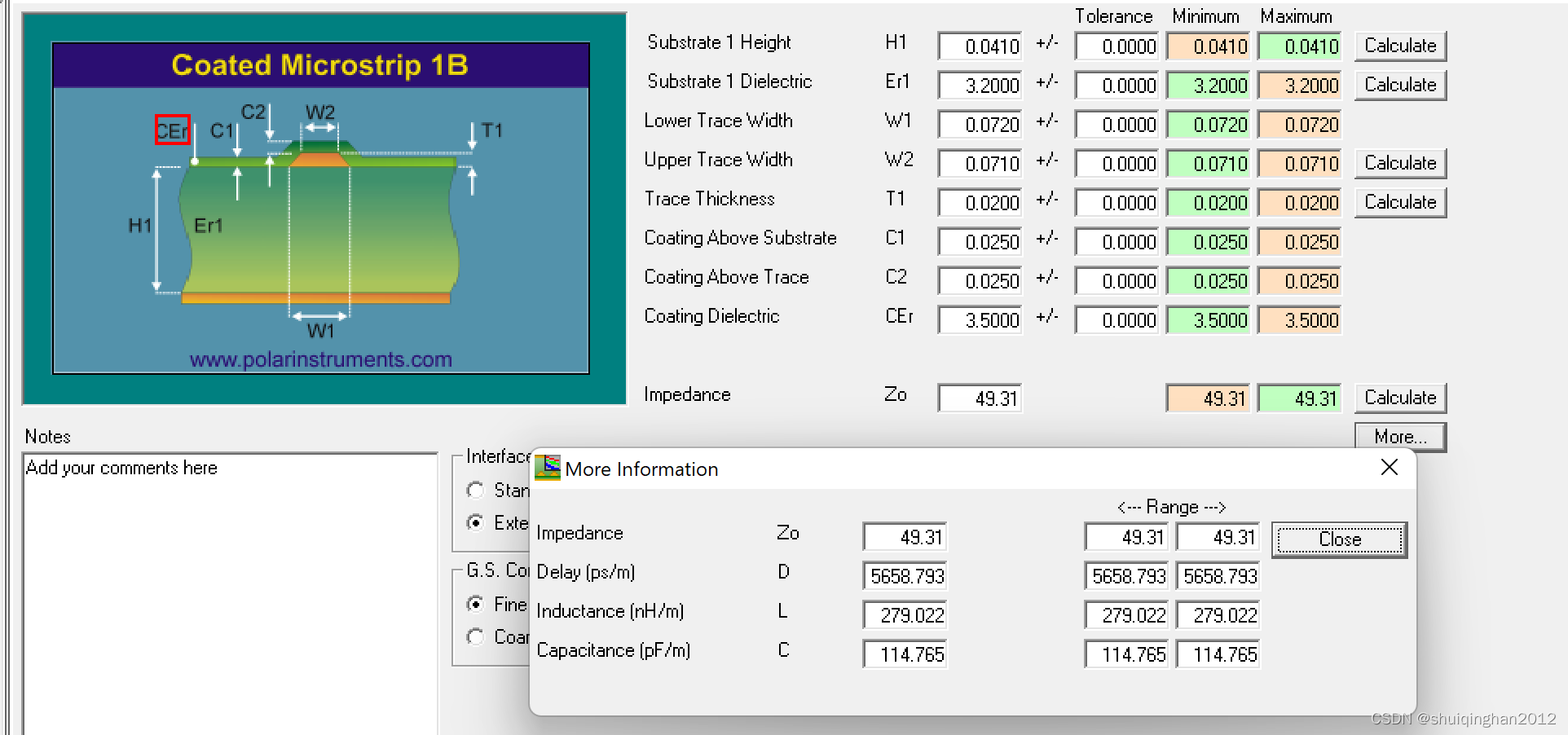

1.2. SI9000

差分阻抗

2.差分阻抗计算

90ohm

2.1 CILD计算

2.2 SI9000计算

使用SI9000计算 结果相当,注意这里H1是T1+PP1的厚度

结论

结论:SI9000和ADS CTLD 计算都和厂商一致

这说明以上计算都是正确的,在评估新的叠层时直接用这两种方式计算即可。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)