计算机组成原理知识点汇总(三)存储器

当有一种情况,如下:CPU访问主存时,由于主存SDPAM虽然容量大,但是CPU访问它很慢。我们知道,cache缓存SPRAM虽然容量小,但是CPU访问它快。于是我们会在CPU和主存中间加一个cache把常用数据放到cache中这样我们平常访问,访问cache就可以了,而不常用的东西放到主存里,这样相当于提高了效率。于是就有了下图:这就是高速缓冲储存器。

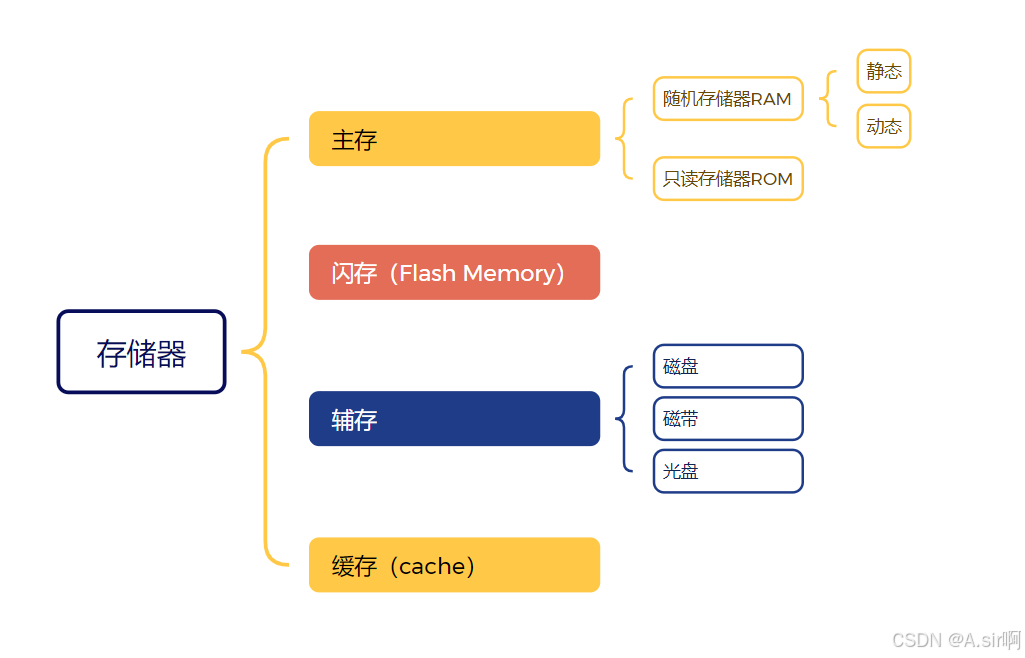

一、存储器的分类

-

根据存储介质:

- 半导体存储器:如动态随机存取存储器(DRAM)、静态随机存取存储器(SRAM)、闪存等。

- 磁性存储器:如硬盘驱动器(HDD)、磁带等。

- 光学存储器:如CD、DVD、蓝光光盘等。

-

根据访问方式:

- 随机存取存储器(RAM):可以随机访问任何存储位置,通常用于临时数据存储。

- 只读存储器(ROM):数据在制造时已写入,通常用于存储固件或系统启动程序。

-

根据用途:

- 主存储器:通常指计算机中的RAM,主要用来临时存储正在处理的数据和程序。

- 辅存储器:如硬盘、SSD等,主要用于长期存储数据。

-

根据技术类型:

- DRAM:动态随机存取存储器,存储单元需要定期刷新。

- SRAM:静态随机存取存储器,不需要刷新,速度较快,但成本较高。

- Flash Memory:一种非易失性的存储器,广泛应用于USB闪存驱动器和固态硬盘(SSD)。

图示:

二、层次结构及特点

| 器件 | 所属层次结构 | 速度 | 容量 | 价位 | ||

| 寄存器 | CPU内 | CPU | 主机 | 快 | 小 | 高 |

| 缓存 |

逐 渐 递 减 |

逐 渐 递 增 |

逐 渐 递 减 |

|||

| 主存 | ||||||

| 磁盘 | 辅存 | |||||

| 光盘 | ||||||

| 磁带 | 慢 | 大 | 低 | |||

三、主储存器(主存)

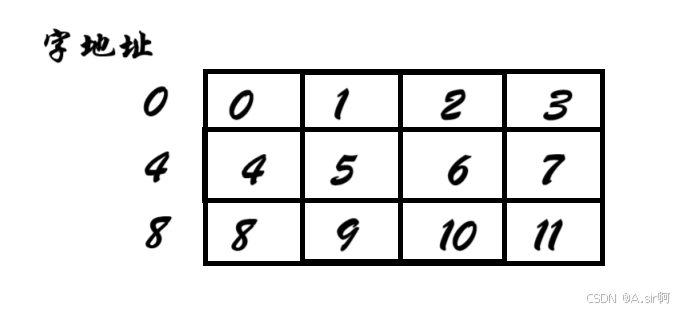

(1)存储单元中的地址分配

一般来说,8个位=1字节 4个字节=1个字

然后引入一个概念:储存单元,即常说的字节。

所以,现在一个储存单元容纳8个位,而四个储存单元构成了一个字。

而每个字,有自己的地址。

如果给每个存储单元编号0,1,2,3……

那么由4个存储单元构成的字,也就有了编号:0,4,8……

所以字的地址就依次有:0,4,8……

所以下面这张图你就理解了:

每一个小格代表一个存储单元,进行编号后,取每行首个单元的编号,作为了字的地址

根据以上两种编号方式,我们有了两种寻址方式:

- 按字节寻址:就是0,1,2,3……

- 按字寻址:就是0,4,8,12……

附加练习题:

1.设地址线为24根,按字节寻址,有多少存储字?

每根地址线可表示0和1

所以24根地址线可表示2^24个存储单元

2^24 字节 = 16,777,216 字节(即16MB)

2.如果储存容量不变,若字长为16位,按字寻址有多少存储字?

存储容量仍然是16MB,一个存储单元有8个位

原先是按字节寻址,所以一个存储单元容纳一个存储字

但现在按字寻址,每个字长为16位,所以变成了两个存储单元才能容纳一个存储字

所以是2^24除2=2^23字节

(2)储存容量公式

储存容量=存储单元个数x存储字长

(3)技术指标

- 储存容量

- 存储速度

- 存储器带宽

四、半导体存储芯片

(1)相关概念

读写控制线:传递CPU的控制信号

地址线:将CPU需要的地址传输到译码驱动中,然后由译码驱动进行翻译,再进行寻址。

数据线:将存储体中的数据读出,放入CPU,或将CPU计算完毕的数据存入存储体。

片选线:用于选择具体的存储芯片。

(2)计算存储容量

n是地址线的数量,m是数据线条数

存储容量=2^n × m

(3)译码驱动方式

线选法

通过将多个存储单元的地址与线的编号来进行选择

-

优点:

- 简单易实现:通过简单的解码方式,可以很方便地实现存储单元或外设的选择。

- 寻址范围大:可以通过增加地址线来扩展可寻址的存储单元数目。

-

缺点:

- 硬件成本较高:随着存储单元数量的增加,需要增加更多的地址线和译码器,从而增加了硬件成本。

- 解码复杂度增加:若存储单元数目极大,译码的复杂度会显著增加,导致系统的性能下降。

重合法

通过对行和列的编号,然后选择行和列来确定具体的存储单元

-

优点:

- 节省硬件资源:通过共享信号,减少了控制信号的数量,降低了硬件成本。

- 适用于大规模系统:在需要大规模存储设备的系统中,重合法能够显著减少布线和控制的复杂性。

-

缺点:

- 控制延时增加:由于多个存储单元或设备共享同一条选择线或地址线,可能导致系统的延迟增加。

- 实现较复杂:需要通过时序控制来确保每个存储单元或设备在不同时间点被选中,设计较为复杂。

五、随机存储器RAM

(1)静态随机存储器SRAM

储存原理:互锁触发器

集成度:低

功耗:大

速度:快

常用于:cache(缓存)

(2)动态随机存储器DRAM

储存原理:电容——>电容里的电会消失,所以要对储存单元恢复一次状态,即刷新(再生)

集成度:高

功耗:小

速度:慢

常用于:主存

(3)刷新

集中刷新:读写完成后,集中刷新,有死区

分散刷新:读写一行,刷新一行,无死区

异步刷新:每隔一定时间刷新一行,每行每隔一定时间刷新一次

六、只读存储器ROM

ROM的内容一旦写入,就无法或很难修改。因此,ROM常用于存储固件或系统启动程序。

补充:

闪存(Flash Memory):是EEPROM的一种特例,允许在块级别进行擦除和重写,广泛应用于USB闪存驱动器、SSD和其他存储设备。

七、储存器与CPU的连接

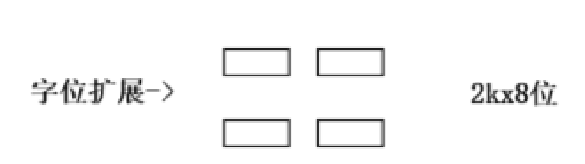

(1)位扩展

增加存储字长

比如,我们让如下数据块代表1kx4位

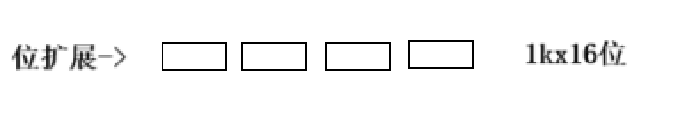

所谓位扩展,就是将其横向排列为:

1kx4位变成了1kx16位,就是增加存储字长

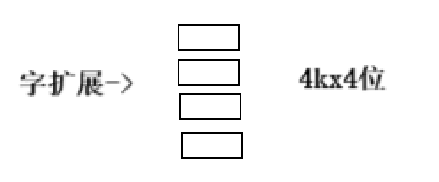

(2)字扩展

增加存储字数量

所谓字扩展,就是将其纵向排列为:

1kx4位变成了4kx4位,就是增加存储字数量

(3)字位扩展

字位扩展就是两个都增加,既横着加又竖着加

八、提高访存速度措施

(1)调整主存结构

1.单体多字

存储器中只有一个存储体,但该存储体可以同时存储多个“字”数据。

存储器的容量有限,但通过位扩展,在一个存储体中存储多个字的数据。

指令和数据在主存内连续存放

2.多体并行

存储器中有多个存储体。各存储体可以并行工作,提高存储容量和效率。

高位交叉:顺序编址

高位地址译码产生片选信号,选择不同的存储模块。

低位地址选择对应的存储模块内对应的存储单元。

低位交叉:轮流编址

低位地址作为选择不同的存储模块

高位地址则对应每个存储模块内的存储单元

(2)采用高速储存器部件

(3)采用高速缓冲储存器

九、高速缓冲储存器cache

(1)介绍

当有一种情况,如下:

CPU访问主存时,由于主存SDPAM虽然容量大,但是CPU访问它很慢。

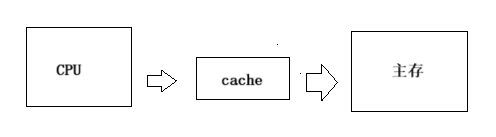

我们知道,cache缓存SPRAM虽然容量小,但是CPU访问它快。

于是我们会在CPU和主存中间加一个cache

把常用数据放到cache中

这样我们平常访问,访问cache就可以了,而不常用的东西放到主存里,这样相当于提高了效率。

于是就有了下图:

这就是高速缓冲储存器

(2)命中

CPU在cache中查找到数据称为数据命中

(3)地址映射

地址映射是cache和主存之间的事

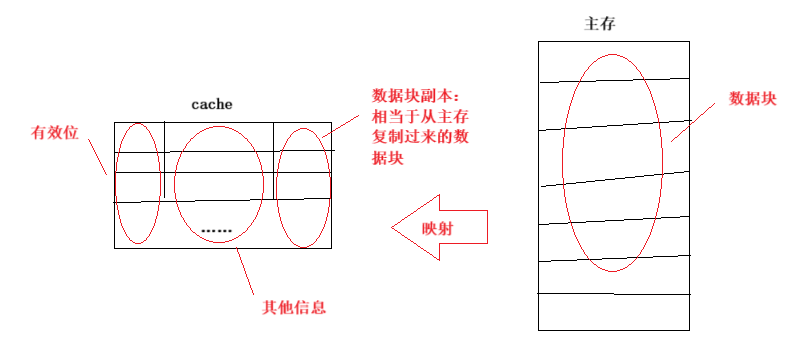

如图是二者的构成以及关系:

有效位:当cache中的某一行存在了数据块副本时,有效位置1,用来标识

映射分为三种:

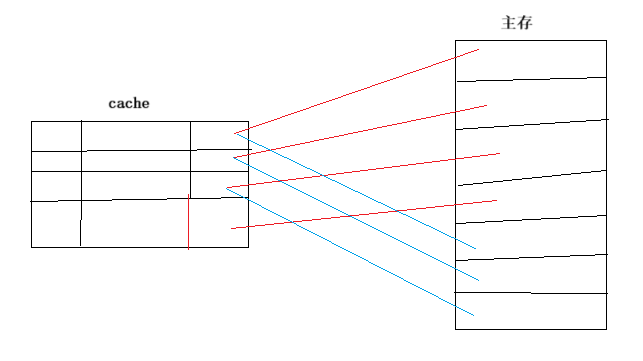

直接映射

每个主存数据块映射到cache中的一个固定行

命中率低,查找成本低

即,主存从上到下,第一个数据块放cache第一行,

第二个数据块放cache第二行

……

第n个数据块放cache第n行

当cache每一行都用了之后

主存接下来的n+1数据块重新放到cache的第一行

n+2数据块放到cache第二行,以此类推……

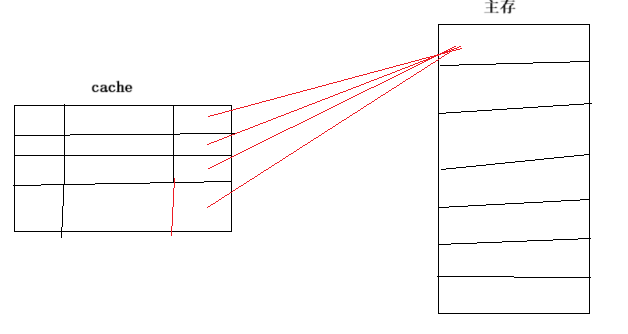

全相联映射

每个主存数据块都可映射到cache中任何一行

命中率高,查找成本高

组相联映射

命中率高,成本低

将cache所有行划分成固定的组,每组k行

主存数据块直接映射于组

主存的数据块所对应的组内,又采取全相联映射

十、存储器的校验

校验,即纠错。

(1)合法编码

假设当前有3位二进制数的编码

若每次只有一个差异数字,如:000,001,010,011,100,101,110,111

若其中有一个数字是错误的,比如000变成了001,这时错误代码混在正确代码里

机器分辨不出来哪个001是正确的,哪个001是错误的,所以是检0位错、纠0位错

若每次只有两个差异数字,如:000,011,101,110

若其中有一个数字是错误的,比如000变成了001,由于机器中不存在001的代码

所以可以检查出来错误代码,所以是检1位错、纠0位错

纠0位错:错误码(001)与原码字(000)的距离为 1,同时与其他合法码字(如 011)的距离也为 1(001 与 011 仅第 2 位不同)。此时,错误码与多个合法码字的距离相等,无法唯一确定纠正目标,因此不具备纠错能力。

同理,若每次只有三个差异数字,如:000,111

则检1位错,纠1位错

从中我们可以发现一个公式:

L-1 = D + C

L:编码的最小距离(每次差异几个数字)

D:检测错误的位数

C:纠正错误的位数、

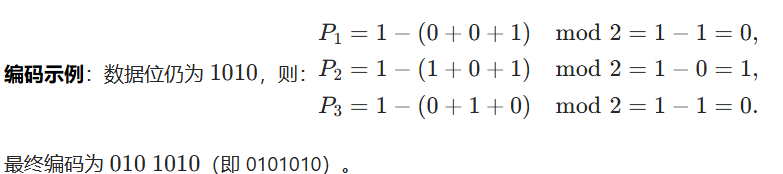

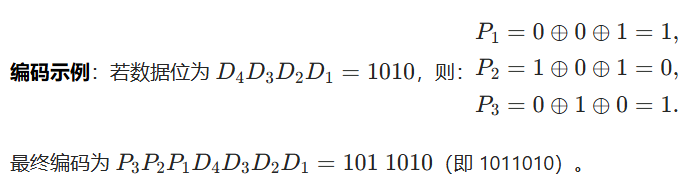

(2)汉明码

汉明码分为奇校验、偶校验。

- 偶校验:每组数据位与校验位的二进制值之和为偶数(包括校验位本身)。

- 奇校验:每组数据位与校验位的二进制值之和为奇数。

校验位通常位于 2^i 位(即第 1、2、4、8、… 位)

例,校验位为![]() 则总编码为

则总编码为![]()

奇校验

每组数据位的二进制和为奇数,因此校验位为数据位和的奇偶性取反

偶校验

每组包含特定的数据位,校验位 的值由对应组内数据位的异或(XOR)结果决定(异或本质是偶校验求和)

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)