一份EtherCAT主站的FPGA Verilog代码 ethercat 主站 FPGA ve...

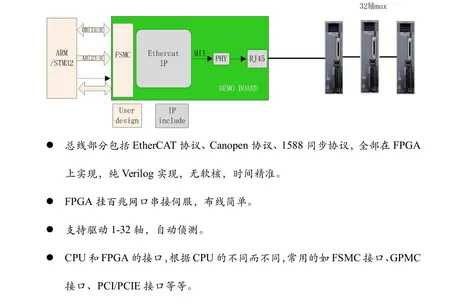

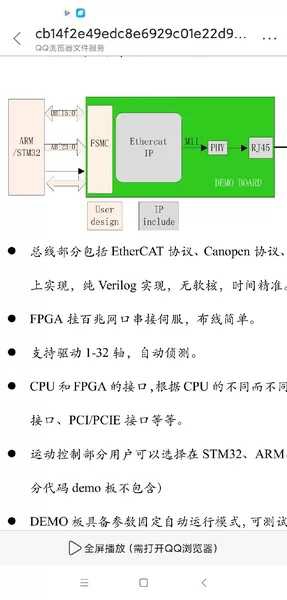

这是一个完整的EtherCAT 主站系统,基于 FPGA 实现,支持最多 32 个伺服轴的实时同步控制。系统通过 EtherCAT 协议与从站(伺服驱动器)通信,实现高性能的多轴运动控制,适用于工业自动化、机器人、CNC 等场景。初始化阶段- FPGA 上电后,ARM 配置伺服参数(如 SM 地址、周期时间)。- 通过 SDO 配置伺服参数(如模式、增益等)。- 伺服依次进入PreOp→SafeO

一份EtherCAT主站的FPGA Verilog代码 ethercat 主站 FPGA verilog 代码 使用FPGA逻辑实现EtherCAT协议,实现主站DC功能。更加突出了EtherCAT现场总线的同步性能及高效性 基于FPGA的EtherCAT主站设计研究 基于FPGA的EtherCAT主站方案 基于FPGA的EtherCAT主站研究 一种基于FPGA实现的EtherCAT主站运动控制器的制作方法 基于FPGA的EtherCAT主站实现与高性能运动控制 基于FPGA的高性能硬件EtherCAT主站研究

一个 EtherCAT 主站(EtherCAT Master)的 FPGA 硬件逻辑,用于控制多个伺服驱动器(servo drives)的同步运动控制。以下是修正后的详细功能说明:

🧠 **系统总体功能概述**

这是一个完整的 EtherCAT 主站系统,基于 FPGA 实现,支持最多 32 个伺服轴的实时同步控制。系统通过 EtherCAT 协议与从站(伺服驱动器)通信,实现高性能的多轴运动控制,适用于工业自动化、机器人、CNC 等场景。

📁 **模块功能分解**

1. **`ECAT_TOP.v`**

- 顶层模块,集成所有子模块。

- 负责时钟生成、复位控制、接口调度。

- 连接外部以太网 PHY、ARM 处理器接口(如 GPIO、手轮、参数配置等)。

2. **`ECAT_ARB.v`**

- 仲裁器,管理多个伺服轴的初始化顺序。

- 根据

Wkc(Working Counter)判断伺服初始化完成状态。 - 生成伺服索引、参数设置序列、安全状态信号。

3. **`ECAT_CONST.v`**

- 常量存储器,存储 EtherCAT 初始化、同步、参数设置等阶段所需的命令数据。

- 使用

case语句实现 ROM 功能,地址由ECATARB和ECATSYNC提供。

4. **`ECAT_INIT_CTRL.v`**

- 初始化控制器,协调伺服驱动器的启动流程(PreOp → SafeOp → Op)。

- 支持 SDO(Service Data Object)参数读写,用于伺服参数配置。

5. **`ECAT_SYNC.v`**

- 分布式时钟(DC)同步模块,实现所有伺服的时间同步。

- 通过读写 ESC(EtherCAT Slave Controller)寄存器(如 0x900, 0x910, 0x920, 0x928)完成时钟校准。

6. **`ECAT_PROCESS_DAT_REF.v`**

- 过程数据刷新控制器,周期性发送 PDO(Process Data Object)命令。

- 根据系统时间和循环周期(如 2ms)生成同步触发信号(

RefReq)。

7. **`ETH_DAT_TX.v`**

- 以太网数据发送构造器,组装 EtherCAT 帧:

- 初始化命令帧

- 同步帧(DC)

- 过程数据帧(PDO)

- SDO 参数读写帧

8. **`ETH_TX.v`**

- 以太网发送控制器,处理 MAC 层封装、CRC32 计算、数据帧发送。

9. **`ETH_RX.v`**

- 以太网接收解析器,解析从站响应:

- 提取伺服状态字、实际位置、SDO 响应等。

- 检测超时、链路故障(

chain_bad)。

10. **`Interface.v`**

- ARM-FPGA 接口模块,实现双端口寄存器映射。

- 提供伺服控制字(CtlW)、目标位置(TargetPos)的写入接口。

- 读取伺服状态字(Sts)、实际位置(EncoderPos)、故障信息等。

11. **`pos_buf.v`**

- 位置缓冲区,实现目标位置的 FIFO 管理。

- 支持抖动控制、虚拟轴模式、手轮输入。

12. **`SERVO_CTLW.v`**(未完整提供)

- 伺服控制字状态机,处理伺服使能、回零模式等控制流程。

🔄 **工作流程简介**

- 初始化阶段:

- FPGA 上电后,ARM 配置伺服参数(如 SM 地址、周期时间)。

- 通过 SDO 配置伺服参数(如模式、增益等)。

- 伺服依次进入PreOp→SafeOp→Op状态。

- 同步阶段:

- 主站与参考从站同步系统时间。

- 所有从站校准本地时钟,实现纳秒级同步。

- 运行阶段:

- 主站周期性发送 PDO 命令(控制字、目标位置)。

- 从站返回状态字、实际位置。

- 支持在线参数修改、故障诊断、手轮干预。

⚙️ **关键特性**

- 支持轴数:最多 32 轴(可配置)

- 同步精度:支持分布式时钟(DC),精度可达纳秒级

- 通信周期:可配置(典型 1~4ms)

- 接口:

- RMII 接口连接以太网 PHY

- 并行总线连接 ARM 处理器

- GPIO、手轮、数字 IO 扩展

- 功能:

- 伺服参数配置(SDO)

- 过程数据交换(PDO)

- 分布式时钟同步(DC)

- 虚拟轴模拟

- 故障诊断与链断检测

✅ **总结**

这套代码是一个完整、高性能的 EtherCAT 主站 IP 核,适用于 FPGA 实现的多轴实时运动控制系统。其设计严谨,支持标准的 EtherCAT 协议栈,具备工业级的可靠性和灵活性。

一份EtherCAT主站的FPGA Verilog代码 ethercat 主站 FPGA verilog 代码 使用FPGA逻辑实现EtherCAT协议,实现主站DC功能。更加突出了EtherCAT现场总线的同步性能及高效性 基于FPGA的EtherCAT主站设计研究 基于FPGA的EtherCAT主站方案 基于FPGA的EtherCAT主站研究 一种基于FPGA实现的EtherCAT主站运动控制器的制作方法 基于FPGA的EtherCAT主站实现与高性能运动控制 基于FPGA的高性能硬件EtherCAT主站研究

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)