锁相环环路滤波器计算公式_锁相环是如何锁相的?

锁相环是一种能够自动跟踪输入信号相位和频率的负反馈系统,应用广泛。在并网逆变器以及PFC系统中电网电压频率和相位往往是关键的控制信息,这里以单相为例,分析锁相环是如何得到电网电压相位和频率的。锁相环的基本结构图如下图所示,主要包括三部分:鉴相器PD、环路滤波器LF以及压控震荡器VCO;PD负责把输入信号与系统内部同步信号的相位差转换为与之相关的电压信号,然后经过LF滤波或补...

锁相环是一种能够自动跟踪输入信号相位和频率的负反馈系统,应用广泛。在并网逆变器以及PFC系统中电网电压频率和相位往往是关键的控制信息,这里以单相为例,分析锁相环是如何得到电网电压相位和频率的。

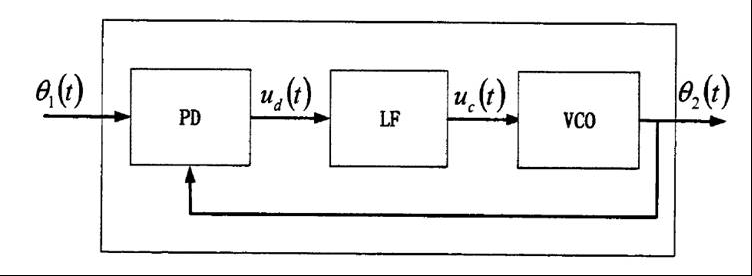

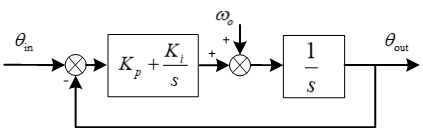

锁相环的基本结构图如下图所示,主要包括三部分:鉴相器PD、环路滤波器LF以及压控震荡器VCO;PD负责把输入信号与系统内部同步信号的相位差转换为与之相关的电压信号,然后经过LF滤波或补偿后去控制VCO,VCO的输出改变系统内部同步信号的频率和相位,进而形成负反馈,最终使内部同步信号跟踪电网电压。

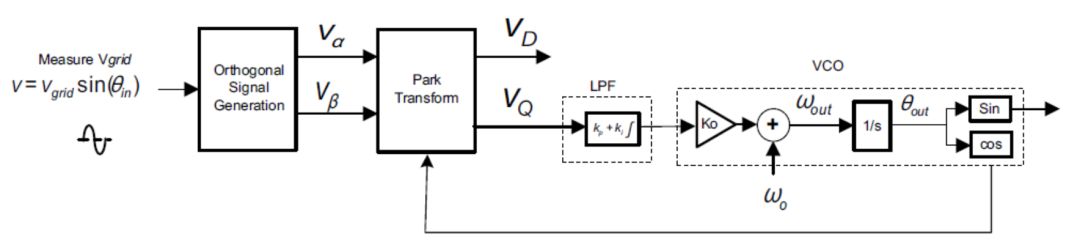

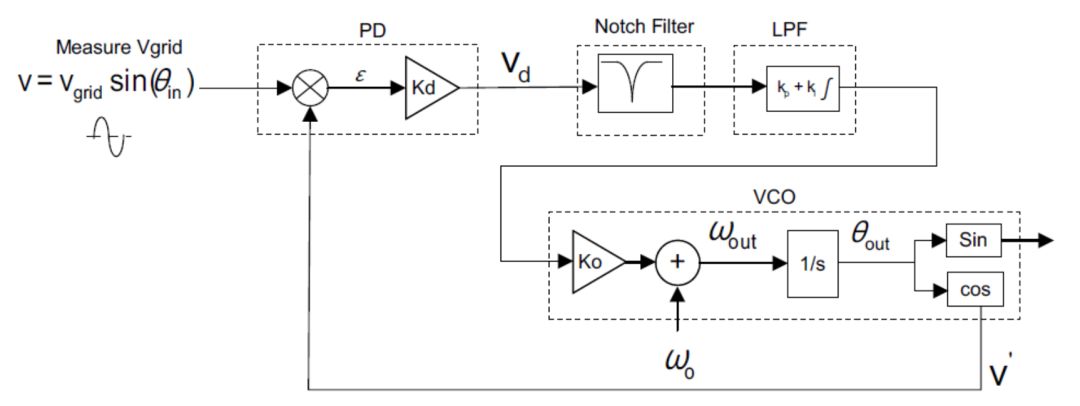

单相锁相环的实现方式有多种,根据鉴相器的不同可以分为两种,如下图所示,图中LPF采用PI补偿器,w0为电网角频率,wout为锁相环输出角频率,θout为锁相环输出相位。

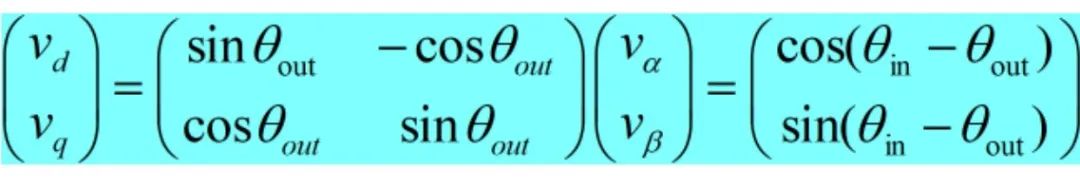

一种是采用坐标变换实现鉴相功能,对一组正交向量(vα与vgrid同相,vβ滞后vgrid 90°)进行Park变换可得:

从上式可以看出,vq的值在一定范围内能反应θin与θout的关系,令vq=0就能够得到与输入相位θin相同的相位θout,等效的线性化框图如下所示。

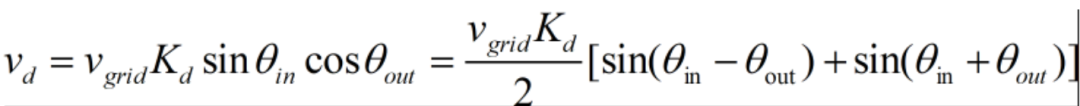

另一种是采用乘法器进行鉴相,其输出如下式,假设输出相位θout能够跟踪θin,那么vd则含有电网二倍频分量,这种低频分量不容易通过LF(一般为PI补偿器)滤除,因此一般需要增加额外陷波器滤除。

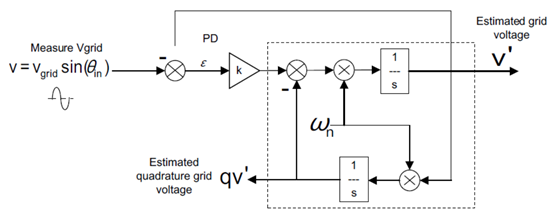

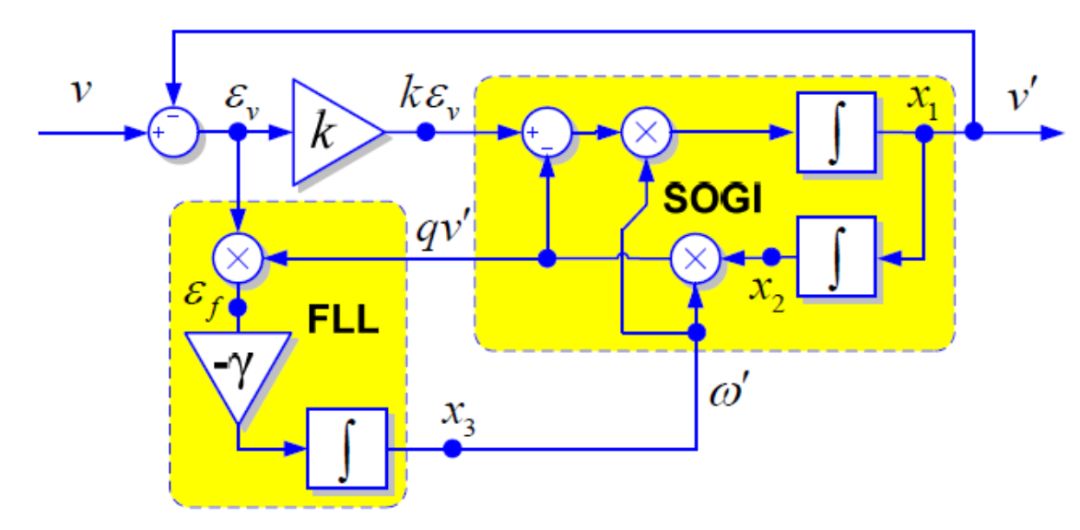

上述第一种方法的关键是如何获得一组正交向量,实现方案有很多种[5],常见的有延迟法、二阶广义积分器(SOGI)等,延迟法很好理解,就是将输入信号延迟1/4周期使之与输入正交;SOGI是利用积分器得到两个正交的信号,如下图所示,

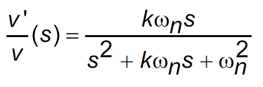

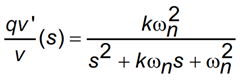

根据上图可以得到v'和qv'对输入v的传递函数,如下所示,

通过其伯德图可以发现,两者相位始终相差90°,因此v'和qv'是一组正交向量。

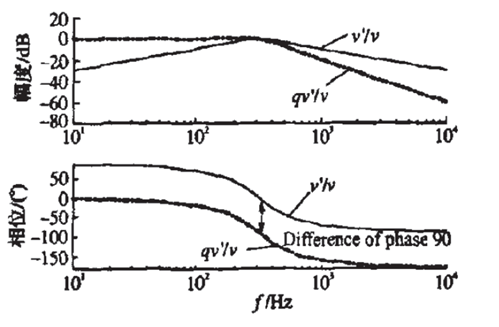

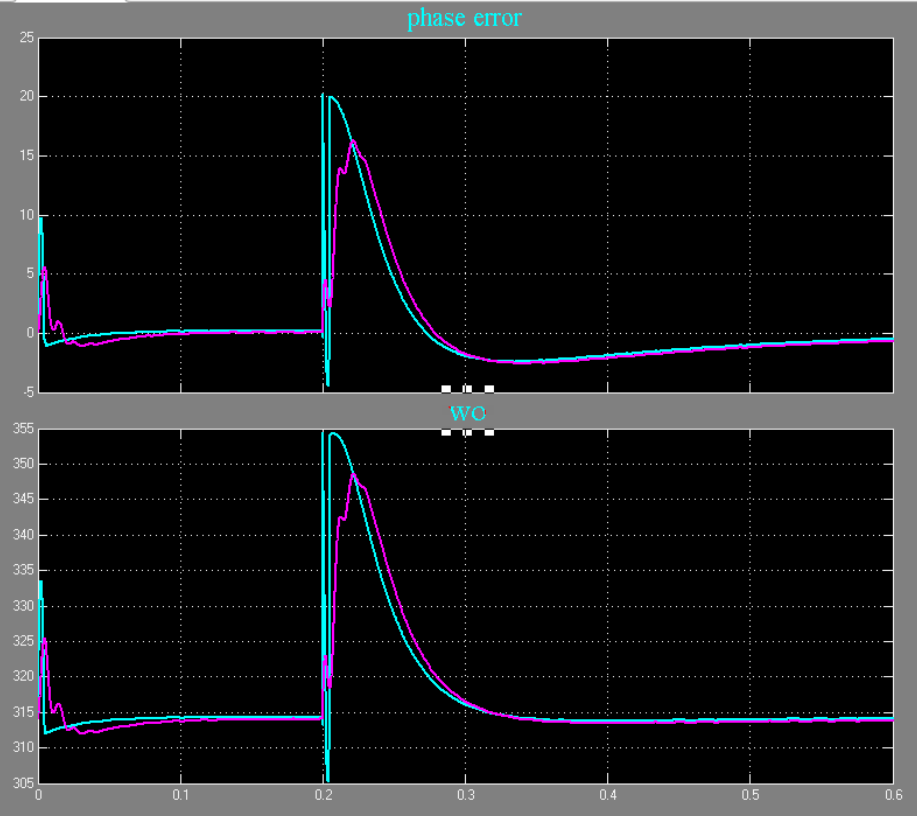

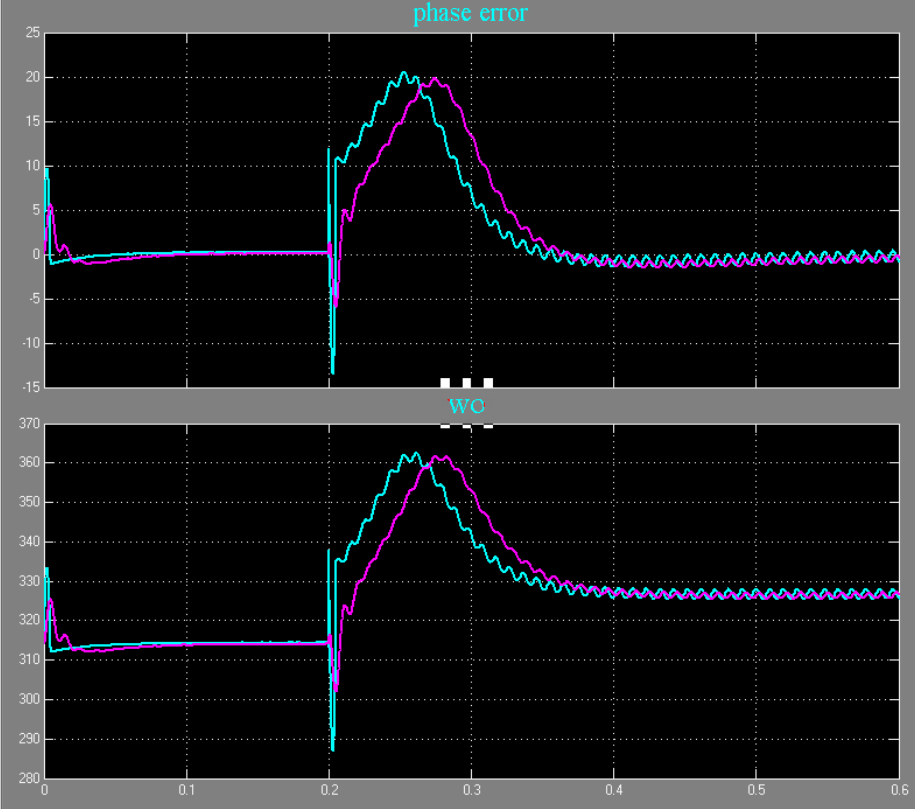

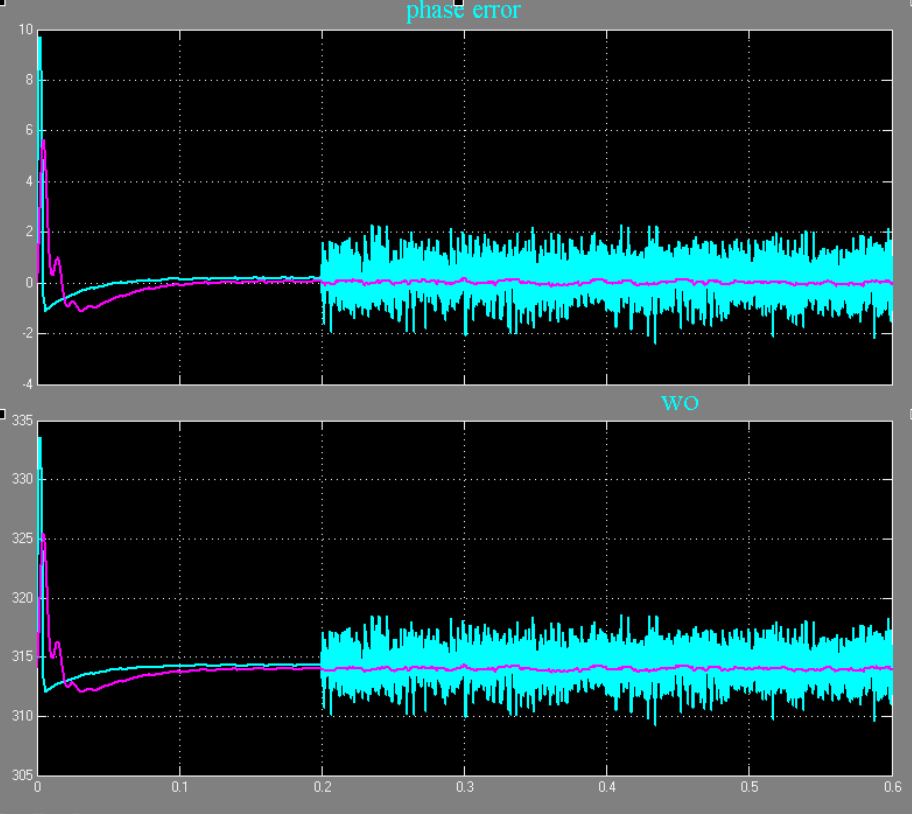

但是两种获得正交向量方式也会影响PLL的性能,仿真可以得到两种方式在电网频率突变、相位突变以及加入噪声时PLL跟踪的相位误差和频率。下图中蓝色代表使用延迟法,紫色代表使用SOGI时的情形。

电网相位突变90°时:

电网频率由50Hz变为52Hz

电网电压中加入白噪声时:

从上面能看出,延迟法和SOGI在电网相位和频率突变时锁相环的效果相差不大(SOGI稍好),但在加入噪声后,延迟法的锁相效果与SOGI相差较明显,主要因为延迟法不具有对输入的滤波能力,SOGI相当于一个震荡环节,具有一定的滤波能力,抗干扰更好。同时在频率突变后,因为正交向量产生环节采用的固定的角频率或延迟时间,所以锁相环的相位误差以及频率发生震荡,去除震荡的方式有多种,可以对信号进行滤波,也可将正交向量产生环节的固定角频率改为PLL输出角频率,也可使用如下的控制框图使SOGI的角频率能够自适应电网频率,这在论文[4]中有详细分析。

参考文献:

1.锁相技术 [张涛 编著] 2015年版

2.Software Phase Locked Loop Design Using C2000™ Microcontrollers for Single Phase Grid Connected Inverter

3.A New Single-Phase PLL Structure Based on Second Order Generalized Integrator

4.grid synchroniczation of power converter using multiple second order generalized integrators

5.Comparative_Performance_Evaluation_of_Orthogonal_Signal_Generators_based_Single_Phase_PLL_Algorithms_A_Survey

6.单相并网逆变器及反孤岛控制研究

后台回复PLL可获得参考文献和simulink仿真文件。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)