MOS 驱动电路中的栅极电阻Rg计算

.

本内容对 MOS 驱动电路中的栅极电阻Rg 进行详细的求解,用于MOS管驱动电路设计全攻略的补充。

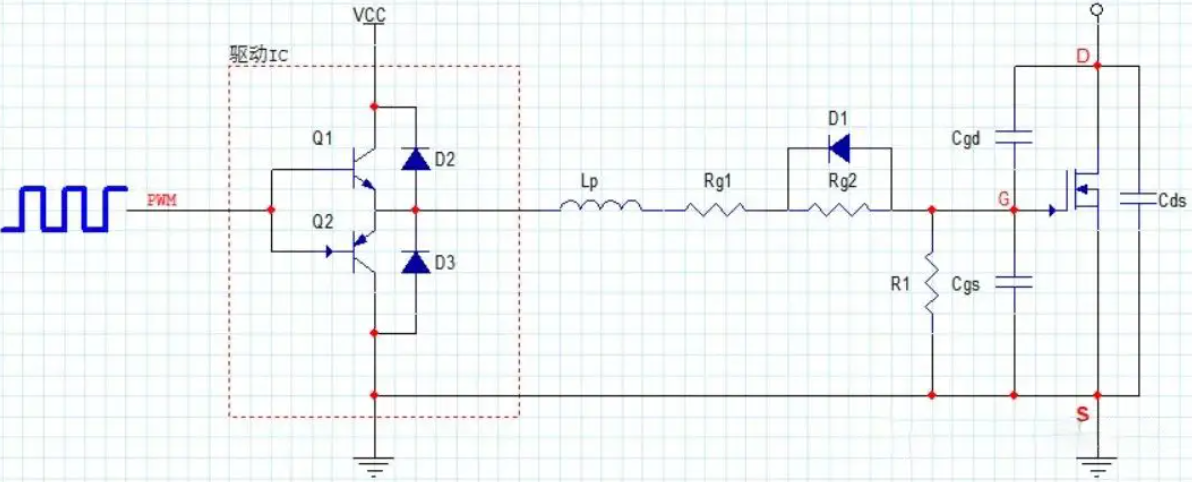

图1 MOS驱动电路

如图1,D1 是驱动电阻Rg2 上并联一个快恢复二极管,使关断时间减小同时减小关断损耗。Rg1 可以限制关断电流,R1 为 MOS管栅源极的下拉电阻,给 MOS管栅极积累的电荷提供泄放回路。

根据 MOSFET 栅极高输入阻抗的特性,一点点静电或者干扰都可能导致 MOS管误导通,所以 R1 也起到降低输入阻抗的作用,一般取值在10k~几十K。

Lp为驱动走线的杂散寄生电感,包括驱动IC引脚、MOS引脚、PCB走线的感抗,精确的数值很难确定,通常取几十nH。

1、驱动电阻Rg的计算

驱动走线的寄生电感和 MOS管的结电容会组成一个 LC 振荡电路,如果驱动芯片的输出端直连到栅极的话,在 PWM 波的上升沿/下降沿会产生很大的振荡,导致 MOS管急剧发热甚至爆炸,一般的解决方法:栅极串联电阻,目的:降低 LC 振荡电路的 Q值,使振荡迅速衰减掉。

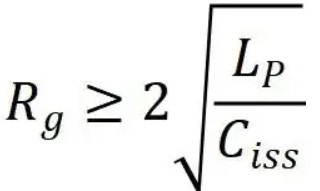

2、驱动电阻下限值

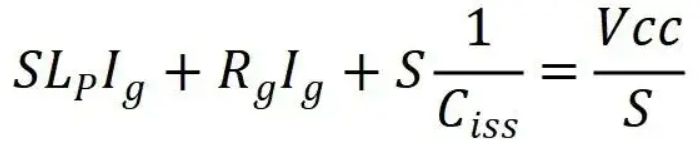

当 MOS 开通瞬间,VCC 通过驱动电阻给 Ciss = Cgs+Cgd 充电,如图1 所示(忽略下拉电阻 R1 的影响)。根据 LC振荡电路模型,可以列出回路在复频域内对应的方程。

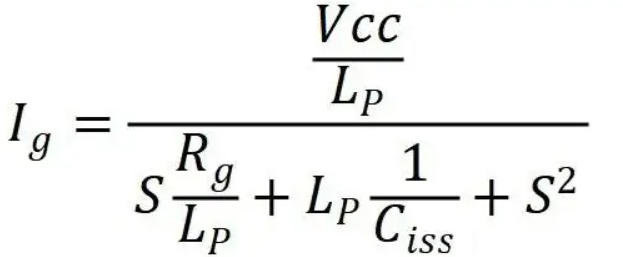

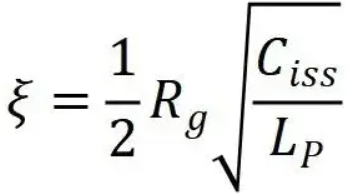

求解出 Ig,并转化为典型二阶系统的形式:

再根据 LC 振荡电路求解二阶系统阻尼系比:

那么根据 LC 振荡电路的特性,为了保证驱动电流Ig 不发生振荡,该系统要处于过阻尼的状态;即阻尼比必须大于1,则方程式解得 Rg = Rg1+Rg2 的下限范围。

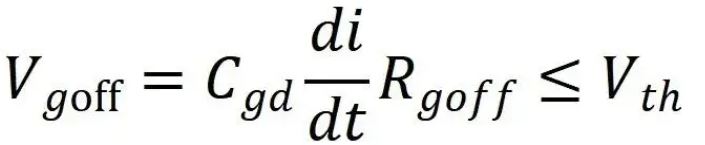

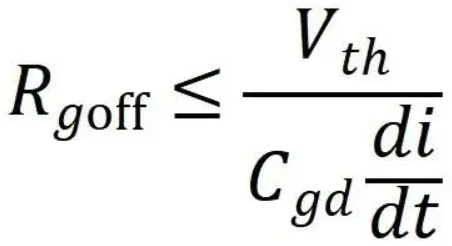

3、驱动关断电阻上限值

MOS 管关断时,Vds 产生的高 dv/dt,会使寄生电容 Cgd 放电形成较大电流(Ic = Cdv/dt)。该电流 Igd 流经驱动电阻 Rg ,在 gs 间产生电压 Vgoff = Igd*Rg。为防止误导通,Vgoff 不能超过 MOS 导通门槛电压 Vth,那么列出不等式:

则解得驱动电阻 Rgoff = Rg1 的取值上限:

实际设计中,先按避免驱动电流振荡算出 Rg(Rg1+Rg2) 下限,再以防关断误导通确定 Rg1 上限。最后结合损耗、电磁干扰(EMI)、桥式拓扑死区控制等因素,通过示波器观测波形调试优化,确定理想的驱动电阻参数。

本内容来自:微碧半导体。如若喜欢这篇文章,不妨留下您宝贵的点赞,这将是对我莫大的鼓励。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)