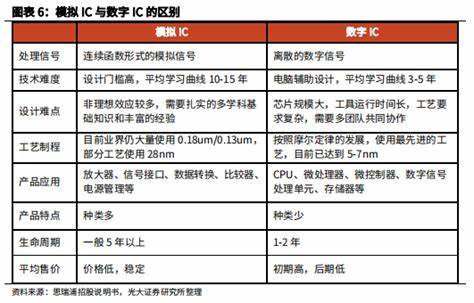

先进芯片封装初级1

英文为 Chip,别称 IC(集成电路:Integrated Circuit 的缩写)。是在半导体晶体片上制造的电子元器件的总称,集成了晶体管、电阻、电容等多种基础器件,形成一个功能完整的电路,可实现复杂计算和控制功能。英文 Integrated Circuit,IC。一种微型电子器件或部件,把一个电路中所需的晶体管、电阻、电容和电感等组件及布线互连一起,制作在一小块或几小块半导体芯片或介质基片上

先进芯片封装初级1

目录

芯片相关

芯片定义

-

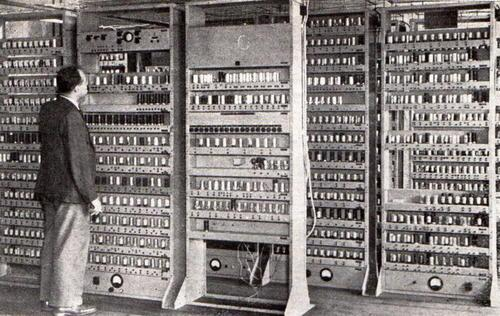

英文为 Chip,别称 IC(集成电路:Integrated Circuit 的缩写)。

-

是在半导体晶体片上制造的电子元器件的总称,集成了晶体管、电阻、电容等多种基础器件,形成一个功能完整的电路,可实现复杂计算和控制功能。

IC 定义

-

英文 Integrated Circuit,IC。

-

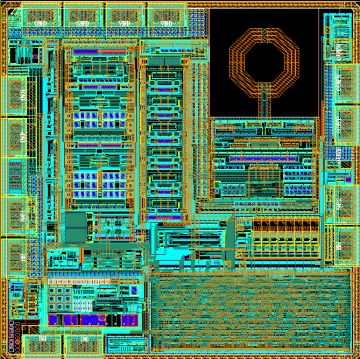

一种微型电子器件或部件,把一个电路中所需的晶体管、电阻、电容和电感等组件及布线互连一起,制作在一小块或几小块半导体芯片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。3

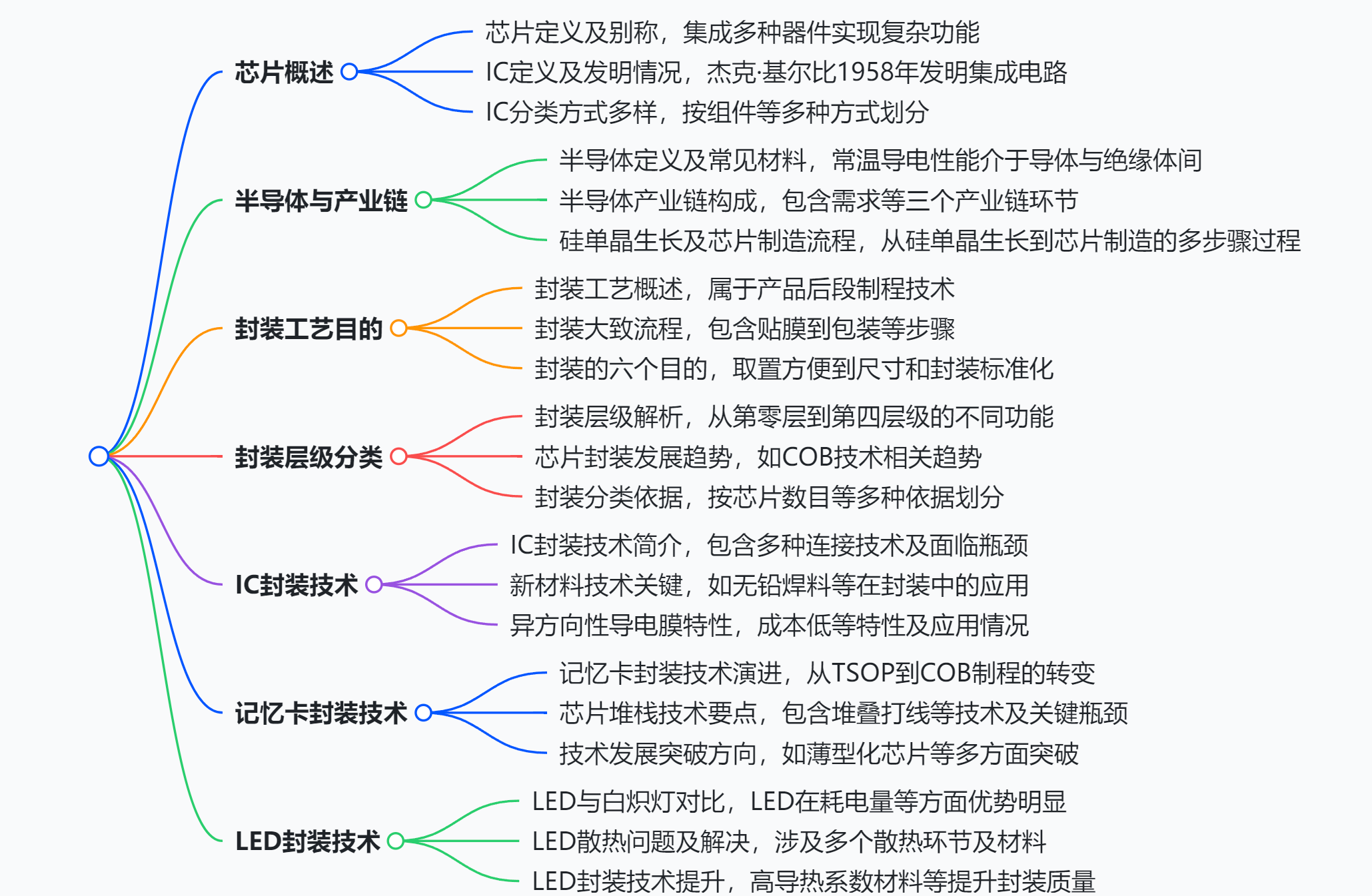

此为ic内部渲染图,包含了所需的晶体管以及电阻电容电感等。

IC 分类

-

按芯片内含组件多少分:小型、中型、大型、超大规模、极大规模。

| 集成电路规模 | 门电路数量范围 | 元器件数范围 |

|---|---|---|

| 小规模集成(SSI)电路 | 10 个以内 | 不超过 100 个 |

| 中规模集成(MSI)电路 | 10 - 100 个 | 100 - 1000 个 |

| 大规模集成(LSI)电路 | 100 个以上 | 1000 - 1 万个 |

| 超大规模集成(VLSI)电路 | 1 万个以上 | 10 万 - 100 万个 |

| 特大规模集成(ULSI)电路 | 10 万个以上 | 100 万 - 1000 万个 |

-

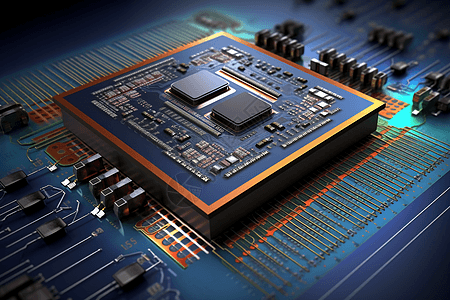

按芯片功能分:模拟、数字。

在这里解释一下数字ic和模拟ic的简单区别:

数字IC:只能处理二进制01,例如电脑中的中央处理器(CPU)、图形处理器(GPU),你输入的数据操作都被转化为二进制,再转化为十六进制机器语言传达给电脑,核心还是处理由机器语言翻译而来的二进制。

模拟IC:模拟IC多用于传感器,电源电路等等。例如Microphone(麦克风)其中就有采集声音的模块,还有温湿度传感器、电压、电流各种传感器,可能通过复杂的电桥电路检测应变片微小参数进行算法计算后得出的测量数值,通常非常考验电路思维,例如气压温度等等都会影响测量。

-

在芯片封装工艺上分:单片、混合。

单片集成电路:所有的电路元件(如晶体管、电阻、电容等)都集成在同一块半导体芯片上,通常是硅片。这些元件通过半导体工艺在芯片内部实现互连,形成一个完整的电路功能单元。例如,一个简单的运算放大器单片集成电路,其内部的晶体管、电阻等元件都是在同一硅片上制作并连接起来的。

混合集成电路:由多个不同类型的元件或芯片组合而成。它可以包含半导体芯片(如数字芯片、模拟芯片)、无源元件(如高精度电阻、电容、电感)以及其他分立元件(如二极管、三极管等)。这些元件通过印刷电路板(PCB)、陶瓷基板或其他介质上的布线进行互连,形成一个具有特定功能的电路。比如,一个混合集成电路电源模块,可能包含一个控制芯片、几个功率晶体管、一些电容和电阻,它们分别安装在陶瓷基板上并通过金属布线连接。

-

在用途上举例有:电视机用、电脑用、通信用。

IC 特点

-

成本低(比离散晶体管低很多)、性能多。

就像A4纸上打印,字大打得少,字小打得多,但是打印一页的价格是差不多的。而且提高集成度的意义并不仅仅是在芯片面积不变的情况下提升电路功能,还可以是实现相同功能用更小的面积。

-

设计难度大、技术要求高、检测多。

设计难度极其复杂,需要eda软件,国产eda主要有:华大九天。+

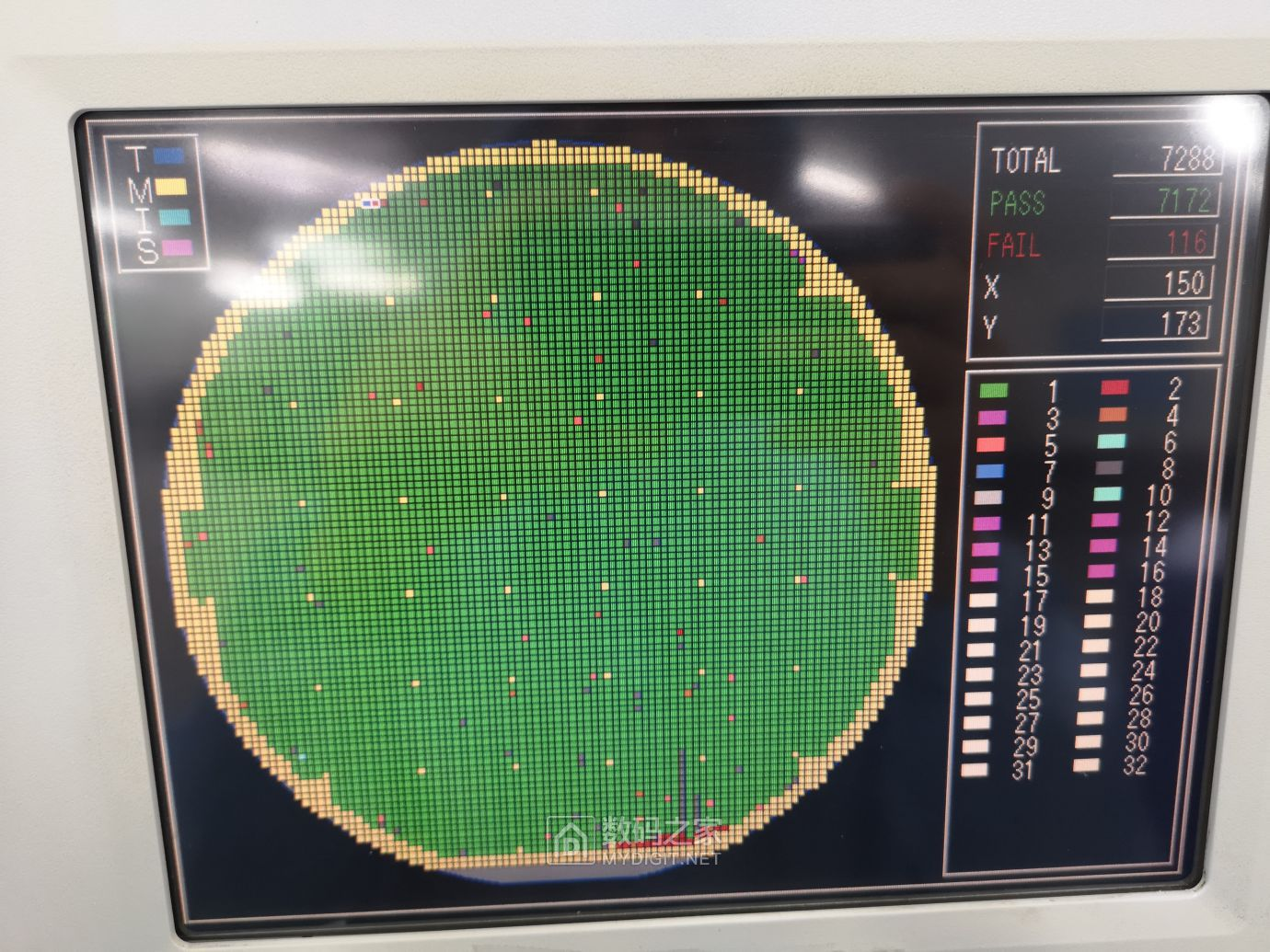

由于其高度集成,所以工艺复杂,在工业生产中,工艺数的增多会带来良率的下降。每一个环节都会有损率。

上图为网络图片,某晶圆某一道工序生产后的map图,其中aoi检测不合格的就会标出,如果工序过多,如何提高良率将是一个重大挑战。

-

稳定性和安全性高。

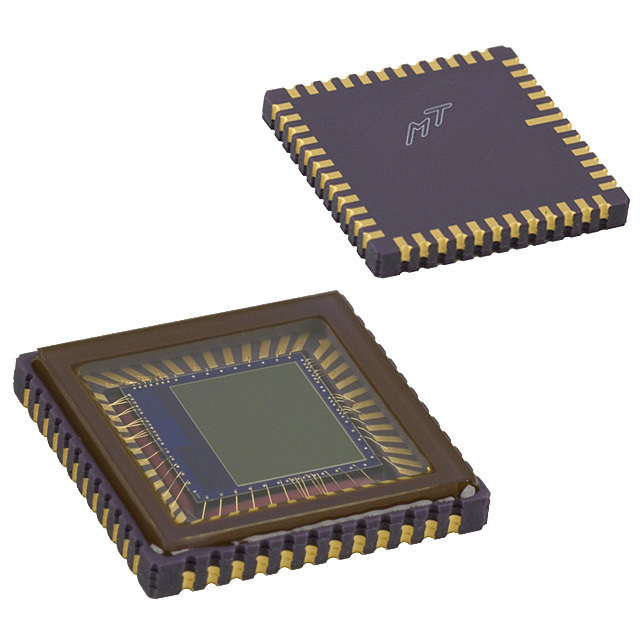

上图为某IC封装,其封装考虑的封装材料的热膨胀系数,以及键合紧密度。晶圆本身是及其脆弱的,但是经过封装后就具有一定的抗腐蚀 抗氧化 抗老化性质,产品出货也会有强酸模拟长时间老化的老化性测试,所以经过封装的IC具有较好的稳定性安全性。

半导体与半导体产业链

半导体定义

-

英文 semiconductor,常温下导电性能介于导体与绝缘体之间的材料。常见材料有硅、锗、砷化镓等,硅在商业应用上最具影响力。

半导体产业链

-

从沙子到 IC / 芯片流程:氧化、化学沉积、加工处理、光刻、蚀刻等操作、切割。

-

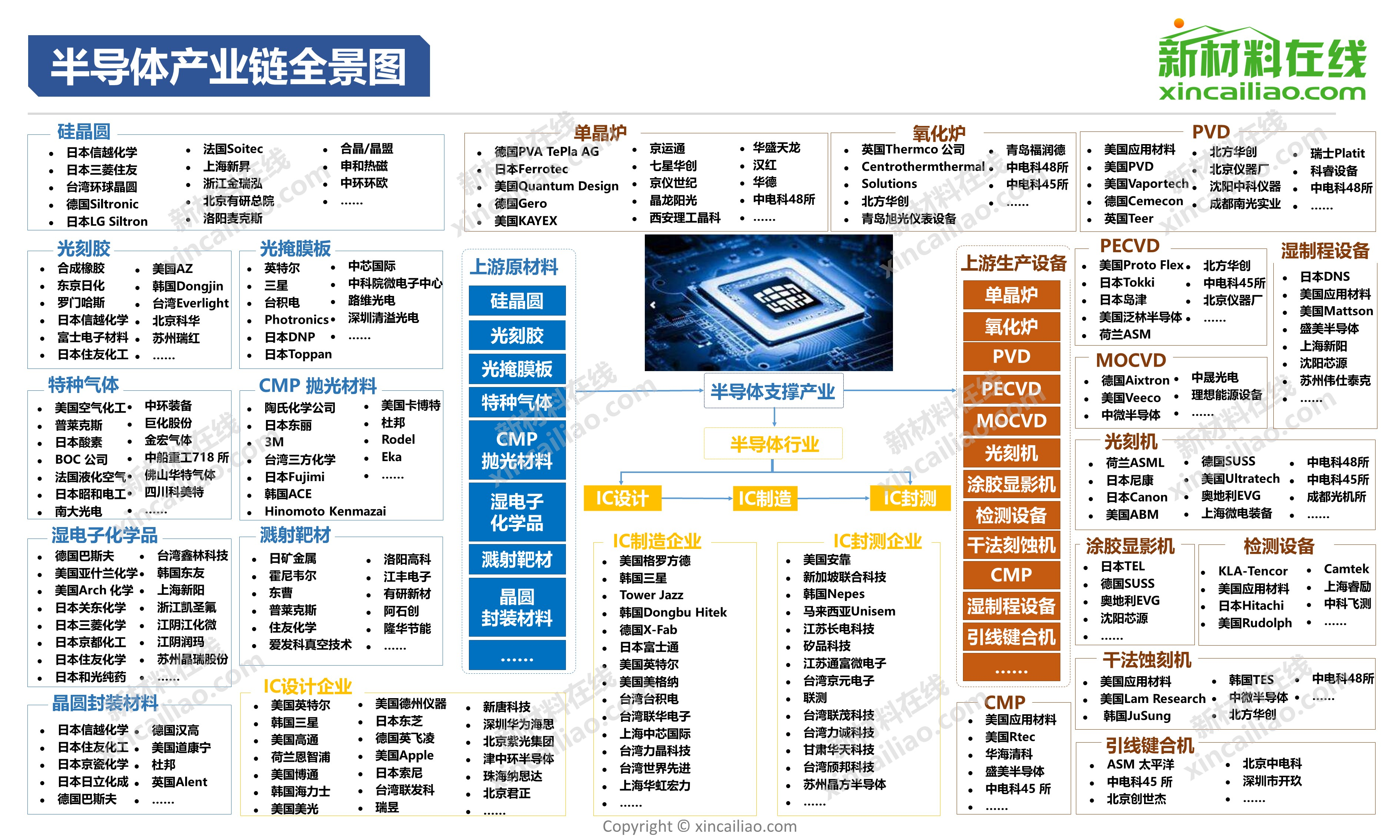

全球半导体产业链:需求产业链(下游应用)、核心产业链(中游制造)、支撑产业链(上游支撑)。包括硅单晶生长、芯片制造、封装测试等环节,涉及众多企业和设备需求。

.

封装工艺与目的

封装工艺

-

属于产品后段的制程技术,常被认为是集成电路制程技术的配角之一,但重要性不亚于 IC 制程技术与其他微电子相关制程技术。

-

大致流程包括贴膜、贴片、焊线、模封、成型、成测、包装。

封装目的

-

取置方便:晶圆切割后所得晶粒毫米级,取置不方便,封装后便于操作。

-

保护芯片免受物理损害和环境影响:防止机械外力冲击、灰尘、湿气、静电等对芯片造成短路、漏电、电蚀、极性反转等损害。

-

提供机械支撑:减轻振动、温度变化和外部力量等因素引起的应力,降低芯片断裂或损坏风险。

-

引脚连接和电气连接:提供外部引脚,方便芯片与其他电子组件进行物理连接和电气连接,实现通信和数据传输。

-

散热和温度管理:通过热传导、散热设计、空气流动、散热组件等方式管理芯片发热。

-

尺寸和封装标准化:使不同芯片可采用相同或相似外部尺寸和标准接口,方便集成到各种电子设备和系统,提高互换性和可扩展性。

封装的层级与分类

封装层级

-

第零层:IC 设计,包括物理布局布线版图物理验证(功能和时序验证)、电路设计、逻辑设计、图形设计等。

-

第 1 层次:第一层级封装(单芯片或多芯片模块),将 IC 芯片黏结于封装壳体中,完成电路连线与密封保护。

-

第 2 层次:第二层级封装(印刷电路板 PCB),将第一层级封装完成的组件组合于一电路卡(Card)上。

-

第 3 层次:第三层级封装(母板),将数个电路板组合于一主机板(Board)上成为一次系统。

-

第 4 层次:第四层级封装(电子产品),将数个层级系统组合成为一完整的电子产品。

封装发展趋势

-

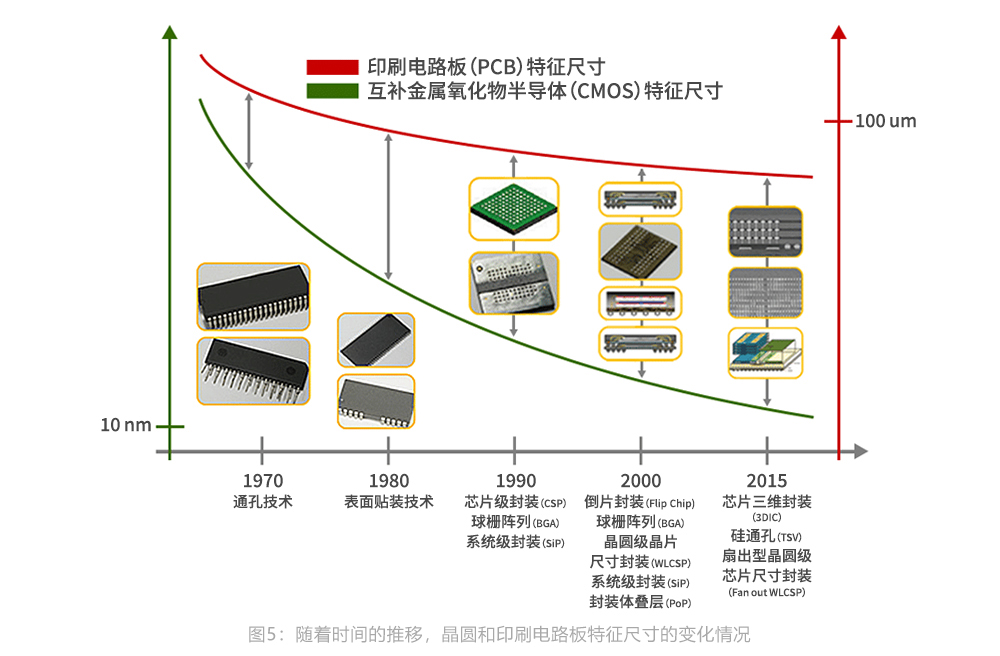

芯片直接组装于电路板(COB)技术的发展趋势,相关技术有打线键合(Wire Bonding)、卷带式自动接合(Tape Automated Bonding,TAB)、覆晶接合(Flip Chip)等。

封装分类依据

-

依照 IC 组件中的芯片数目分:单芯片封装、多芯片封装。

-

依照封装材料来分:陶瓷封装外壳(如陶瓷双列直插 Ceramic Dual In-line Package,CDIP)、塑胶封装外壳(如塑料双列直插 Plastic Dual In-line Package,PDIP)、BGA(Ball Grid Array)等。

-

依照引脚分布型态分:单边引脚、双边引脚、四边引脚、底部引脚。

-

依照与电路板的接合方式分:表面贴装封装(Surface Mount Package)、插装封装(Through-Hole Package)、混合封装(Hybrid Package)、格式阵列封装 PGA(Pin Grid Array)。

IC 封装技术简介与发展

IC 封装技术内容

-

包含芯片黏结(Die Mount)、联线技术(Interconnection)、导线架(Lead Frame)、陶瓷封装、封胶(Molding)、塑胶封装、印刷电路板(Printed Circuit Board PCB)、焊锡球 / 焊锡凸块(Solder Ball/ Solder Bump)等。

-

单芯片构装连接技术如金焊线连结卷带式芯片封装、球栅面阵列及覆晶阵列封装等,还有多芯片模块、3D 立体构装技术及晶圆级芯片封装。

面临瓶颈与发展关键

-

国内半导体构装业者面临产品、技术升级与转型瓶颈,特别是在高频宽带与光电产 PC 与通讯产业市场趋向饱和及成长衰退相关技术方面。

-

未来发展关键在于新材料技术的掌控搭配环境永续发展与绿色环保意识,如在芯片连接、载板制作、讯号传输、芯片整合等方面需要新材料突破,同时要解决绿色制程材料无铅化等课题。例如,一些超细间距的温敏应用开始使用纯铟或者镀铟 / 银的凸块。无卤素定义为均质材料中氯溴化合物含量低于 900ppm 且氧化锑含量低于 900ppm,无铅定义为均质材料含铅量低于 1000ppm。

异方向性导电膜(ACF)

-

具有成本低、耐疲劳破坏、可靠度高及材料可再生利用的特性。主要由在胶材料中均匀分布一定量导电粒子组成,本身不导电,通过制程控制使胶呈熔胶状态让导电粒子均匀分布。在连接至液晶显示器之外引脚接合(Outer Lead Bonding OLB)、内引脚接合(Inner Lead Bonding,LB)或驱动芯片(Driver IC)的制程等应用上大量采用。可连续加工,提供机械强度保障,减少组件间热应力或断裂面产生,能满足微小间距封装。

记忆卡封装技术简介与发展

封装技术演进

-

初期以 TSOP(Thin Small Outline Package)的封装形式搭配 SMT 的制程为主,外观组装以射出成型塑胶外壳利用超音波压合而成。近年随着产品轻薄短小需求与制程技术提升,封装技术应用导向以 COB 制程搭配芯片堆栈为主。

芯片堆栈技术

-

芯片会直接贴附在裸露的电路板上,使用导电粘合剂固定。利用先进制程技术直接将晶圆进行堆栈后封装,如台积电的 CoWoS 封装过程。包括堆叠打线技术,涉及封装胶、焊料凸块、外球、封装基板、芯片微凸点、填充料、FC 焊点、基根等。完成记忆卡容量提升需从前段制程开始将芯片磨薄,然后进行多层芯片堆叠固晶打线,同时涉及金属布线层、重布线层、Si 中介层等。

技术发展突破

-

薄型化芯片朝向 50um 以下厚度规格迈进,弧高技术朝向 35um 以下瓶颈突破,固晶接合材料上导入 DAF(Die Attach Film)、FOW(Film・WIRE)等特殊接合材料,在 1mm 厚度可完成 2 - 8 层芯片堆叠量产并向 9 层以上结构发展。三次元封装(3D package)技术发展,采用导通孔贯穿技术(Through Silicon Via,TSV)取代打线制程,使内部连接路径更短、芯片间传输速度更快、效能更佳。

LED 封装技术简介与发展

LED 与白炽灯对比

-

LED 灯在耗电量与二氧化碳排放量上可大幅减少 85% 以上,光效率转换高,不含水银,不会放出红外线与紫外光等。传统白炽灯光效率转换偏低(仅 10% 可转换成光源),会导致过多二氧化碳排放,红外线会使室内温度升高,紫外光会让被照射物体产生裂化且易吸引昆虫聚集。

LED 散热问题及解决

-

LED 灯需要解决芯片结到外延层、外延层到封装基板、封装基板到外部冷却装置等环节的散热问题,热传导信道任何环节出现问题都会导致 LED 结温过高,引发灯光衰现象直至产品提早报废。散热材料包括导热硅脂、导热双面胶、导热硅胶片、导热绝缘片等。采用高导热系数材料陶瓷基板,COB 封装技术搭配 DB 时的 Eutetic bonding(共晶键合),WLP 晶圆级封装技术提供最佳散热途径与高可靠度质量。

LED 封装技术提升

-

封装材料上以提升荧光粉的光能量转换效率、涂布技术与高耐热、高效能、低吸湿性透明胶材的开发为主。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)