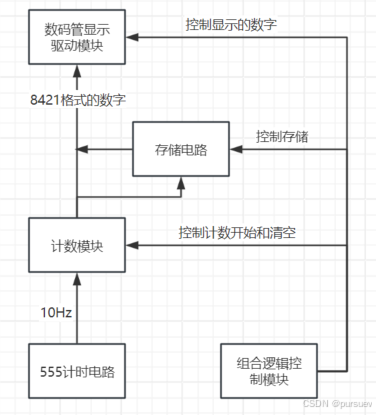

数字秒表电路设计(74系列芯片逻辑电路,Multisim仿真,可存储)

本项目来源于作者的数字电路课程设计:可实现计时,锁存(一组数据),解锁,清零功能设计要求及指标:最大记时长度99.9秒的秒表。时间分辨率0.1秒。两个按键, 一个用于复位,另外一个用于启停。复位按键仅在停止计时时有效,如果是在计时状态按下复位,则实际上是锁存当前计时,如果再按复位,则解除锁定。如果在锁存状态下按启停按钮,则实际停止计时,用3位数码管显示计时仿真软件:Multisim。

通过百度网盘分享的文件:数字秒表设计_Multisim原件&74系列芯片手册.zip

链接:https://pan.baidu.com/s/1jGjgDj3S1Yzd7GorkSHFcQ?pwd=0000

提取码:0000

本项目来源于作者的数字电路课程设计:可实现计时,锁存(一组数据),解锁,清零功能

设计要求及指标: 最大记时长度99.9秒的秒表。时间分辨率0.1秒。

仿真软件:Multisim

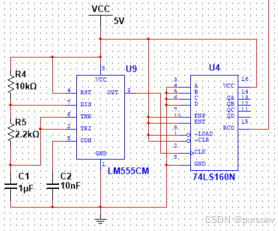

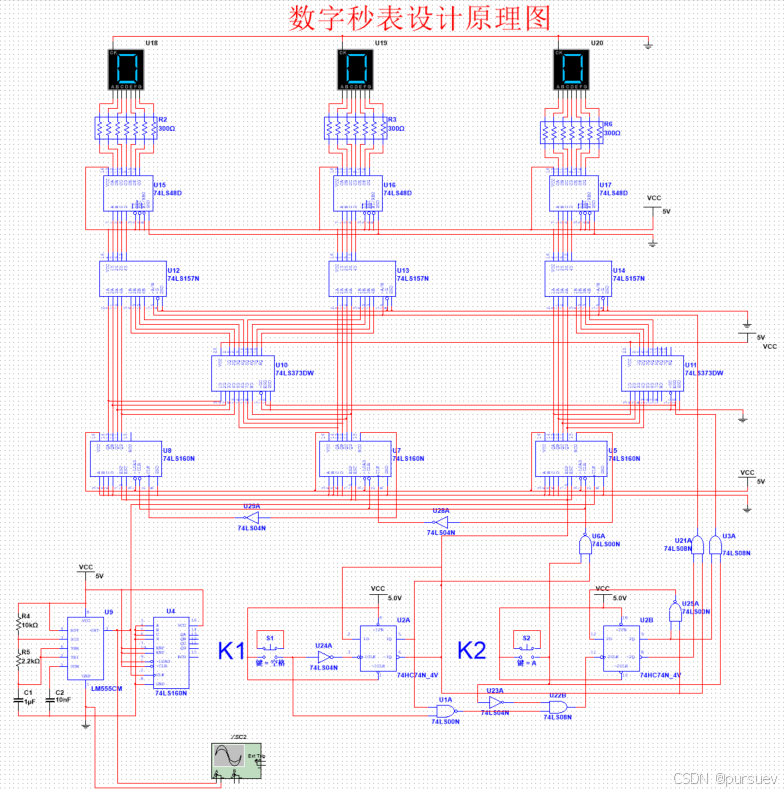

555电路:NE555,74ls160

计数模块:74ls160

锁存模块:74ls373

数选模块:74ls157

译码模块:74ls48,电阻

组合逻辑模块:74ls00,74ls04,74ls08,74hc74,按键开关

1.设计基本原理及分析

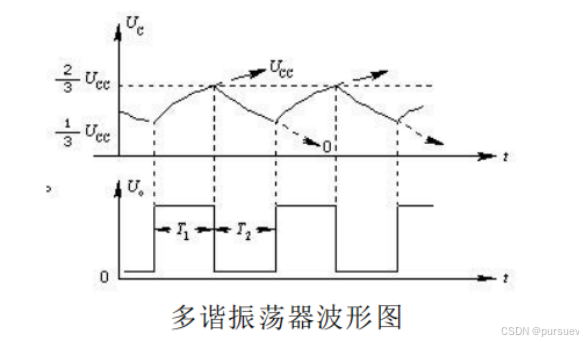

(1)555震荡电路设计

芯片:LM555CM ,74ls160

555组成多谐振荡器的工作原理如下:

接通电源 Vcc 后,Vcc 经电阻 R1和 R2对电容 C 充电,其电压 UC 由0按指数规律上升。当 UC≥2/3VCC 时,电压比较器 C1和 C2的输出分别为UC1=0、UC2=1,基本 RS 触发器被置0,Q=0、Q’=1,输出 U0跃到低点平 UoL。

与此同时,放电管 V 导通,电容 C 经电阻 R2和放电管 V 放电,电路进入暂稳态。随着电容 C 放电,Uc 下降到 Uc≤1/3Vcc 时,则电压比较器 C1和 C2的输出为 Uc1=1、Uc2=0,基本 RS 触发器被置1,Q=1,Q’=0,输出 U0 由低点平 UoL 跃到高电平 UoH。同时,因 Q’=0,放电管 V 截止,电源 Vcc 又经过电阻 R1和 R2对电容 C 充电。电路又返回前一个暂稳态。因此,电容 C上的电压 Uc 将在2/3Vcc 和1/3Vcc 之间来回充电和放电,从而使电路产生了振荡,输出矩形脉冲。

振荡频率:

因为需要10Hz信号,还需通过74ls160进行10分频。(也可以直接改变1uF电容的值,不用10分频,产生10Hz信号。)

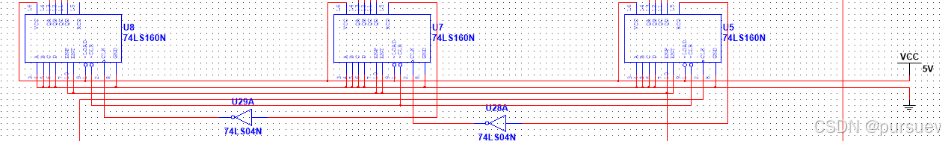

(2)计数电路设计

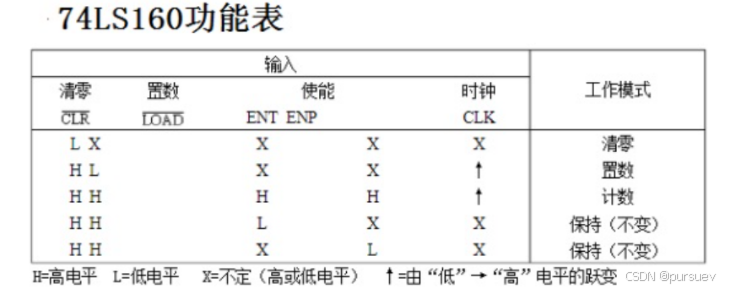

芯片:74ls160

因为实验中的计数需求是逢十进一,而且需要输出高电平来驱动共阴极数码管,因此采用74LS160作为计时芯片。74LS160是常用的数字逻辑芯片,为十进制计数器,具有计数、置数、禁止、清零等功能,其内部是由 D 触发器和逻辑门电路构成的。

为了实现三个逢十进一的进位,我们将三个74ls160计数芯片进行级联,将上一级的进位端连到下一位的时钟端作为计数信号,同时为了保证时序上的一致性,在中间连接一个非门,利用进位信号的下降沿作为时钟计数信号的上升沿,保证了上一级计数由9到0的时候下一级再计数加一,而不是在计数到9,下一级立马计数加一,以免会出现8的下一个状态有短暂的19而不是9的这种错误的状况。

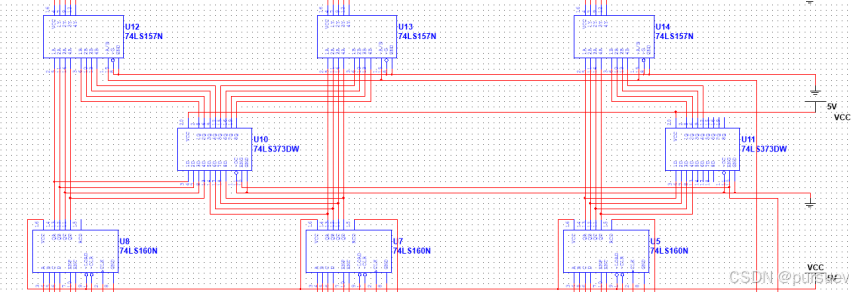

(3)锁存电路以及显示控制电路设计

锁存芯片:74ls373 数选芯片:74ls157

锁存电路采用74ls373 (D锁存器)来存储锁存操作记录下的时间,74LS373是一种8位锁存器,采用三态输出,具有输入数据存储、输出数据驱动、数据总线隔离等多种功能。此外根据要求,数码管显示的时间有两种状态,显示计时时间/显示锁存时间,需要对两种时间进行选择,74ls157数选芯片可以实现四路并行数据的2选1,通过选择输入端和选通输入端控制输出的信号。

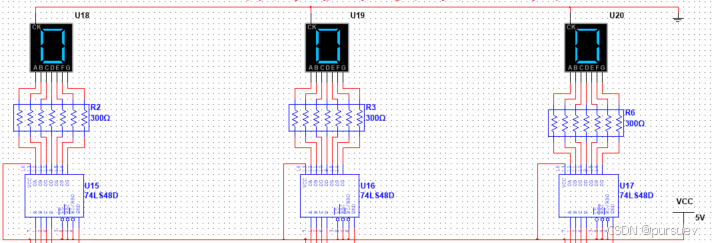

(4)数码管显示驱动设计(译码电路)

芯片:74ls48

"74LS48 芯片是一种常用的七段数码管译码器驱动器,被广泛应用于各种数字 电 路 和 单 片 机 系 统 的 显 示 系 统 中 。 在 设 计 中 , 该 芯 片 用 于 驱 动SEVEN_SEG_COM_K 数码管。该芯片的主要功能是对输入信号进行译码,并控制相应的输出,以实现七段数码管的显示效果。输出端口最好在接入数码管的对应端口之前串联一个电阻,保证数码管不会烧掉。

74LS48 芯片是一款特殊的译码器,其输出在高电平有效。除了基本的输入(DCBA)和输出(Ya~Yg)端之外,74LS48 还引入了灯测试输入端(LT)和动态灭零输入端(RBI),以及具有输入和输出双重功能的消隐输入/动态灭零输出端(BI/RBO)。

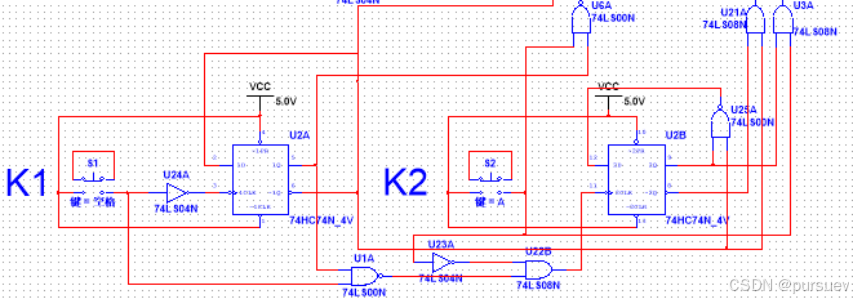

(5)组合逻辑控制模块设计

要完成数字秒表电路的控制部分首先要搞清需要实现的功能,用到的芯片的控制端的逻辑,以及状态转移的变化。

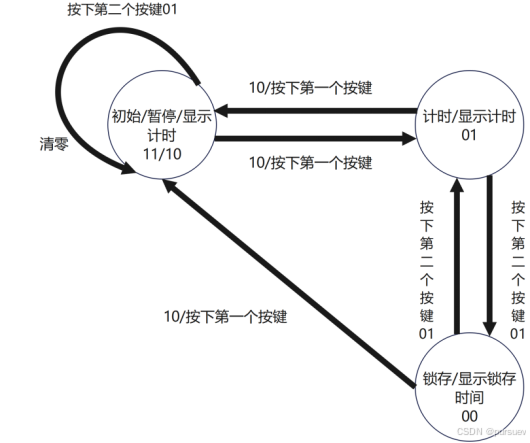

首先根据要求,此电路需要两个按键,一个用于复位(K2),一个用于启停(K1),复位按键仅在停止计时时有效,如果是在计时状态按下复位,则实际上是锁定当前计时,并显示锁定的时间,但是计时器还在继续工作,如果再按复位,则解除锁定,并显示计数器的时间,如果在锁定状态下按启停按钮,则实际停止计时,再按复位键后清零,并回到初始状态。经过多次实际的仿真迭代,决定采用如下所示的状态转移图。并根据状态转移图列出了状态转移表。

|

状态 |

Q1 |

Q2 |

输入 |

Q1’ |

Q2’ |

功能 |

显示 |

|

初始/暂停 |

1 |

X |

K1 |

0 |

1 |

启动 |

计数 |

|

初始/暂停 |

1 |

X |

K2 |

1 |

1 |

清零 |

计数 |

|

计时 |

0 |

1 |

K1 |

1 |

1 |

暂停 |

计数 |

|

计时 |

0 |

1 |

K2 |

0 |

0 |

锁存 |

锁存 |

|

锁存 |

0 |

0 |

K1 |

1 |

0 |

暂停 |

计数 |

|

锁存 |

0 |

0 |

K2 |

0 |

1 |

解锁 |

计数 |

为满足实际生活中秒表的操作,我们运用 D 触发器和 PB_DPST 开关设计出通过按钮式的开关,实现通过按压一次按钮实现功能切换的模式。

D 触发器只有一个数据输入“D”和一个时钟脉冲输入,带有两个输出 Q 和 Qbar。这种触发器也称为延迟触发器,因为当输入数据提供给 d 触发器时,输出跟随输入数据延迟一个时钟脉冲。D 触发器是一种双稳态存储器元件,一次可以存储一位,“1”或“0”。

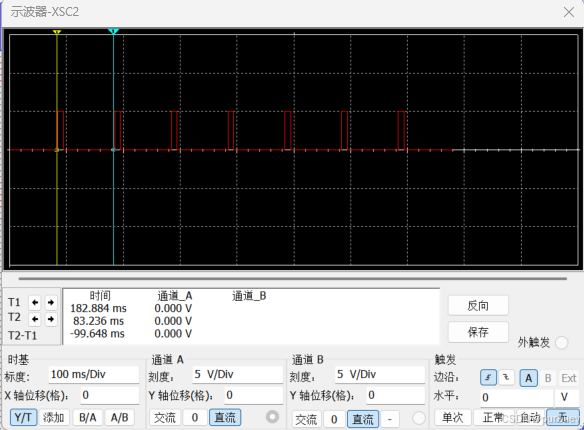

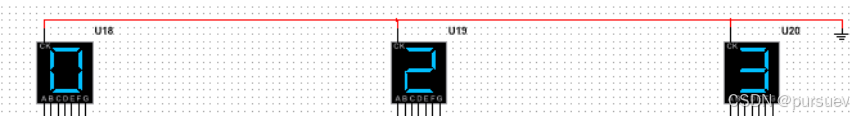

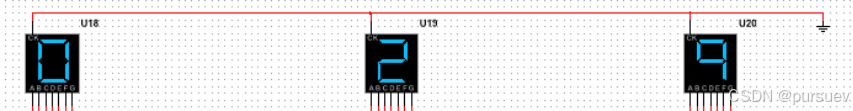

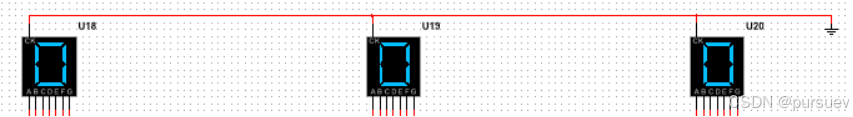

2.Multisim仿真

Multisim仿真原件在文章开头,下面是电路仿真图

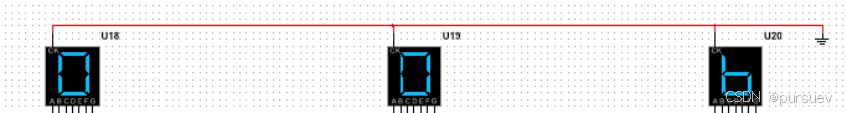

1.启动(按下K1)

2.锁存并显示锁存时间(按下K2)

3.暂停计时并显示计时时间

4.清零

3.板级验证后的改进

实际的电路搭建时,在两个开关的输出端都要接下拉电阻,因为如果不接下拉电阻,开关未按下时处于高阻态,不能作为逻辑0来驱动非门输出高电平,导致状态转移和仿真过程中的结果发生偏差。

七段共阴极数码管的每一个输入端都要接电阻来限流,防止电流过大烧掉数码管里的LED灯。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)