一文弄清芯片IC前端设计layout版图布置设计--NMOS 与 PMOS 结构及制作工艺全解析(2/3)

nmos 和 pmos 制作工艺全解析

各位爱好的电子的朋友对电路图应该不陌生, 会用到各种芯片的封装,然后放在相应的位置实现电路功能

那你有没有想过这个芯片里面是什么样子的呢

芯片是怎么设计出来的啊, 用什么EDA工具啊 ,为什么要这样设计的呢

为了讲清楚这个问题,我们先要了解下大概的芯片制作流程哈

详细可参考视频: 半导体EDA布局工具Virtuoso,从CMOS晶圆到电路仿真,全流程设计CMOS inverter_哔哩哔哩_bilibili

首先回答第一个问题啊, 这里有以mosfet结构来举例

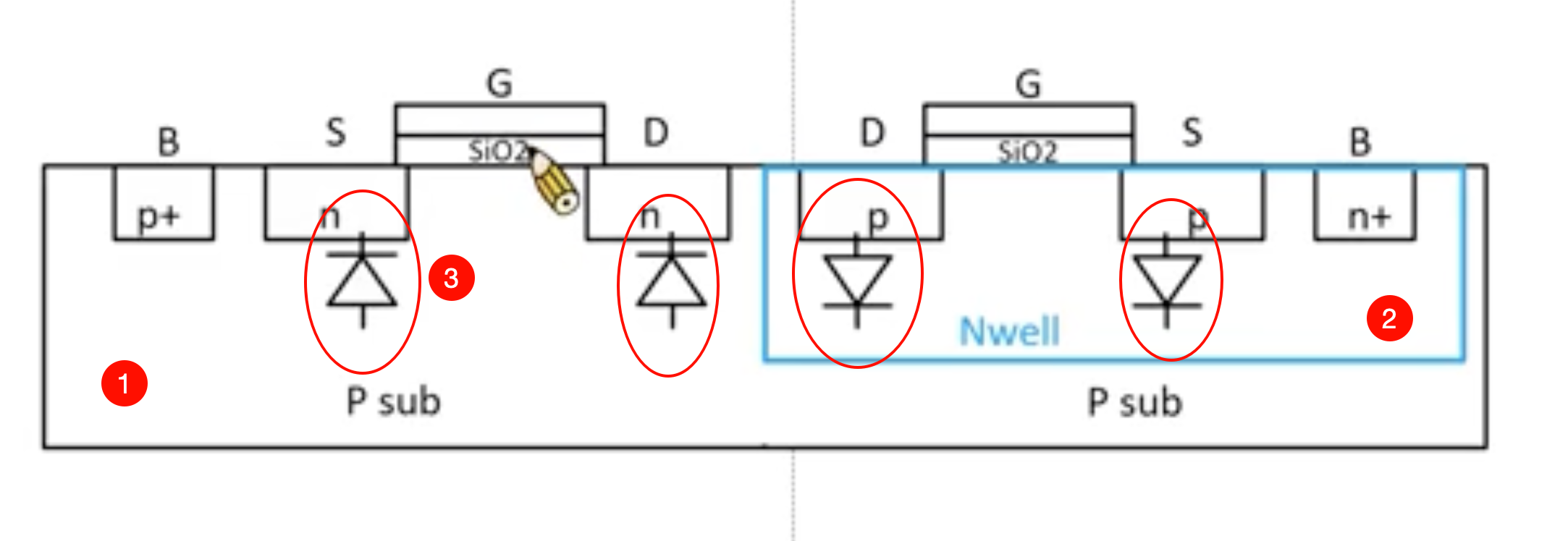

我们来看看, NMOS 和PMOS的结构,

通过这张图我们可以发现

1 不管是NMOS还是PMOS都基底都是建立在Pwell上面哈,类似于建筑立面都用一种地基去建造的, 如果是Nmos就可以直接建造了

而如果是PMOS ,我们就要打二次基底了, 如2所示 .因为PMOS的衬底都是N型半导体啊

第二点,我们发现3处是不是有好多二极管啊, 这时天然属性,有PN结的地方就有半导体啊 , 为了不让这个半导体导通或者说反偏 ,

我们有2中方法啊 ,

第一种就是让正极也就是P最大电压为0 ,这样结构上没有比0更低的电压了吧, 他就没机会正篇了是吧, 也就是左边的NMOS的b衬底接地

第二正我负极接最高电压,也就是N的最小电压为VDD供电电压,这样结构上没

有比此处更高的电压了是吧,这样肯定不会导通, 也就是右边的PMOS的B衬底接VDD电源了

关于为什么衬底要接对应的电压,

可参考文章 https://zhuanlan.zhihu.com/p/24186520658

大家在画电路图的时候, 肯定都没有b极这个选项, 因为芯片厂商都帮你连接好了,

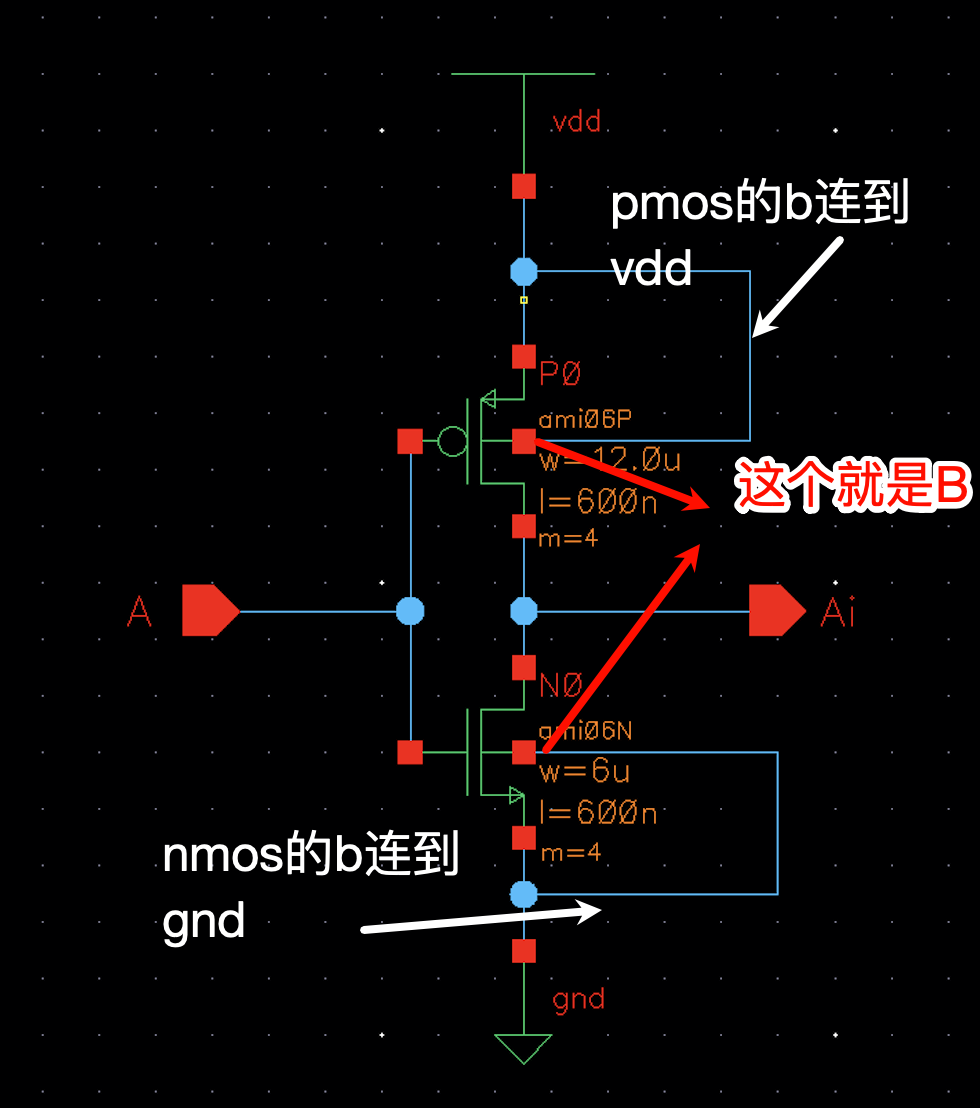

我给大家看看芯片设计的时候NMOS和PMOS的B极是如何连接的

是不是和我们说的一样啊

PMOS的b 连接到vdd。 NMOS连接到gnd啊

好,接下来我们来看看第一张的图在实际的工艺生产的时候是怎么做出来的啊

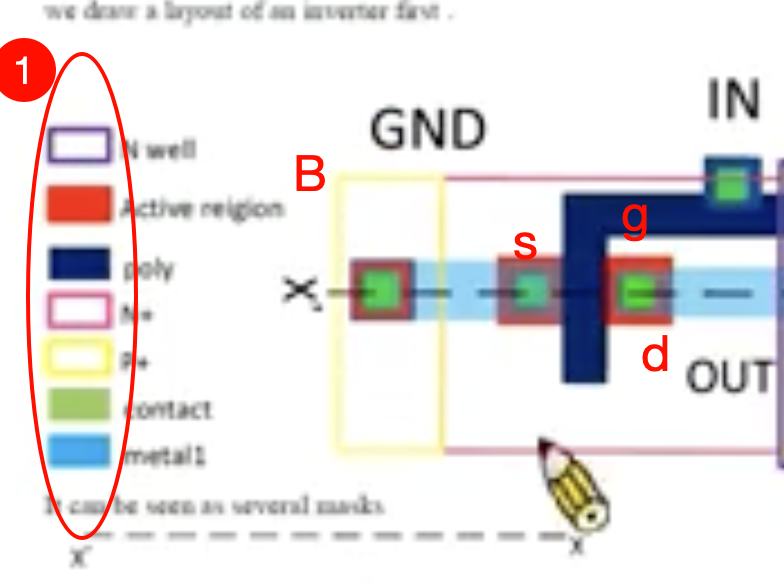

上面是一个layout

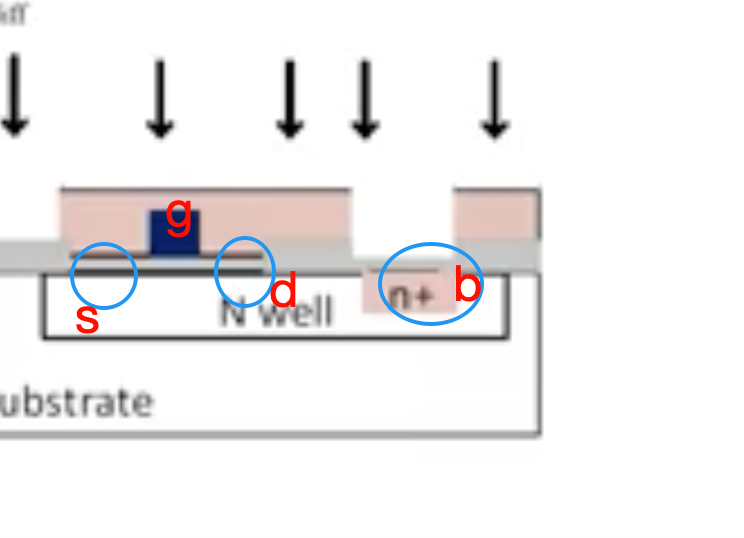

我们看到一个MOSFET的四个极 GDSB

同时我们看下圈子里面的图标意思

Nwell 就是N型材料

Active region就是实际做出来的时候的有效区域

Poly多晶硅,就是专门用来做gate栅极的,有时候也可以直接当做导体用

N+是n离子注入区, 比方说我们active区域都是先进行N+离子注入,再形成active区域

P+是p离子注入区

Contact 就是接触点, 有限面积内越多越好,减小电阻

Metal1 就是金属层1, 因为半导体有很多层,这里是第一层,有可能看到metal2,3,4之类的

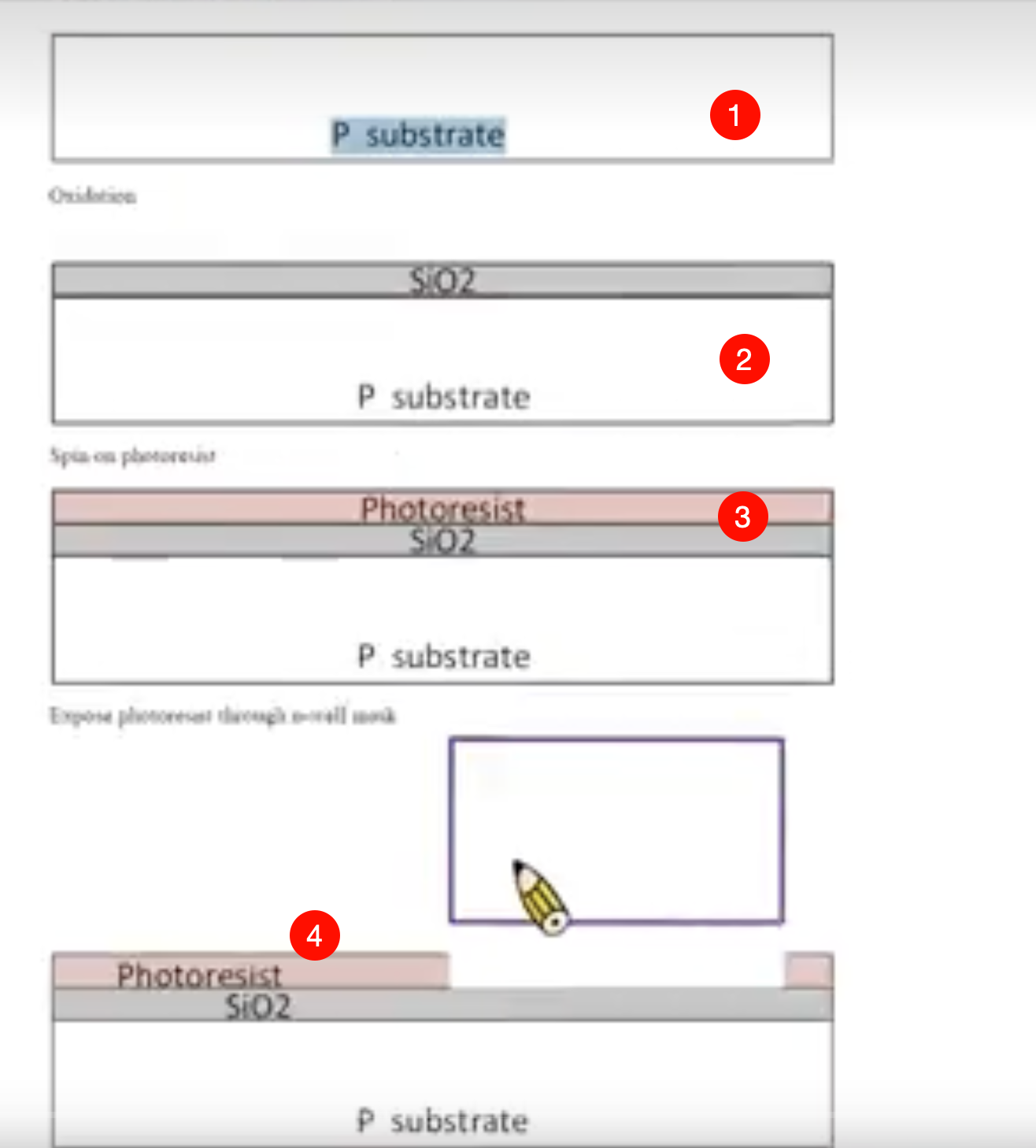

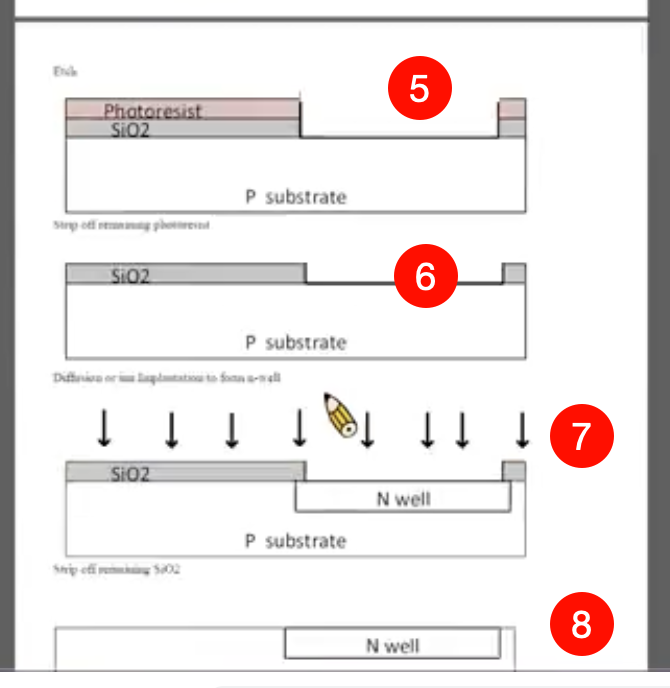

要做上面的实际模型 ,我们看生产的时候怎么弄(下面以P型mos举例哈

,上面那张图是NMOS的)

第一:有个p型衬底是吧

第二:我们再上面注入sio2二氧化硅

第三:屠夫光阻剂)

第四:用一个N+的mask罩子阻挡要蚀刻的区域(这里是负片效应,挡的地方会适合,不挡就留下, 有的地方也用正片设计,挡的地方留下, 不挡的地方时刻掉)

第五:把sio2二氧化硅蚀刻掉

第六:清洁之类的

第七:离子注入

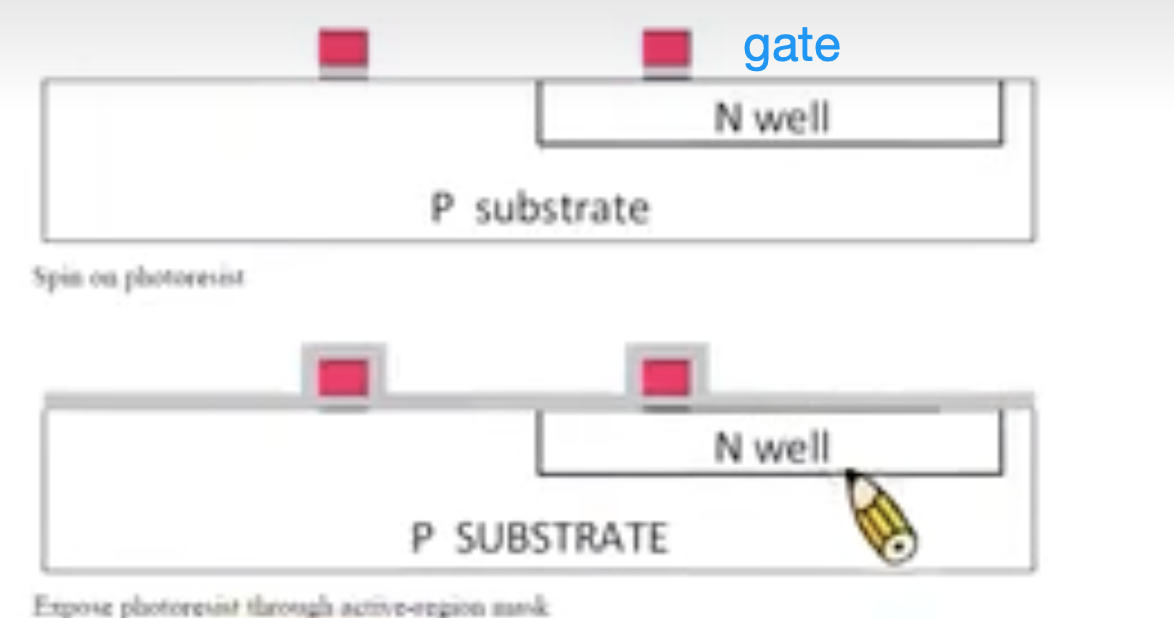

第八:这就形成了Nwell, 为我们后头的制作nmos做进一步准备

至于后面要再Nwell上面再形成Pwell 方法和上面是一样的

只是先插入了一个gate,

这样下次再注入p离子的时候,这个gate下面就自动不会填充p,保留衬底的材料N型,这样是不是p---n----p的PMOS拉

然后再进行p+注入

就形成了下面这样子的

是不是pmos做出来了

好, 大致了解工艺之后,我们就可以讲用软件进行画图了

画图用的是cadence virtuoso , 我们下篇讲解哈

有问题可以留言,希望大家点赞关注, 你们的支持是我更新的动力啊

转载请注明 半导体老登

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)