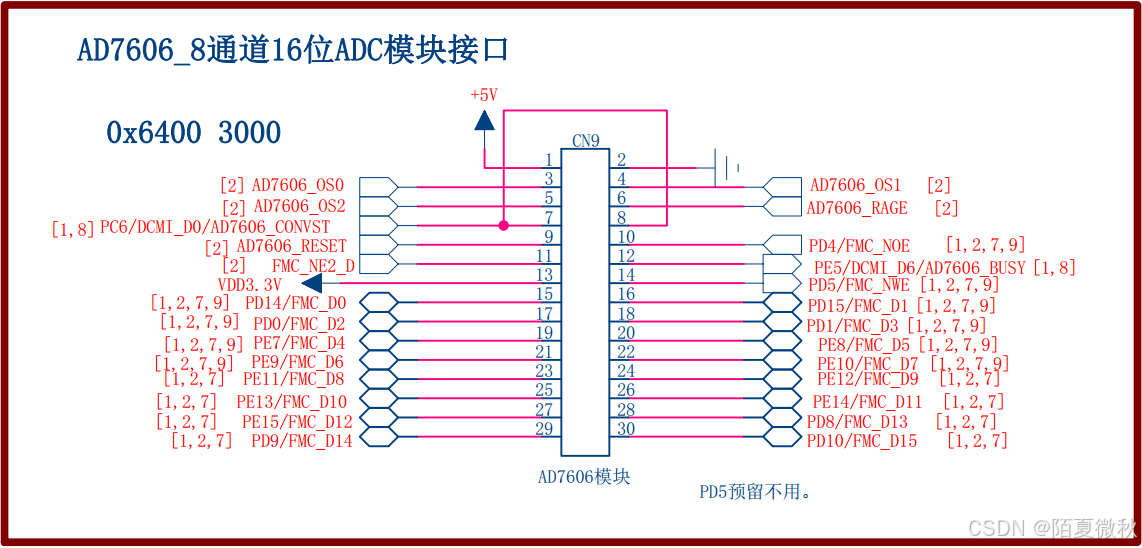

STM32单片机芯片与内部99 FMC驱动AD7606

初步对AD7606的硬件、软件和时序进行了整体介绍。

目录

1、AD7606 的 CONVST 转换时序( 转换之后读取数据)

2、AD7606 的并行驱动模式有两种时序图,一个是独立的 CS 片选和 RD 读信号时序图

一、AD7606初步介绍

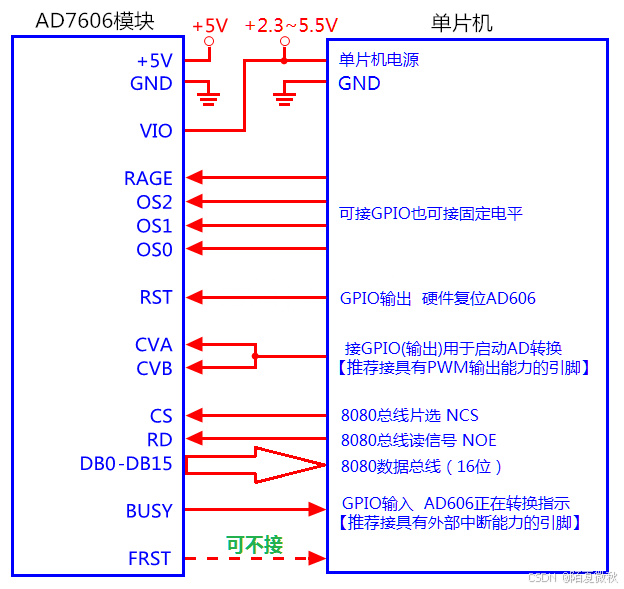

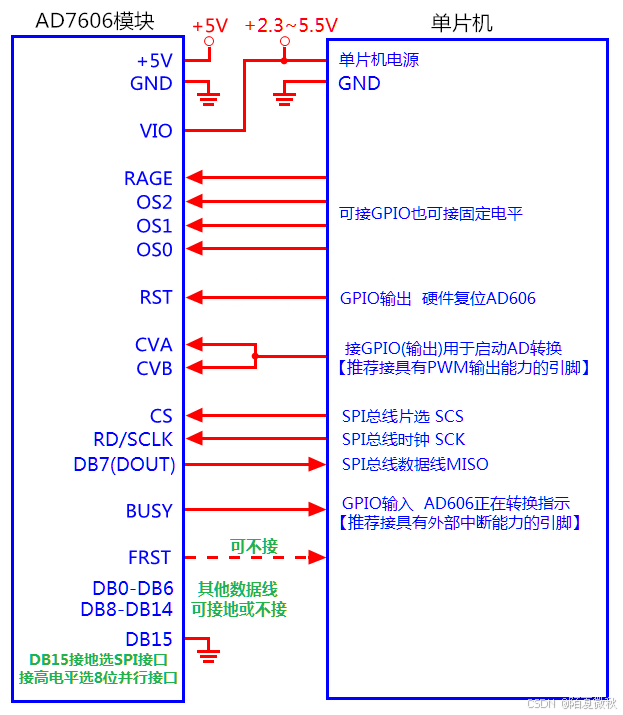

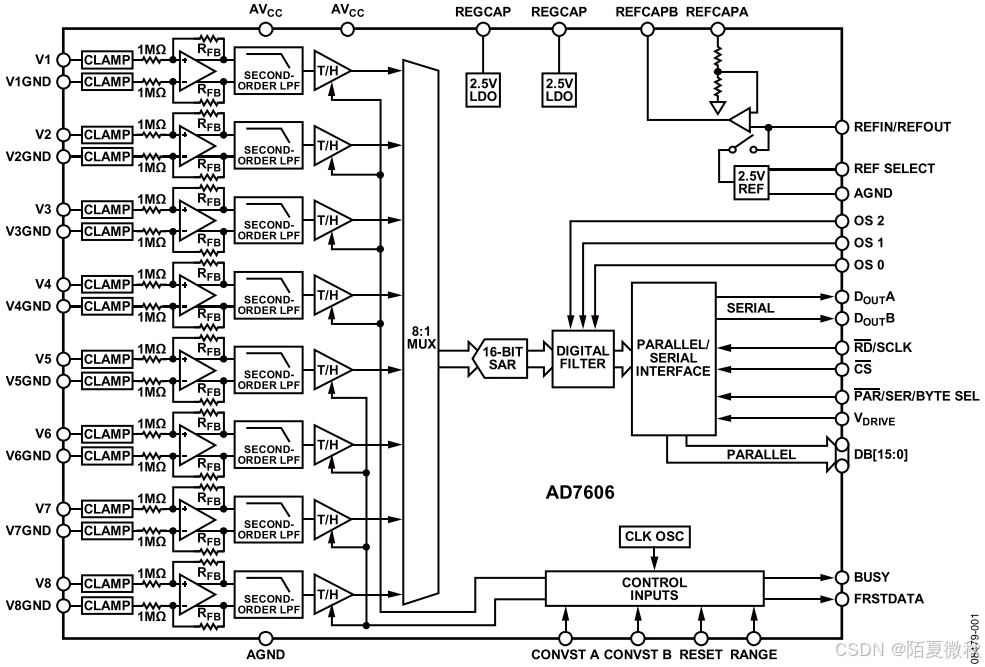

- AD7606 的配置很简单,它没有内部寄存器,量程范围和过采样参数是通过外部 IO 控制的, 采样速率由 MCU 或 DSP 提供的脉冲频率控制。

- AD7606 必须使用单 5V 供电。 而 AD7606 和 MCU 之间的通信接口电平由 VIO( VDRIVE)引脚控制。也就是说 VIO 必须接单片机的电源,可以是 3.3V 也可以是 5V(范围 2.3V – 5V)。

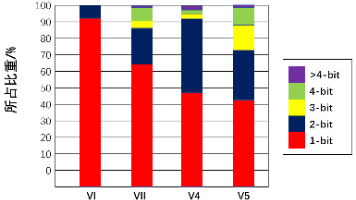

- 正确的理解过采样,比如我们设置是 1Ksps 采样率, 64 倍过采样。 意思是指每次采样, AD7606 会采样 64 次数据并求平均,相当于 AD7606 以 64Ksps 进行采样的,只是将每 64 个采样点的值做了平均,用户得到的值就是平均后的数值。 因此, 如果使用 AD7606 最高的 200Ksps 采样率, 就不可以使用过采样了。

OS2 OS1 OS2 :组合状态选择过采样模式。

- 000 表示无过采样,最大 200Ksps 采样速率。

- 001 表示 2 倍过采样, 也就是硬件内部采集 2 个样本求平均。

- 010 表示 4 倍过采样, 也就是硬件内部采集 4 个样本求平均。

- 011 表示 8 倍过采样, 也就是硬件内部采集 8 个样本求平均。

- 100 表示 16 倍过采样, 也就是硬件内部采集 16 个样本求平均。

- 101 表示 32 倍过采样, 也就是硬件内部采集 32 个样本求平均。

- 110 表示 64 倍过采样, 也就是硬件内部采集 64 个样本求平均。

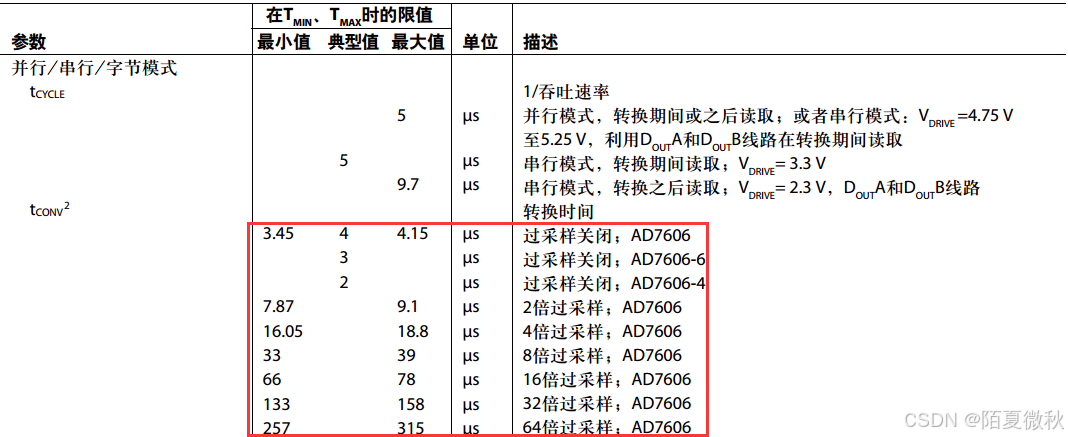

- 过采样倍率越高, ADC 转换时间越长,可得到的最大采样频率就越低。

CVA, CVB :启动 AD 转换的控制信号。

- CVA 决定 1-4 通道, CVB 决定 5-8 通道。

- 2 个信号可以错开短暂的时间。一般情况可以将 CVA, CVB 并联在一起。

RAGE:量程范围选择。

- 0 表示正负 5V;

- 1 表示正负 10V。

RD:读信号。

RST:复位信号。

BUSY:忙信号。

CS:片选信号。

FRST:第 1 个通道样本的指示信号。

VIO:通信接口电平。

DB0-DB15:数据总线。

二、AD7606时序图

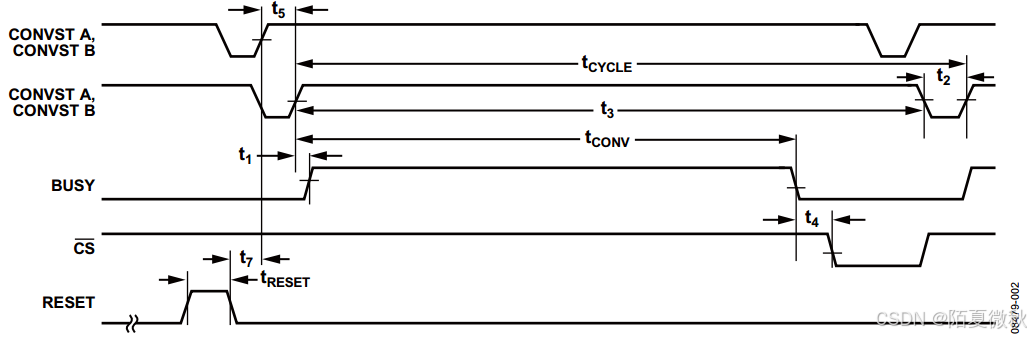

1、AD7606 的 CONVST 转换时序( 转换之后读取数据)

t5

CONVST A 和 CONVST B 上升沿之间最大允许的延迟时间。 一般我们是用一根控制线同时控制CONVST A 和 CONVST B,因此可以不用管这个时间。

tCYCLE

并行模式,转换后并读取数据的最大值是 5us,即最高支持的时钟速度是 20MHz 及其以上。

tCONV

转换时间。

t3

最短的 CONVST A/B 电平脉冲, 最小值 25ns。

t4

BUSY 下降沿到 CS 下降沿设置时间,最小值 0ns,所以可以忽略。

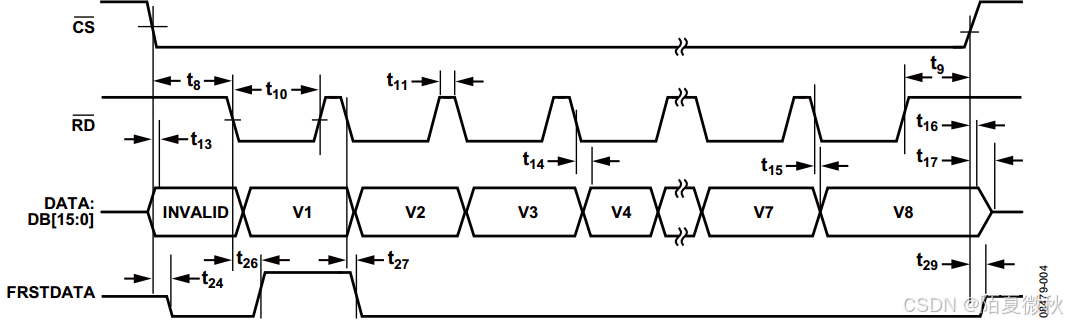

2、AD7606 的并行驱动模式有两种时序图,一个是独立的 CS 片选和 RD 读信号时序图

t8

CS 到 RD 的设置时间,最小值是 0ns,可以忽略。

t10

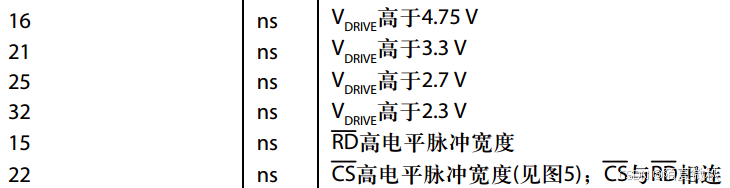

RD 读信号的低电平脉冲宽度,通信电压不同,时间不同。对于 STM32 来说, FMC 通信电平一般是3.3V, 即最小值 21ns。

t11

RD 高电平脉冲宽度,最小值 15ns。

t9

CS 到 RD 保持时间,最小值 0ns,可以忽略。

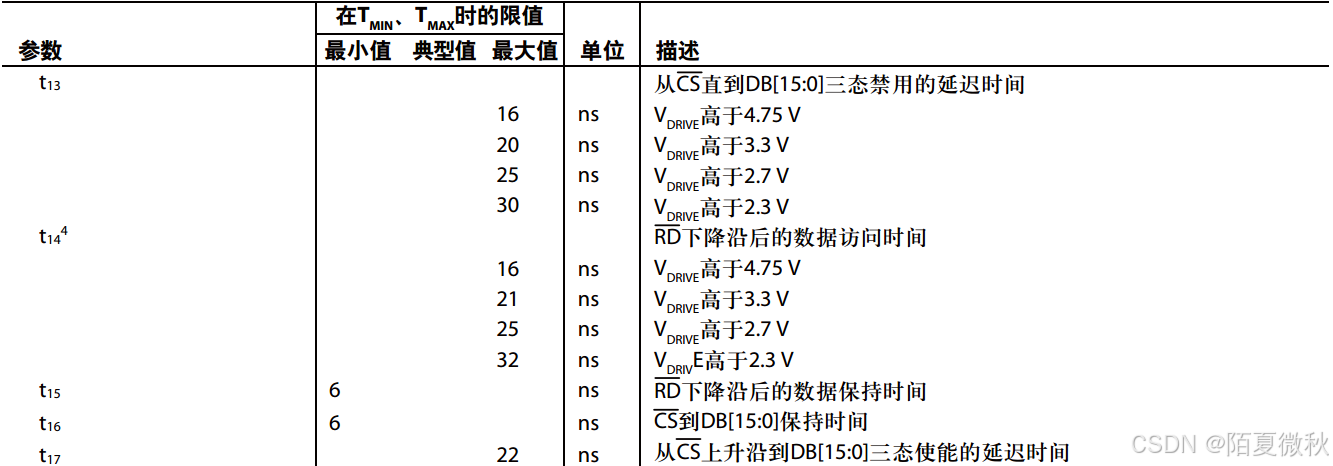

t13 到 t17

这几个参数了解下即可:

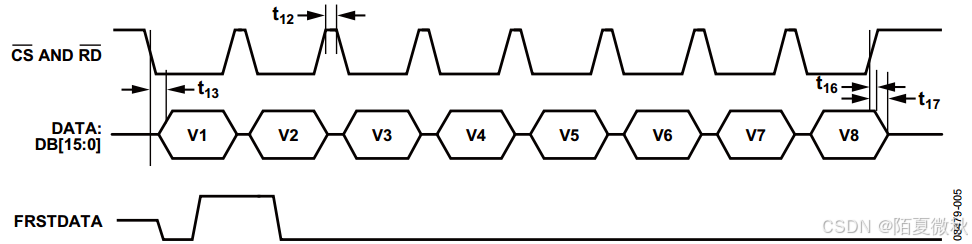

3、另一个是 CS 片选和 RD 相连的方式

t12

CS 和 RD 的高电平脉冲宽度, 最小值 22ns。

第 2 个和第 3 个时序图的主要区别是连续读取 8 路数据时, 一个 CS 信号是全程低电平,另一个 CS 信号是与 RD 信号同步,每读取完一路,拉高一次。

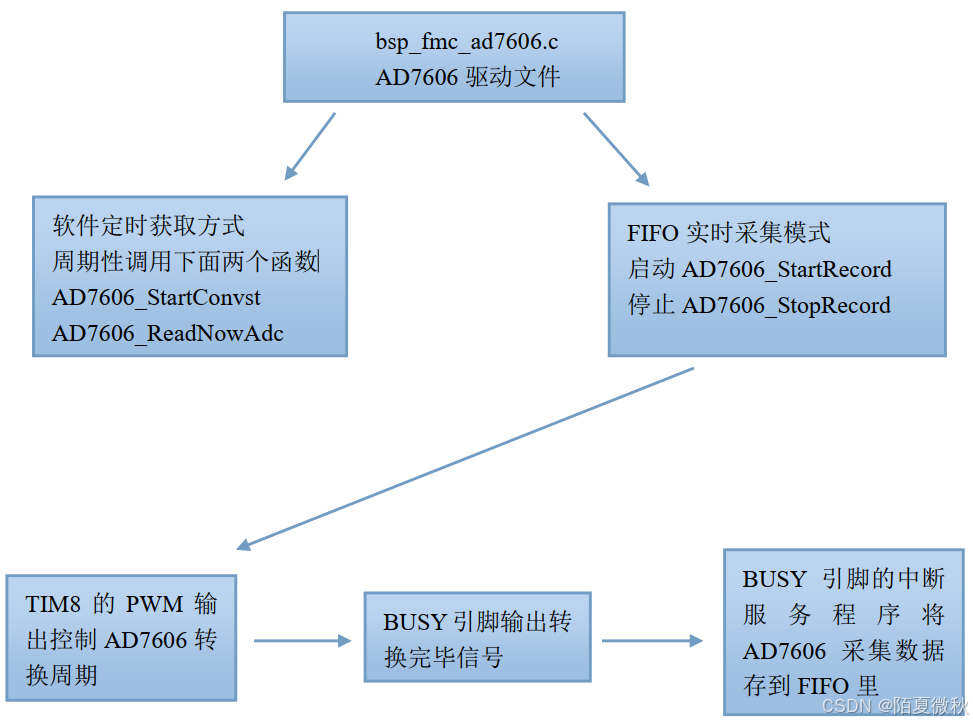

三、整体驱动思路

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)