DDR4 CTRL 系统芯片设计全流程记录 -----从需求确认到样片调试

本系列记录过去项目中关于DDR4 CTRL系统芯片设计流程,目的为了总结经验以及后续项目可以查阅,也希望可以帮助大家理解DDR CTRL相关技术,起到抛砖引玉的作用欢迎大家来讨论进步。预计按照上面思维导图中展开,具体内容包括需求整理、PHY IP选型、方案设计、代码设计、功能仿真、FPGA测试、低功耗设计、后端仿真、SI/PI仿真、样片调试等方面。涉及到方向较宽泛,基本可以遍历SOC芯片中关于DD

序言

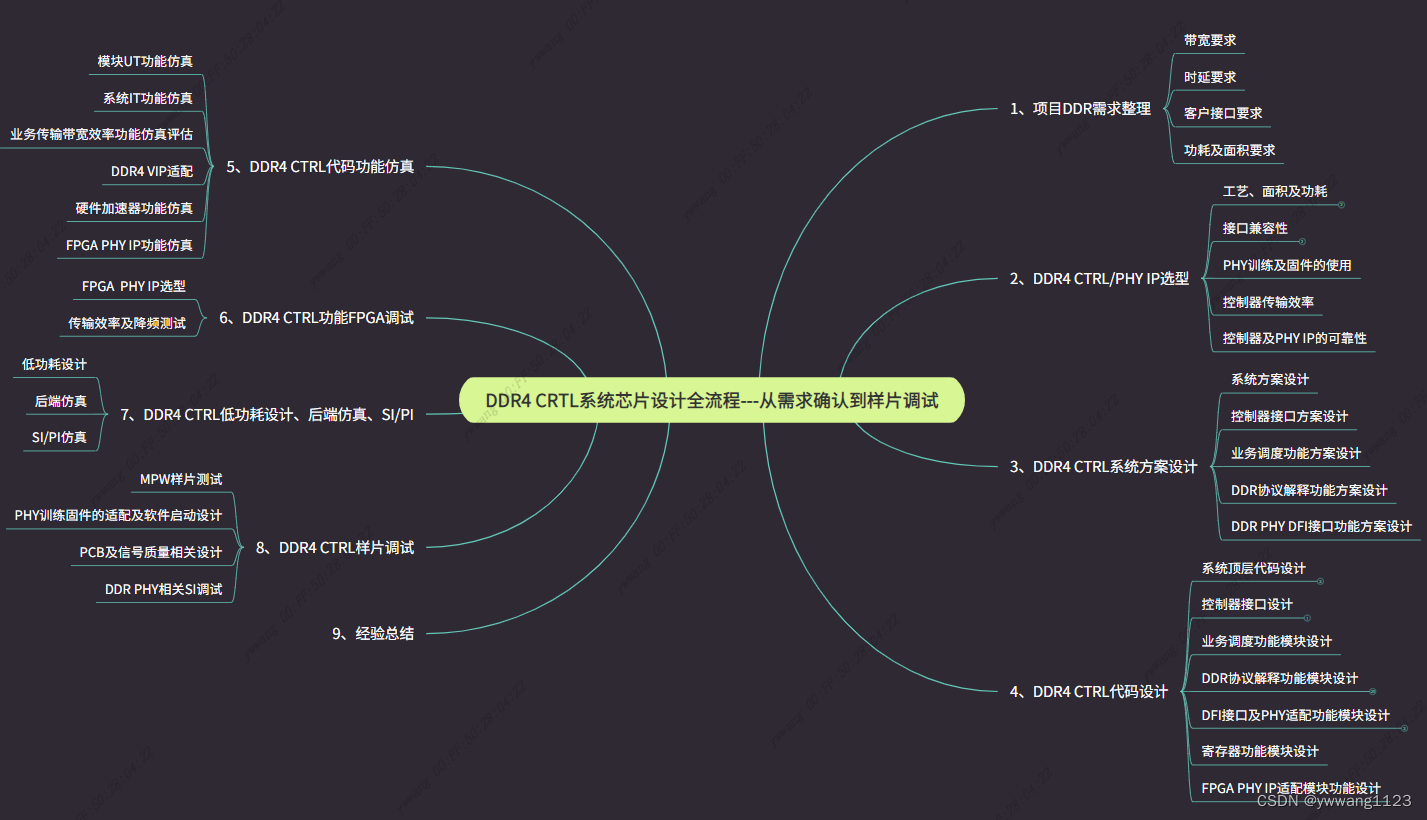

全流程思维导图

本系列记录过去项目中关于DDR4 CTRL系统芯片设计流程,目的为了总结经验以及后续项目可以查阅,也希望可以帮助大家理解DDR CTRL相关技术,起到抛砖引玉的作用欢迎大家来讨论进步。

预计按照上面思维导图中展开,具体内容包括需求整理、PHY IP选型、方案设计、代码设计、功能仿真、FPGA测试、低功耗设计、后端仿真、SI/PI仿真、样片调试等方面。涉及到方向较宽泛,基本可以遍历SOC芯片中关于DDR CTRL系统芯片设计相关技术,由于本人倾向前端逻辑设计,涉及到仿真、PCB设计、后端、软件设计并不专业只能记录下重点内容及调测过程。

全流程记录大纲:

1、项目DDR需求整理

- 带宽要求

- 时延要求

- 客户接口要求

- 功耗及面积要求

2、DDR4 CTRL/PHY IP选型

- 工艺、面积及功耗

- 接口兼容性

- PHY训练及固件的使用

- 控制器传输效率

- 控制器及PHY IP的可靠性

3、DDR4 CTRL系统方案设计

- 系统方案设计

- 控制器接口方案设计

- 业务调度功能方案设计

- DDR协议解释功能方案设计

- DDR PHY DFI接口功能方案设计

4、DDR4 CTRL代码设计

- 系统顶层代码设计

- 控制器接口设计

- 业务调度功能模块设计

- DDR协议解释功能模块设计

- DFI接口及PHY适配功能模块设计

- 寄存器功能模块设计

- FPGA PHY IP适配模块功能设计

5、DDR4 CTRL代码功能仿真

- 模块UT功能仿真

- 系统IT功能仿真

- 业务传输带宽效率功能仿真评估

- DDR4 VIP适配

- 硬件加速器功能仿真

- FPGA PHY IP功能仿真

6、DDR4 CTRL功能FPGA调试

- FPGA PHY IP选型

- 传输效率及降频测试

7、DDR4 CTRL低功耗设计、后端仿真、SI/PI

- 低功耗设计

- 后端仿真

- SI/PI仿真

8、DDR4 CTRL样片调试

- MPW样片测试

- PHY训练固件的适配及软件启动设计

- PCB及信号质量相关设计

- DDR PHY相关SI调试

9、经验总结

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)