从芯片硬件的角度理解海思的VPSS

从芯片硬件上理解海思的VPSS模块。以hi3559av100为例。首先芯片的逻辑框图中VPSS处于image subsystem:VPSS分为VPSS0和VPSS1两部分,有独立的寄存器地址空间:且两个VPSS的时钟独立,更具不同的场景配置使用哪一个VPSS以及使用的时钟频率。时钟频率的配置寄存器:频率选择寄存器;在线或者离线频率选择:...

·

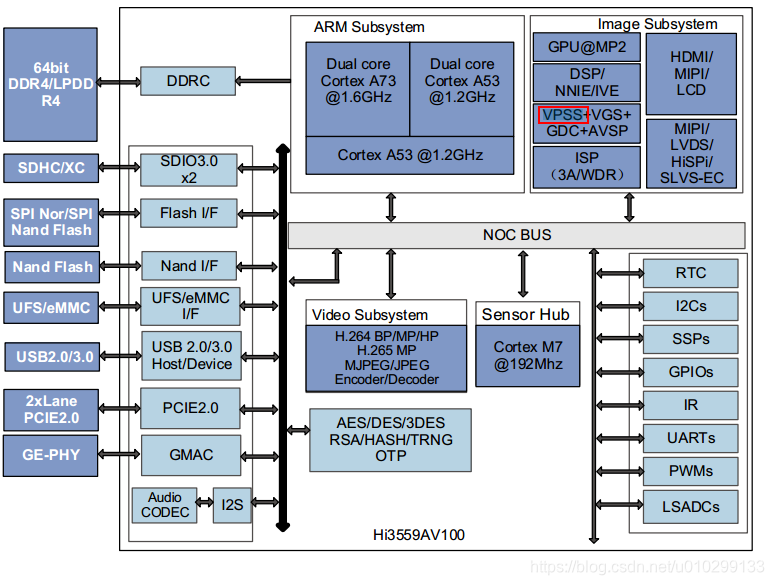

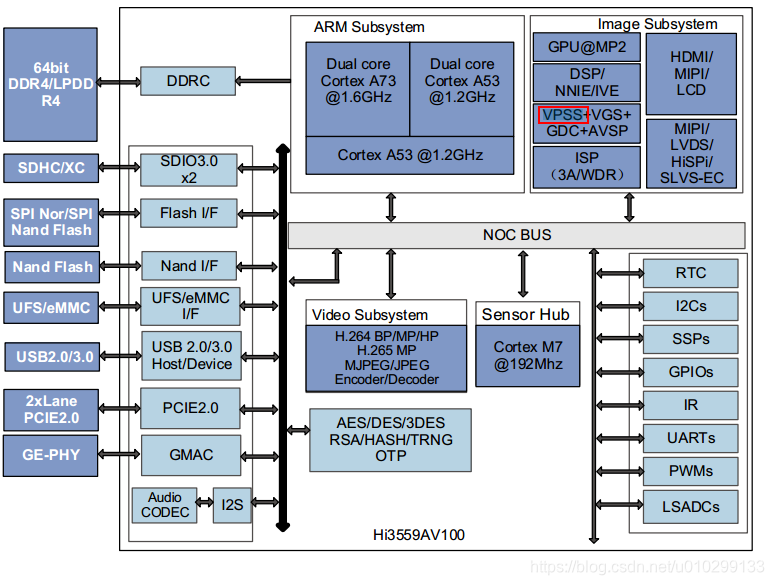

从芯片硬件上理解海思的VPSS模块。以hi3559av100为例。

首先芯片的逻辑框图中VPSS处于image subsystem:

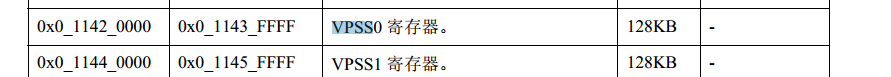

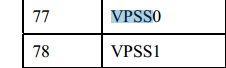

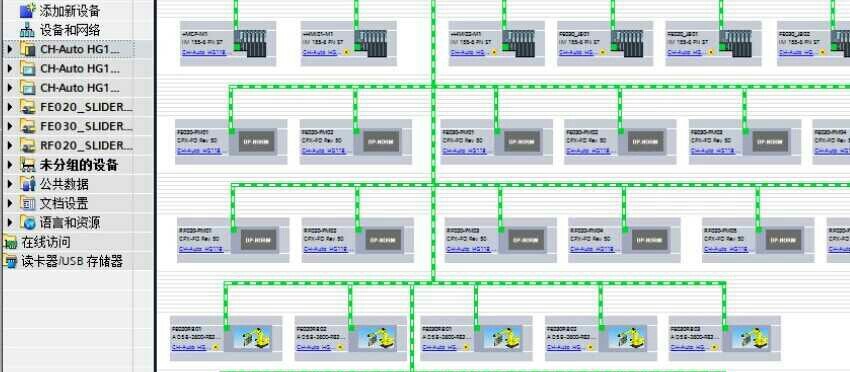

VPSS分为VPSS0和VPSS1两部分,有独立的寄存器地址空间:

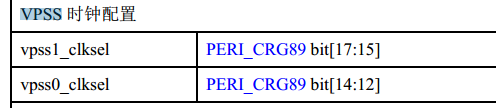

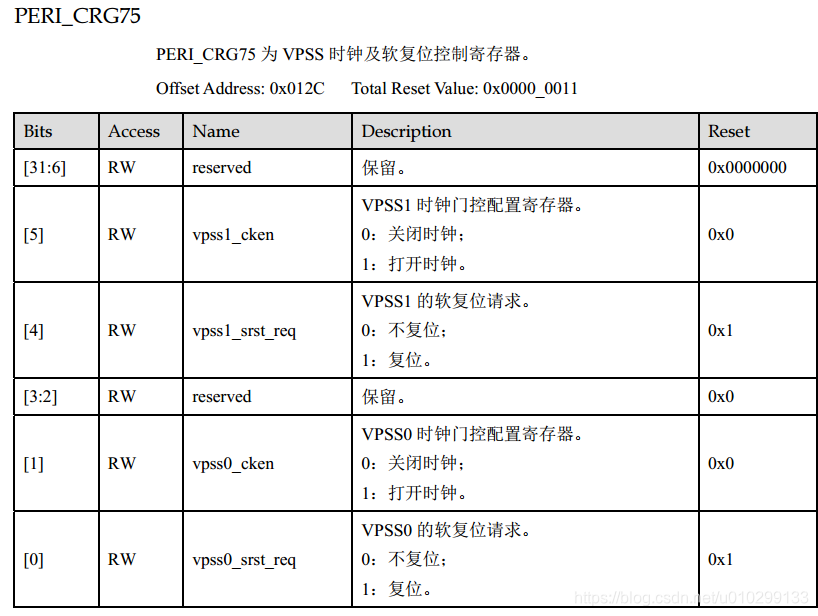

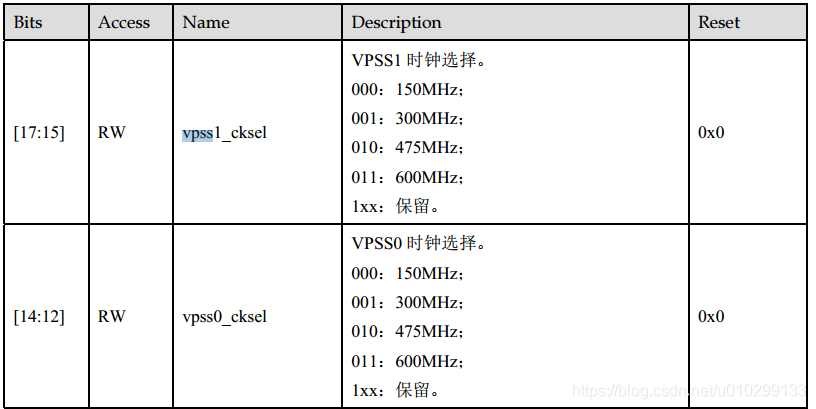

且两个VPSS的时钟独立,更具不同的场景配置使用哪一个VPSS以及使用的时钟频率。

时钟频率的配置寄存器:

![]()

频率选择寄存器;

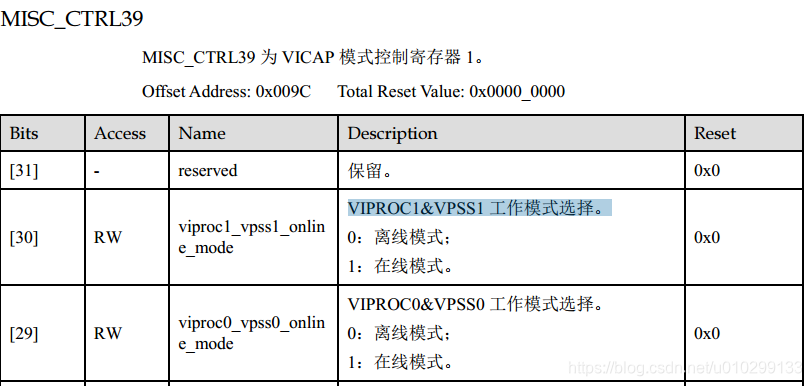

在线或者离线频率选择:

中断号:

VIPROC和VPSS的工作模式选择:

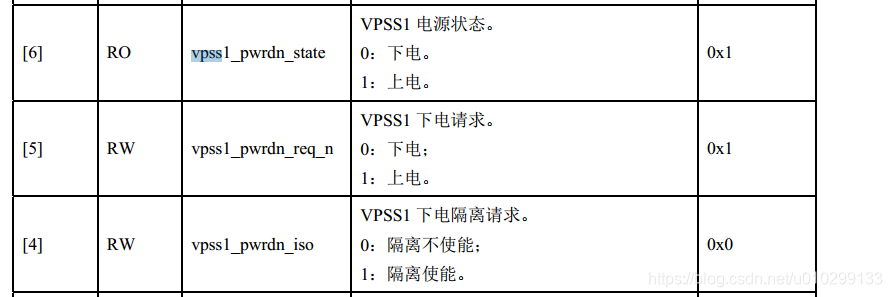

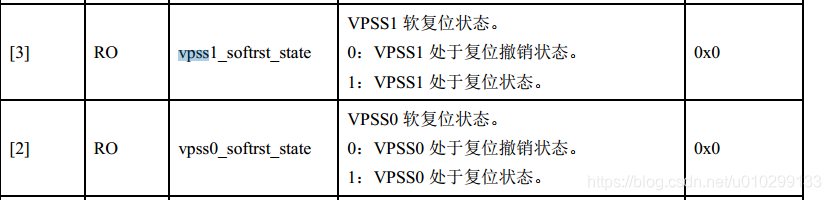

VPSS的电源管理:

寄存器:MISC_CTRL44为模块电源控制寄存器。

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)