探索未来计算:PicoRV32 — 一款精巧的RISC-V CPU

探索未来计算:PicoRV32 — 一款精巧的RISC-V CPU项目地址:https://gitcode.com/gh_mirrors/pic/picorv32在现代电子设计中,高效的处理器核心是不可或缺的。今天,我们向您推荐一个名为PicoRV32的开源项目,它是一款高度优化的RISC-V CPU,专为那些追求小巧高效解决方案的工程师和爱好者们打造。项目简介PicoRV32是基于RIS...

探索未来计算:PicoRV32 — 一款精巧的RISC-V CPU

项目地址:https://gitcode.com/gh_mirrors/pic/picorv32

在现代电子设计中,高效的处理器核心是不可或缺的。今天,我们向您推荐一个名为PicoRV32的开源项目,它是一款高度优化的RISC-V CPU,专为那些追求小巧高效解决方案的工程师和爱好者们打造。

项目简介

PicoRV32是基于RISC-V RV32IMC指令集的CPU核心,可配置为多种变体,包括RV32E、RV32I、RV32IC、RV32IM或RV32IMC。此外,该CPU还带有内置中断控制器,使得它在处理实时任务时更为灵活。该项目采用ISC许可,意味着它是免费且开放源代码的,允许在各种项目中自由使用。

项目技术分析

PicoRV32的设计亮点在于其小体积和高速度。在Xilinx 7系列FPGA上,它可以实现750到2000个LUTs(逻辑单元)的规模,并达到250至450MHz的运行频率。这种高性能特性使其非常适合在现有设计中作为辅助处理器,无需跨时钟域操作。

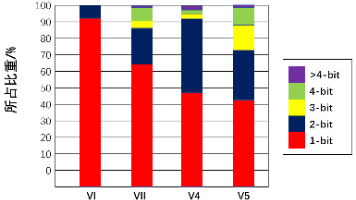

核心有双端口和单端口两种寄存器文件实现方式,前者提供更好的性能,而后者则有助于减小核心大小。通过禁用一些高级功能,如x16-x31寄存器、RDCYCLE等指令,可以进一步降低其尺寸,以适应更紧凑的应用场景。

应用场景

PicoRV32广泛适用于需要小型、高效处理器的FPGA和ASIC设计。它可以在不干扰系统其他部分的情况下轻松集成,由于其高fmax,即使在较低的频率下运行,也能保证充足的时序余量,避免影响整体设计的时序收敛。

除了基本的内存接口,PicoRV32还提供了AXI4-Lite主控接口和Wishbone主控接口的选择,这使它能够无缝对接各类标准系统总线,增强了其实用性和灵活性。

项目特点

- 灵活性:支持多种配置,包括RV32E到RV32IMC的各种变体。

- 高效性:在有限的资源下实现了较高的运行速度和良好的性能。

- 兼容性:提供AXI4-Lite和Wishbone接口,方便与其他硬件组件协同工作。

- 可扩展性:支持自定义指令和Pico Co-Processor Interface(PCPI),可用于实现特定功能的协处理器。

无论您是在进行嵌入式开发、学术研究,还是单纯对RISC-V感兴趣,PicoRV32都是值得一试的优秀项目。立即加入社区,探索这个强大的微处理器能为您带来哪些创新可能吧!

git clone https://github.com/YosysHQ/picorv32.git

cd picorv32

make test

只需几行命令,即可开始您的PicoRV32之旅!

picorv32 PicoRV32 - A Size-Optimized RISC-V CPU

DAMO开发者矩阵,由阿里巴巴达摩院和中国互联网协会联合发起,致力于探讨最前沿的技术趋势与应用成果,搭建高质量的交流与分享平台,推动技术创新与产业应用链接,围绕“人工智能与新型计算”构建开放共享的开发者生态。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)